## The Practitioner's Cookbook for Good Parallel Performance on Multi- and Many-Core Systems

Georg Hager, Jan Treibig, Gerhard Wellein Erlangen Regional Computing Center (RRZE) and Department of Computer Science University of Erlangen-Nuremberg

SC13 full-day tutorial June 18, 2013 Denver, CO

#### Agenda

| зНа                |   | Preliminaries                                                      | 08:30 |

|--------------------|---|--------------------------------------------------------------------|-------|

| U                  |   | Introduction to multicore architecture                             |       |

| Ň                  |   | Cores, caches, chips, sockets, ccNUMA, SIMD                        | 10:00 |

| 0                  |   | LIKWID tools                                                       | 10:30 |

|                    |   | Microbenchmarking for architectural exploration                    |       |

| 5                  |   | Streaming benchmarks: throughput mode                              |       |

|                    |   | Streaming benchmarks: work sharing                                 |       |

|                    |   | Roadblocks for scalability: Saturation effects and OpenMP overhead | 12:00 |

|                    |   | Lunch break                                                        |       |

| GW JT GHA JT GW GH | • | Node-level performance modeling                                    | 13:30 |

|                    |   | The Roofline Model                                                 |       |

|                    |   | Case study: 3D Jacobi solver and model-guided optimization         | 15:00 |

| GW JT GHa JT GW    |   | Optimal resource utilization                                       | 15:30 |

|                    |   | SIMD parallelism                                                   |       |

|                    |   | ccNUMA                                                             |       |

|                    |   | <ul> <li>Simultaneous multi-threading (SMT)</li> </ul>             | 17:00 |

| GHa                |   | Optional: The ECM multicore performance model                      |       |

|                    |   |                                                                    |       |

#### Agenda

#### Preliminaries

- Introduction to multicore architecture

- Cores, caches, chips, sockets, ccNUMA, SIMD

- LIKWID tools

- Microbenchmarking for architectural exploration

- Streaming benchmarks: throughput mode

- Streaming benchmarks: work sharing

- Roadblocks for scalability: Saturation effects and OpenMP overhead

- Lunch break

- Node-level performance modeling

- The Roofline Model

- Case study: 3D Jacobi solver and model-guided optimization

- Optimal resource utilization

- SIMD parallelism

- ccNUMA

- Simultaneous multi-threading (SMT)

- Optional: The ECM multicore performance model

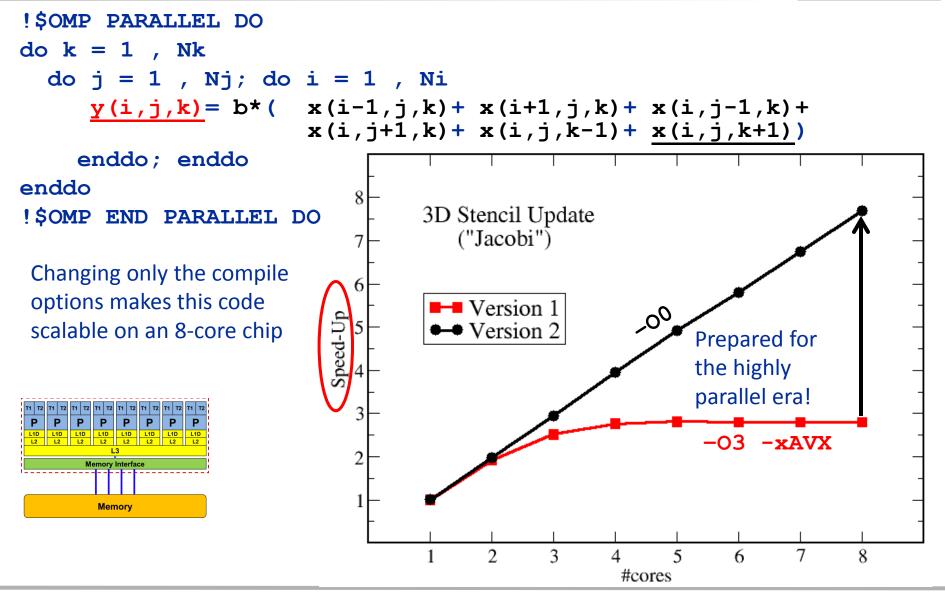

# Prelude: Scalability 4 the win!

#### Lore 1

# In a world of highly parallel computer architectures only highly scalable codes will survive

#### Lore 2

# Single core performance no longer matters since we have so many of them and use scalable codes

(c) RRZE 2013

#### Scalability Myth: Code scalability is the key issue

(c) RRZE 2013

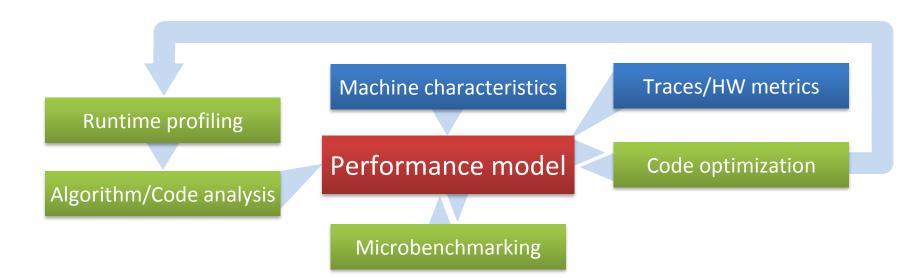

- Do I understand the performance behavior of my code?

- Does the performance match a model I have made?

- What is the optimal performance for my code on a given machine?

- High Performance Computing == Computing at the bottleneck

- Can I change my code so that the "optimal performance" gets higher?

- Circumventing/ameliorating the impact of the bottleneck

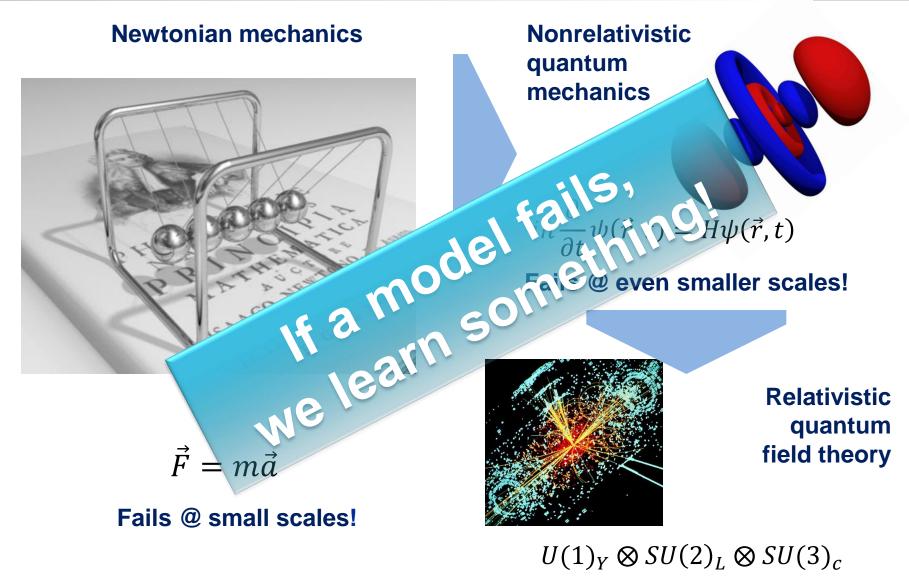

- My model does not work what's wrong?

- This is the good case, because you learn something

- Performance monitoring / microbenchmarking may help clear up the situation

# The Performance Engineering (PE) process:

The performance model is the central component – if the model fails to predict the measurement, you learn something!

The analysis has to be done for every loop / basic block!

- White Box Performance Model

- Simple enough to do on paper

- Catching the important influences

#### How model-building works: Physics

# There is no alternative to knowing what is going on between your code and the hardware

#### Without performance modeling, optimizing code is like stumbling in the dark

#### Agenda

- Preliminaries

- Introduction to multicore architecture

- Cores, caches, chips, sockets, ccNUMA, SIMD

- LIKWID tools

- Microbenchmarking for architectural exploration

- Streaming benchmarks: throughput mode

- Streaming benchmarks: work sharing

- Roadblocks for scalability: Saturation effects and OpenMP overhead

- Lunch break

- Node-level performance modeling

- The Roofline Model

- Case study: 3D Jacobi solver and model-guided optimization

- Optimal resource utilization

- SIMD parallelism

- ccNUMA

- Simultaneous multi-threading (SMT)

- Optional: The ECM multicore performance model

# Introduction: Modern node architecture

Multi- and manycore chips and nodes A glance at basic core features Caches and data transfers through the memory hierarchy Memory organization Accelerators Programming models

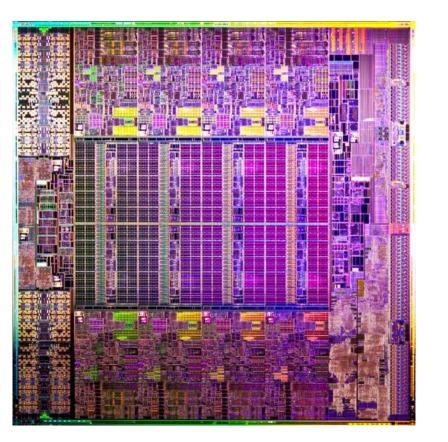

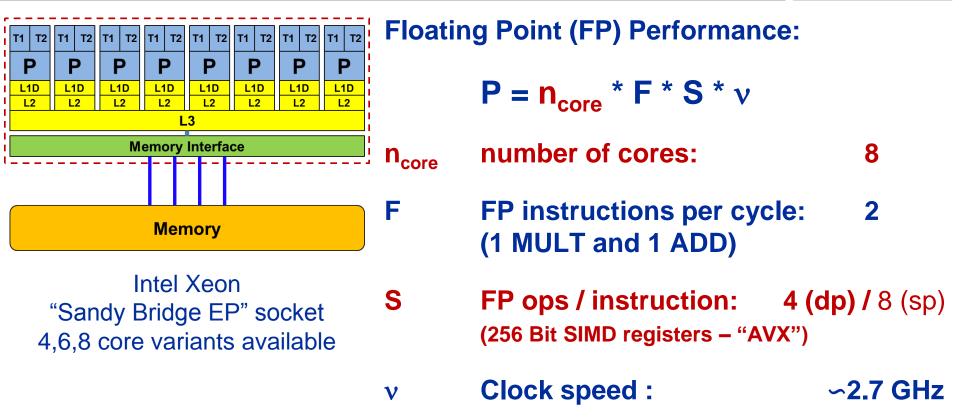

- Xeon 2600 "Sandy Bridge EP": 8 cores running at 2.7 GHz (max 3.2 GHz)

- Simultaneous Multithreading

→ reports as 16-way chip

- 2.3 Billion Transistors / 32 nm

- Die size: 435 mm<sup>2</sup>

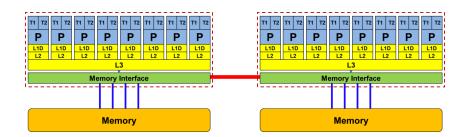

#### 2-socket server

#### • (Almost) the same basic design in all modern systems

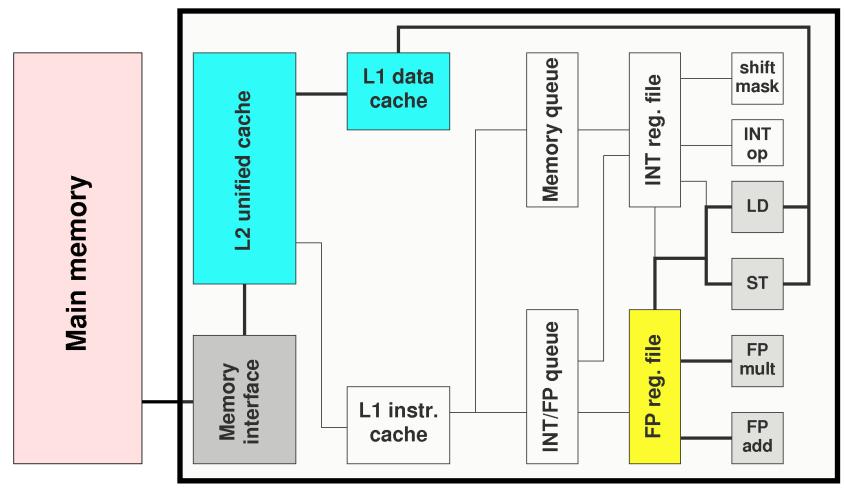

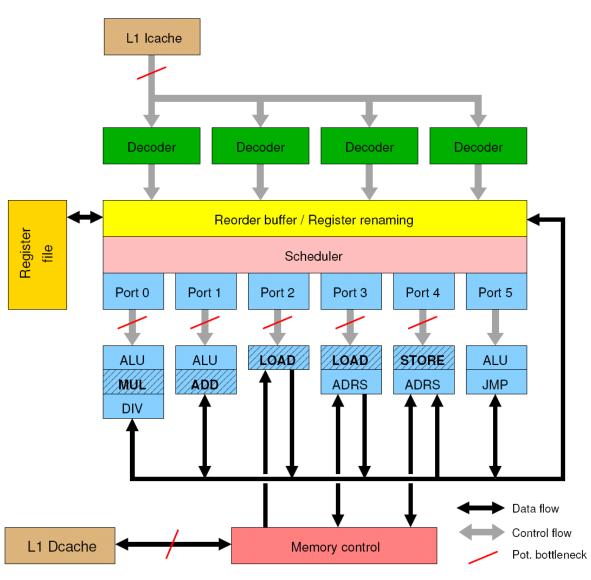

Not shown: most of the control unit, e.g. instruction fetch/decode, branch prediction,...

#### (c) RRZE 2013

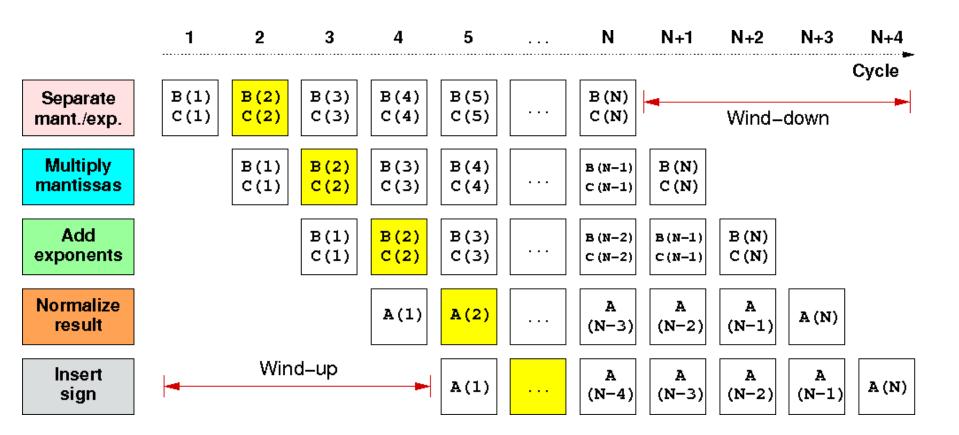

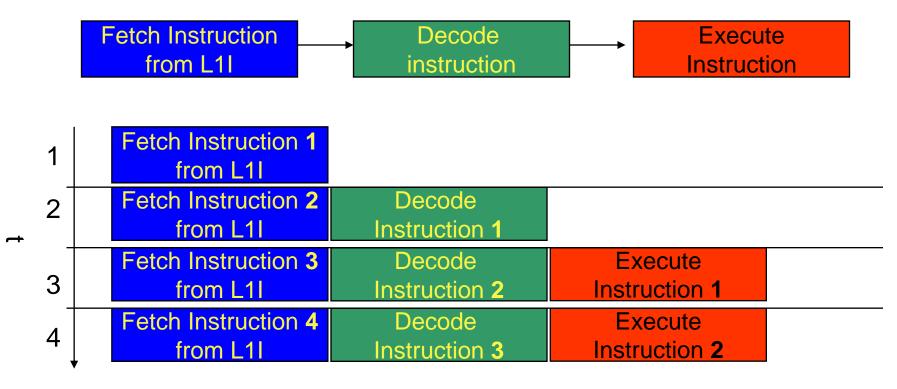

#### Idea:

- Split complex instruction into several simple / fast steps (stages)

- Each step takes the same amount of time, e.g. a single cycle

- Execute different steps on different instructions at the same time (in parallel)

#### Allows for shorter cycle times (simpler logic circuits), e.g.:

- floating point multiplication takes 5 cycles, but

- processor can work on 5 different multiplications simultaneously

- one result at each cycle after the pipeline is full

#### Drawback:

- Pipeline must be filled startup times (#Instructions >> pipeline steps)

- Efficient use of pipelines requires large number of independent instructions → instruction level parallelism

- Requires complex instruction scheduling by compiler/hardware softwarepipelining / out-of-order

#### Pipelining is widely used in modern computer architectures

First result is available after 5 cycles (=latency of pipeline)! Wind-up/-down phases: Empty pipeline stages

Besides arithmetic & functional unit, instruction execution itself is pipelined also, e.g.: one instruction performs at least 3 steps:

- Branches can stall this pipeline! (Speculative Execution, Predication)

- Each unit is pipelined itself (e.g., Execute = Multiply Pipeline)

#### **Superscalar Processors – Instruction Level Parallelism**

Multiple units enable use of Instruction Level Parallelism (ILP): Instruction stream is "parallelized" on the fly

- Issuing m concurrent instructions per cycle: m-way superscalar

- Modern processors are 3- to 6-way superscalar & can perform 2 or 4 floating point operations per cycles

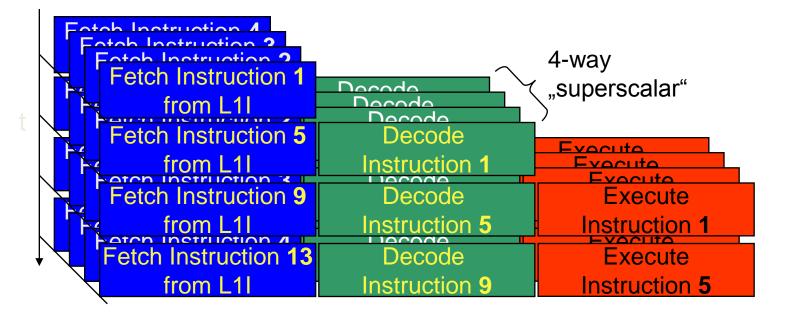

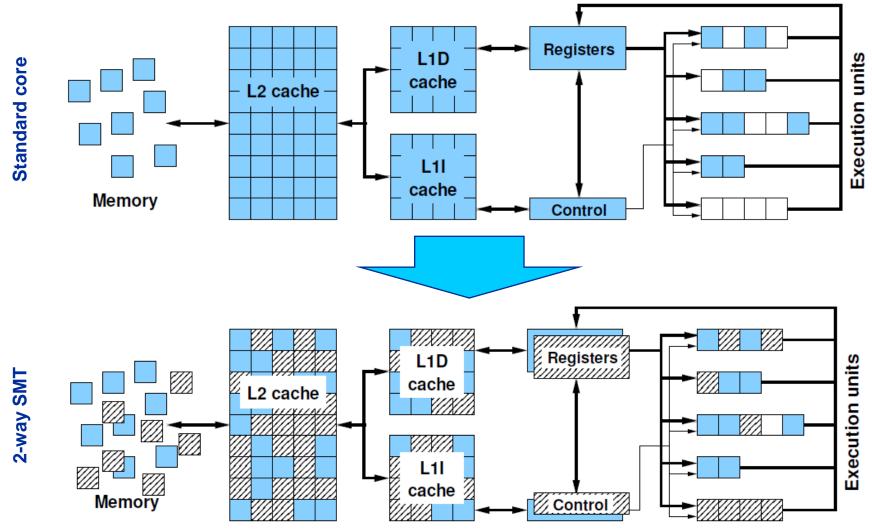

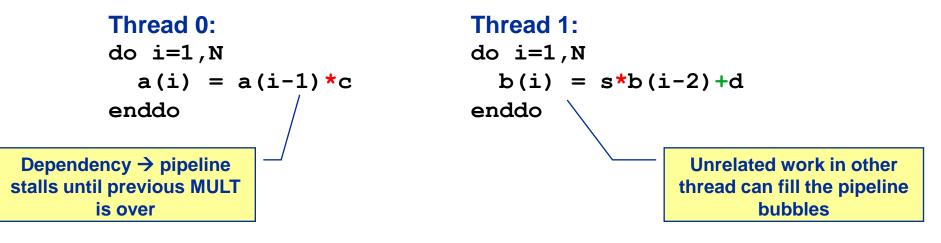

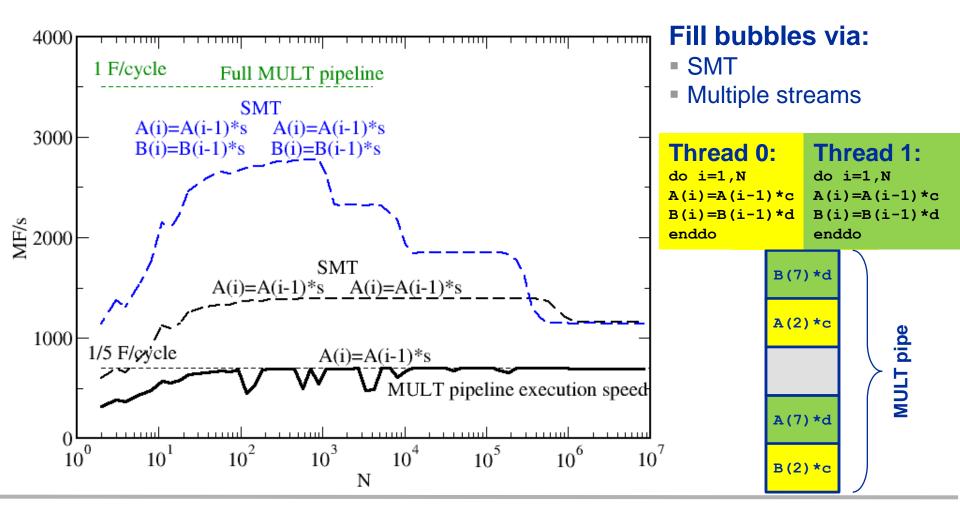

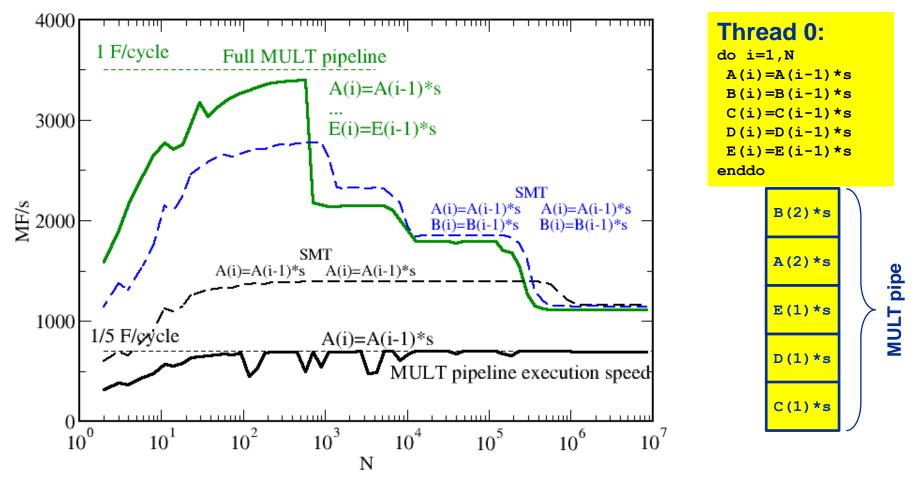

#### SMT principle (2-way example):

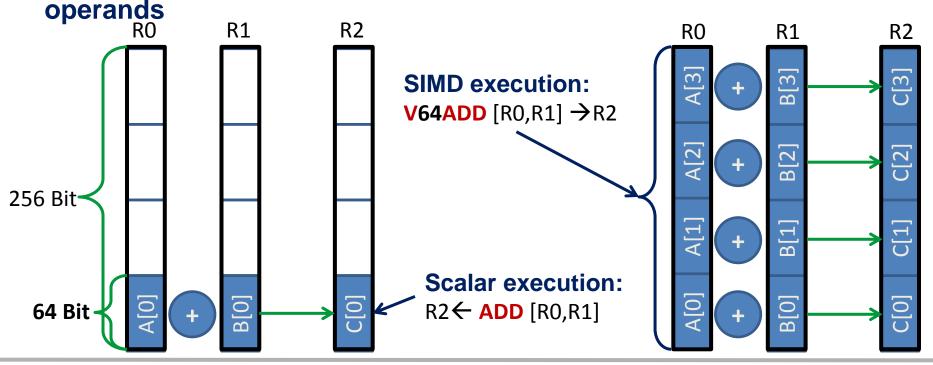

- x86 SIMD instruction sets:

- SSE: register width = 128 Bit  $\rightarrow$  2 double precision floating point operands

- AVX: register width = 256 Bit  $\rightarrow$  4 double precision floating point operands

- Adding two registers holding double precision floating point

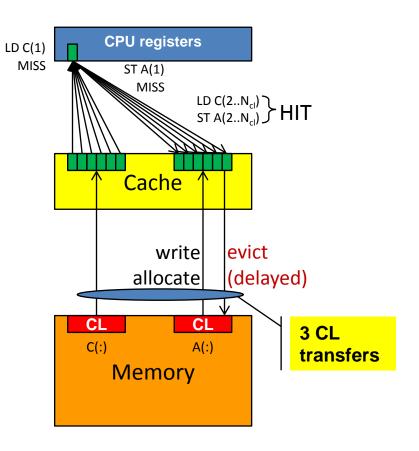

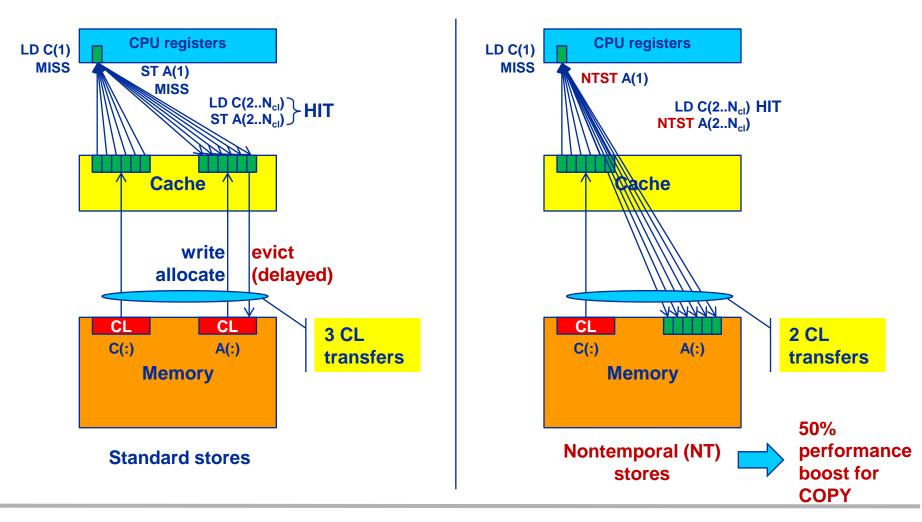

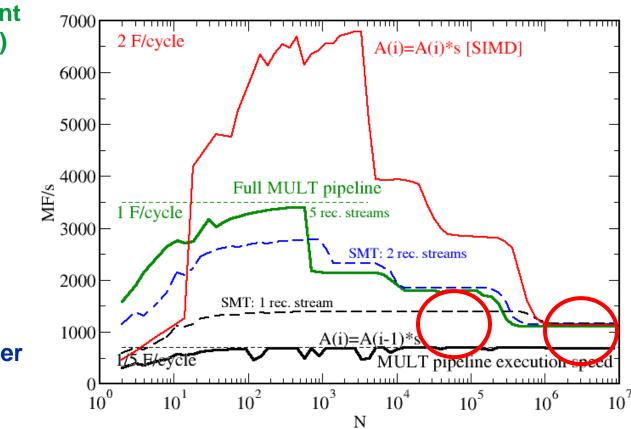

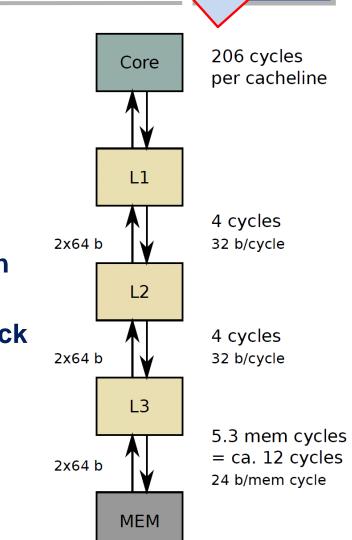

- How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- MISS: Load or store instruction does not find the data in a cache level

CL transfer required

Example: Array copy A(:)=C(:)

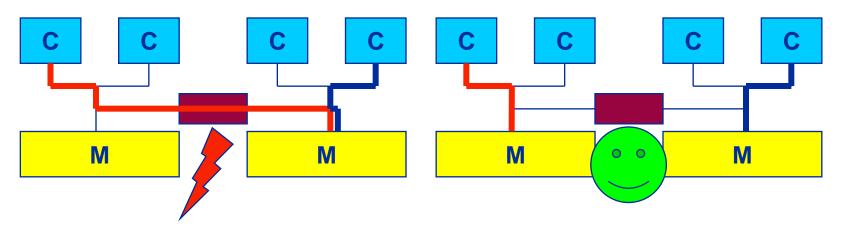

Basic architecture of commodity compute cluster nodes

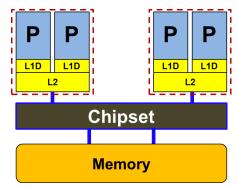

#### Yesterday (2006): Dual-socket Intel "Core2" node:

Uniform Memory Architecture (UMA)

Flat memory ; symmetric MPs

But: system "anisotropy"

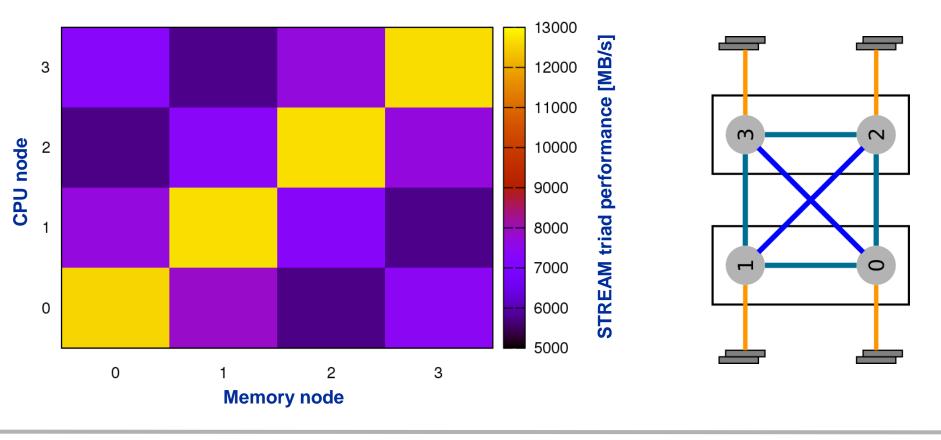

#### Today: Dual-socket Intel (Westmere,...) node:

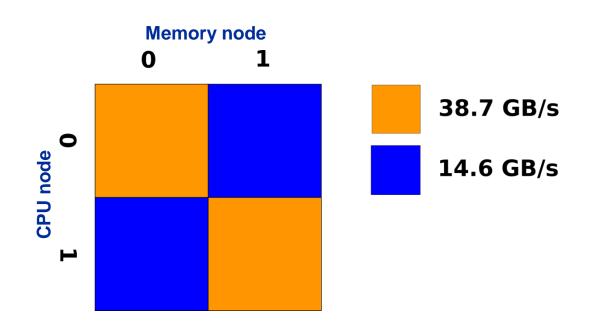

Cache-coherent Non-Uniform Memory Architecture (ccNUMA)

HT / QPI provide scalable bandwidth at the price of ccNUMA architectures: *Where does my data finally end up?*

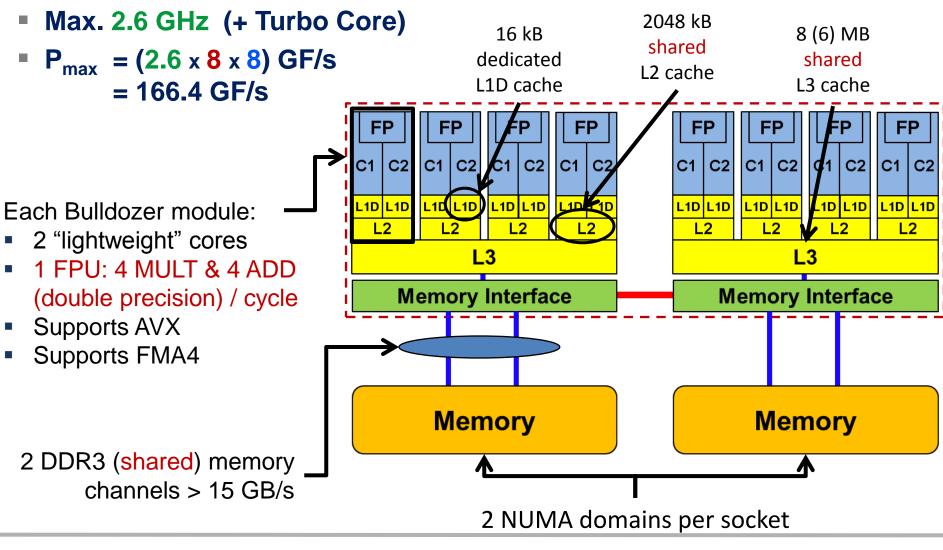

#### On AMD it is even more complicated $\rightarrow$ ccNUMA within a socket!

Up to 16 cores (8 Bulldozer modules) in a single socket

(c) RRZE 2013

TOP500 rank 1 (mid-90s) **P = 173 GF/s (dp) /** 346 GF/s (sp)

But: P=5.4 GF/s (dp) for serial, non-SIMD code

# Interlude: A glance at current accelerator technology

## **NVIDIA Kepler GK110 Block Diagram**

#### Architecture

- 7.1B Transistors

- 15 "SMX" units

- 192 (SP) "cores" each

- > 1 TFLOP DP peak

- 1.5 MB L2 Cache

- 384-bit GDDR5

- PCI Express Gen3

- 3:1 SP:DP performance

|                                     |  | LD/ST SFU | J Core | Core Co | re DP Un                      | it Core | Core Cor | DP Unit                          |

|-------------------------------------|--|-----------|--------|---------|-------------------------------|---------|----------|----------------------------------|

|                                     |  |           |        |         | 0 Host Interface<br>ad Engine |         |          |                                  |

| Memory Controller Memory Controller |  |           |        |         |                               |         |          | Memory Controller Memory Control |

| Siler Memory Controller             |  |           |        |         |                               |         |          | ler Mennory Contro               |

© NVIDIA Corp. Used with permission.

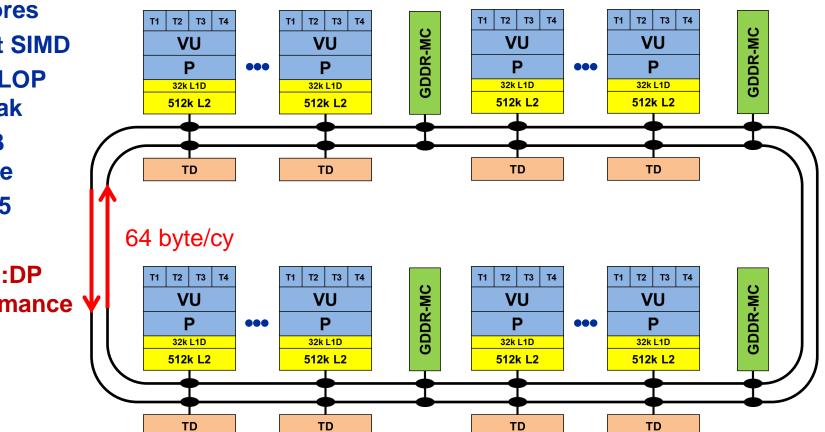

#### Intel Xeon Phi block diagram

#### Architecture

- 3B Transistors

- 60+ cores

- 512 bit SIMD

- ≈ 1 TFLOP DP peak

- 0.5 MB L2/core

- GDDR5

2:1 SP:DP performance

#### **Comparing accelerators**

#### Intel Xeon Phi

- 60+ IA32 cores each with 512 Bit SIMD FMA unit → 480/960 SIMD DP/SP tracks

- Clock Speed: ~1000 MHz

- Transistor count: ~3 B (22nm)

- Power consumption: ~250 W

- Peak Performance (DP): ~ 1 TF/s

- Memory BW: ~250 GB/s (GDDR5)

- Threads to execute: 60-240+

Programming: Fortran/C/C++ +OpenMP + SIMD

#### NVIDIA Kepler K20

15 SMX units each with 192 "cores" → 960/2880 DP/SP "cores"

- Clock Speed: ~700 MHz

- Transistor count: 7.1 B (28nm)

- Power consumption: ~250 W

- Peak Performance (DP): ~ 1.3 TF/s

- Memory BW: ~ 250 GB/s (GDDR5)

- Threads to execute: 10,000+

- Programming: CUDA, OpenCL, (OpenACC)

| Top7: "Stampede" at Texas Center<br>for Advanced Computing | TOP500<br>rankings<br>Nov 2012 | <ul> <li>Top1: "Titan" at Oak Ridge National<br/>Laboratory</li> </ul> |

|------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|

|------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|

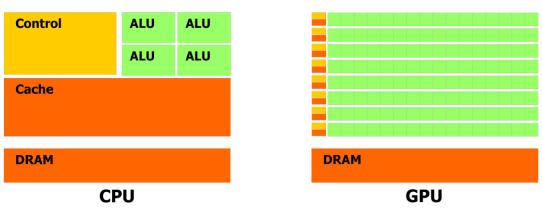

#### **Trading single thread performance for parallelism:** *GPGPUs vs. CPUs*

#### GPU vs. CPU light speed estimate:

- 1. Compute bound: 2-10x

- 2. Memory Bandwidth: 1-5x

|                                                                                   | -                                        |                                                |                           |  |  |

|-----------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------|---------------------------|--|--|

|                                                                                   | Intel Core i5 – 2500<br>("Sandy Bridge") | Intel Xeon E5-2680 DP<br>node ("Sandy Bridge") | NVIDIA K20x<br>("Kepler") |  |  |

| Cores@Clock                                                                       | 4 @ 3.3 GHz                              | 2 x 8 @ 2.7 GHz                                | 2880 @ 0.7 GHz            |  |  |

| Performance+/core                                                                 | 52.8 GFlop/s                             | 43.2 GFlop/s                                   | 1.4 GFlop/s               |  |  |

| Threads@STREAM                                                                    | <4                                       | <16                                            | >8000?                    |  |  |

| Total performance+                                                                | 210 GFlop/s                              | 691 GFlop/s                                    | 4,000 GFlop/s             |  |  |

| Stream BW                                                                         | 18 GB/s                                  | 2 x 40 GB/s                                    | 168 GB/s (ECC=1)          |  |  |

| Transistors / TDP                                                                 | 1 Billion* / 95 W                        | 2 x (2.27 Billion/130W)                        | 7.1 Billion/250W          |  |  |

| + Single Precision * Includes on-chip GPU and PCI-Express Complete compute device |                                          |                                                |                           |  |  |

(c) RRZE 2013

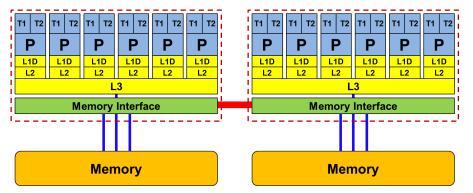

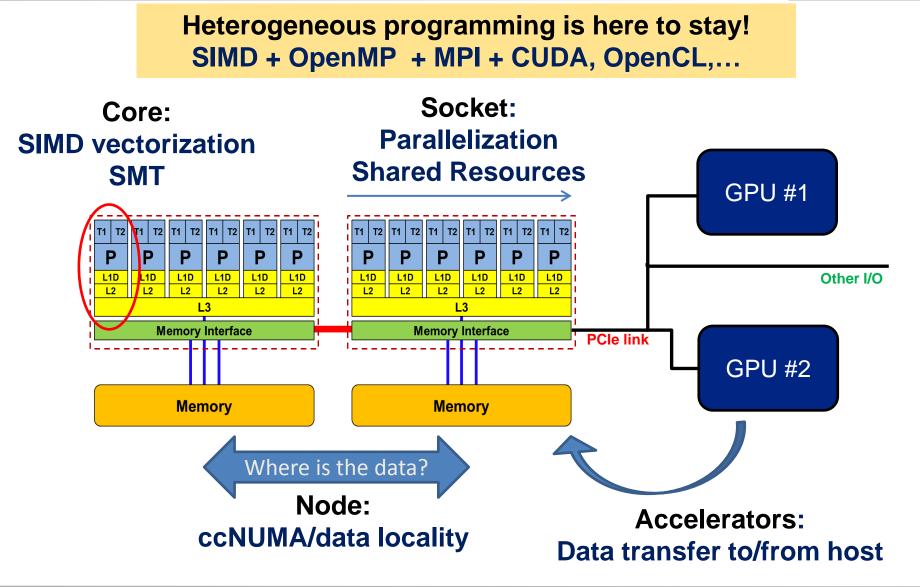

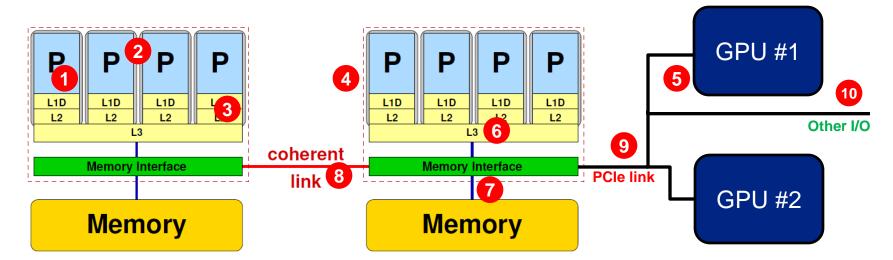

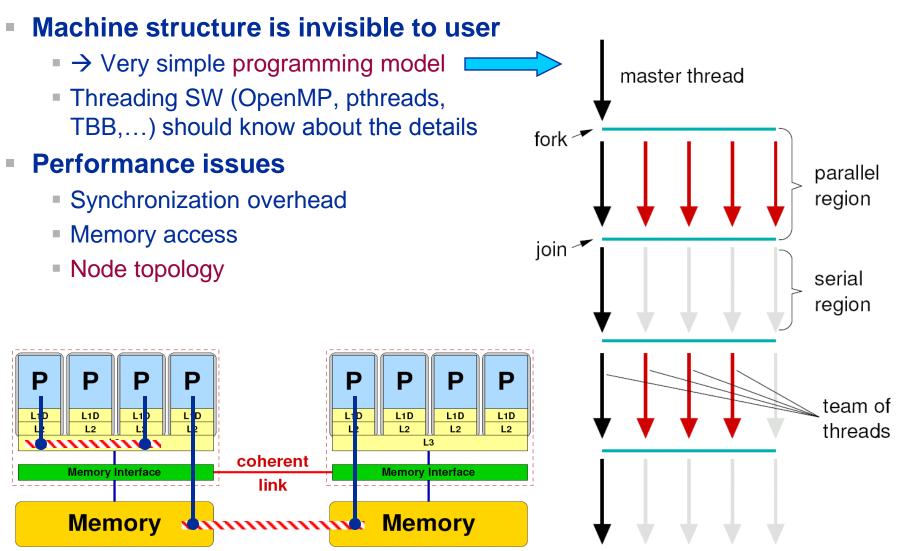

# Node topology and programming models

# Parallelism in a modern compute node

Parallel and shared resources within a shared-memory node

#### Parallel resources:

- Execution/SIMD units 1

- Cores (2)

- Inner cache levels 3

- Sockets / ccNUMA domains 4

- Multiple accelerators 5

#### **Shared resources:**

- Outer cache level per socket

- Memory bus per socket 7

- Intersocket link 8

- PCIe bus(es) 9

- Other I/O resources 10

#### How does your application react to all of those details?

## Parallel programming models

on modern compute nodes

#### Shared-memory (intra-node)

- Good old MPI

- OpenMP

- POSIX threads

- Intel Threading Building Blocks (TBB)

- Cilk+, OpenCL, StarSs,... you name it

#### Distributed-memory (inter-node)

- MPI

- PVM (gone)

### Hybrid

- Pure MPI

- MPI+OpenMP

- MPI + any shared-memory model

- MPI (+OpenMP) + CUDA/OpenCL/...

All models require awareness of *topology* and *affinity* issues for getting best performance out of the machine!

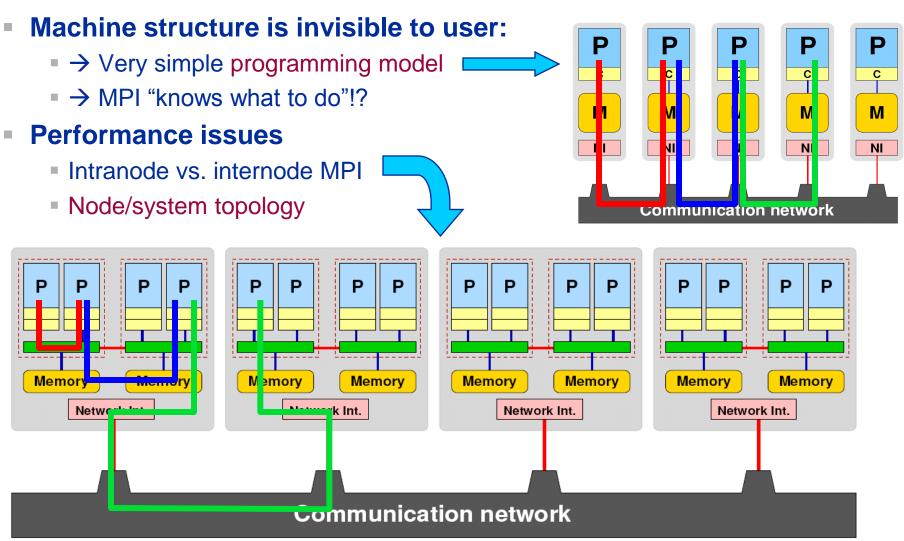

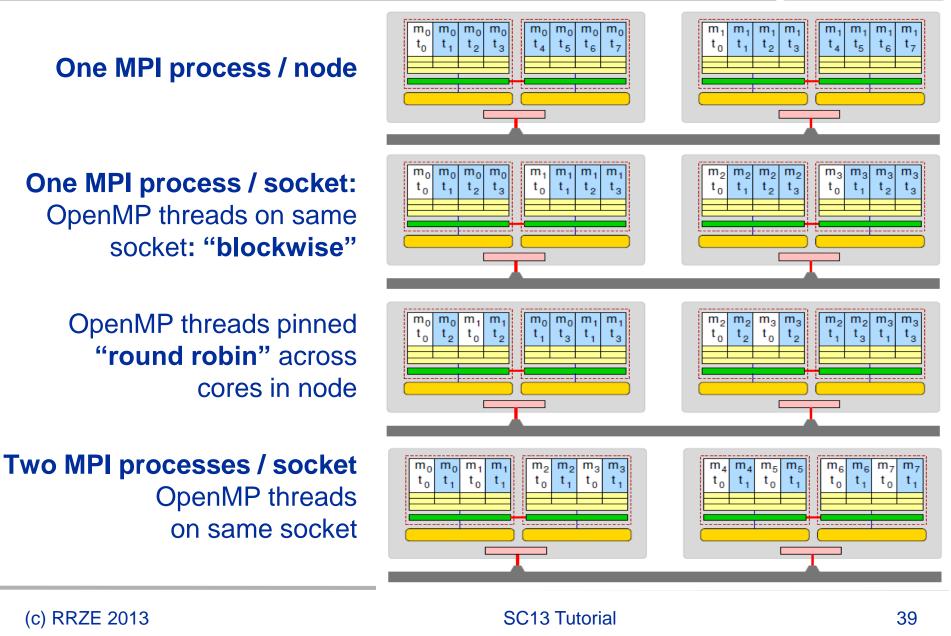

#### **Parallel programming models:** *Pure MPI*

#### **Parallel programming models:**

Pure threading on the node

## Parallel programming models: Lots of choices

Hybrid MPI+OpenMP on a multicore multisocket cluster

- Modern computer architecture has a rich "topology"

- Node-level hardware parallelism takes many forms

- Sockets/devices CPU: 1-8, GPGPU: 1-6

- Cores moderate (CPU: 4-16) to massive (GPGPU: 1000's)

- SIMD moderate (CPU: 2-8) to massive (GPGPU: 10's-100's)

- Superscalarity (CPU: 2-6)

- Exploiting performance: parallelism + bottleneck awareness

"High Performance Computing" == computing at a bottleneck

- Performance of programs is sensitive to architecture

- Topology/affinity influences overheads of popular programming models

- Standards do not contain (many) topology-aware features

- Things are starting to improve slowly (MPI 3.0, OpenMP 4.0)

- Apart from overheads, performance features are largely independent of the programming model

### Agenda

- Preliminaries

- Introduction to multicore architecture

- Cores, caches, chips, sockets, ccNUMA, SIMD

- LIKWID tools

- Microbenchmarking for architectural exploration

- Streaming benchmarks: throughput mode

- Streaming benchmarks: work sharing

- Roadblocks for scalability: Saturation effects and OpenMP overhead

- Lunch break

- Node-level performance modeling

- The Roofline Model

- Case study: 3D Jacobi solver and model-guided optimization

- Optimal resource utilization

- SIMD parallelism

- ccNUMA

- Simultaneous multi-threading (SMT)

- Optional: The ECM multicore performance model

# **Multicore Performance and Tools**

# Probing node topology

- Standard tools

- likwid-topology

#### (c) RRZE 2013

# How do we figure out the node topology?

#### Topology =

- Where in the machine does core #n reside? And do I have to remember this awkward numbering anyway?

- Which cores share which cache levels?

- Which hardware threads ("logical cores") share a physical core?

- Linux

- cat /proc/cpuinfo is of limited use

- Core numbers may change across kernels and BIOSes even on identical hardware

- numactl --hardware prints ccNUMA node information

- Information on caches is harder to obtain

| <pre>\$ numactlhardware</pre> |     |        |                   |  |  |  |

|-------------------------------|-----|--------|-------------------|--|--|--|

| avail                         | Lak | ole: 4 | nodes (0-3)       |  |  |  |

| node                          | 0   | cpus:  | 0 1 2 3 4 5       |  |  |  |

| node                          | 0   | size:  | 8189 MB           |  |  |  |

| node                          | 0   | free:  | 3824 MB           |  |  |  |

| node                          | 1   | cpus:  | 6 7 8 9 10 11     |  |  |  |

| node                          | 1   | size:  | 8192 MB           |  |  |  |

| node                          | 1   | free:  | 28 MB             |  |  |  |

| node                          | 2   | cpus:  | 18 19 20 21 22 23 |  |  |  |

| node                          | 2   | size:  | 8192 MB           |  |  |  |

| node                          | 2   | free:  | 8036 MB           |  |  |  |

| node                          | 3   | cpus:  | 12 13 14 15 16 17 |  |  |  |

| node                          | 3   | size:  | 8192 MB           |  |  |  |

| node                          | 3   | free:  | 7840 MB           |  |  |  |

LIKWID tool suite:

Like I Knew What I'm Doing

Open source tool collection (developed at RRZE):

http://code.google.com/p/likwid

J. Treibig, G. Hager, G. Wellein: *LIKWID: A lightweight performance-oriented tool suite for x86 multicore environments.* Accepted for PSTI2010, Sep 13-16, 2010, San Diego, CA http://arxiv.org/abs/1004.4431

# **Likwid Tool Suite**

KRUPS

#### Command line tools for Linux:

- easy to install

- works with standard linux 2.6 kernel

- simple and clear to use

- supports Intel and AMD CPUs

### Current tools:

- Iikwid-topology: Print thread and cache topology

- Iikwid-pin: Pin threaded application without touching code

- Iikwid-perfctr: Measure performance counters

- Iikwid-mpirun: mpirun wrapper script for easy LIKWID integration

- Iikwid-bench: Low-level bandwidth benchmark generator tool

- ... some more

#### (c) RRZE 2013

#### Output of likwid-topology -g

on one node of Cray XE6 "Hermit"

|              |             | erlagos processor                       | ****          | *****   |  |  |  |  |

|--------------|-------------|-----------------------------------------|---------------|---------|--|--|--|--|

| Hardware Thr | ead Topolog | īv                                      |               |         |  |  |  |  |

|              |             | *****                                   | ****          | ******  |  |  |  |  |

| Sockets:     | Sockets: 2  |                                         |               |         |  |  |  |  |

| Cores per so | cket:       | 16                                      |               |         |  |  |  |  |

| Threads per  |             |                                         |               |         |  |  |  |  |

|              | Thread      | Core                                    | Socket        |         |  |  |  |  |

| 0            | 0           | 0                                       | 0             |         |  |  |  |  |

| 1            | 0           | 1                                       | 0             |         |  |  |  |  |

| 2            | 0           | 2                                       | 0             |         |  |  |  |  |

| 3            | 0           | 3                                       | 0             |         |  |  |  |  |

| []           |             |                                         |               |         |  |  |  |  |

| 16           | 0           | 0                                       | 1             |         |  |  |  |  |

| 17           | 0           | 1                                       | 1             |         |  |  |  |  |

| 18           | 0           | 2                                       | 1             |         |  |  |  |  |

| 19           | 0           | 3                                       | 1             |         |  |  |  |  |

| []           |             |                                         |               |         |  |  |  |  |

|              |             |                                         | 10 14 15 \    |         |  |  |  |  |

|              |             | 5 6 7 8 9 10 11 12<br>20 21 22 23 24 25 |               | 0 21 1  |  |  |  |  |

| SOCKET I: (  | 10 1/ 10 19 | 20 21 22 23 24 25                       | 20 21 28 29 . | 50 3I ) |  |  |  |  |

|              |             |                                         |               |         |  |  |  |  |

| ****         | *****       | ****                                    | ****          | ******  |  |  |  |  |

| Cache Topolo |             |                                         |               |         |  |  |  |  |

| -            |             | ****                                    | ****          | ******  |  |  |  |  |

| Level: 1     |             |                                         |               |         |  |  |  |  |

| Size: 16 k   | в           |                                         |               |         |  |  |  |  |

|              |             | (1)(2)(3)(                              | 4) (5) (0     | 5) (7   |  |  |  |  |

|              |             | (17)(18)(19                             |               |         |  |  |  |  |

| 28)(29)      |             |                                         | / ( / (       | - / ( - |  |  |  |  |

| - / / /      | ,, ,        | *                                       |               |         |  |  |  |  |

#### (c) RRZE 2013

# **Output of likwid-topology continued**

Level: 2 Size: 2 MB Cache groups: (01)(23)(45)(67)(89)(1011)(1213)(1415)(1617)(18 19) (2021) (2223) (2425) (2627) (2829) (3031) Level: 3 Size: 6 MB Cache groups: (01234567) (89101112131415) (1617181920212223) (242526 27 28 29 30 31 ) NUMA Topology NUMA domains: 4 \_\_\_\_\_ Domain 0: Processors: 0 1 2 3 4 5 6 7 Memory: 7837.25 MB free of total 8191.62 MB \_\_\_\_\_ Domain 1: Processors: 8 9 10 11 12 13 14 15 Memory: 7860.02 MB free of total 8192 MB \_\_\_\_\_ Domain 2: Processors: 16 17 18 19 20 21 22 23 Memory: 7847.39 MB free of total 8192 MB \_\_\_\_\_ Domain 3: Processors: 24 25 26 27 28 29 30 31 Memory: 7785.02 MB free of total 8192 MB \_\_\_\_\_\_

#### (c) RRZE 2013

# **Output of likwid-topology continued**

| raphical:                                     | *****                               | *****                    |                      |                                      |                          |  |

|-----------------------------------------------|-------------------------------------|--------------------------|----------------------|--------------------------------------|--------------------------|--|

| ocket 0:                                      |                                     |                          |                      |                                      |                          |  |

| ++ ++ ++<br>  0     1   2     3<br>++ ++      | + ++ ++<br>    4     5  <br>+ ++ ++ |                          |                      | LO     11     12     13              | 14     15                |  |

| 16kB     16kB     16kB     16kB<br>++ ++ ++ + | 16kB     16kB  <br>+ ++             | 16kB     16kB  <br>++ ++ | 16kB     16kB     16 |                                      | 16kB     16kB<br>-+ ++ + |  |

| ++ +<br>  2MB     2MB<br>++ +                 | і і 2мв і<br>+ ++                   | 2MB  <br>++              | 2MB    <br>++ +      |                                      | 2MB                      |  |

| <br>+                                         | 6МВ                                 |                          | +6MB<br>+            |                                      |                          |  |

| ocket 1:                                      |                                     |                          |                      |                                      |                          |  |

| 16     17     18     19                       |                                     | 22     23                | 24     25     2      | 26     27     28     29<br>+ ++ ++ + | 30     31                |  |

| ++ ++ ++ +                                    | 16kB     16kB  <br>+ ++             | 16kB     16kB  <br>++ ++ | 16kB     16kB     16 | 6kB     16kB     16kB     16kB       | 16kB     16kB<br>-+ ++ + |  |

| ++ +<br>  2MB     2MB<br>++ +                 | і і 2мв і<br>+ ++                   | 2MB  <br>++              | 2MB    <br>++ +      | 2MB     2MB                          | 2MB                      |  |

|                                               | 6MB                                 | i                        | +                    |                                      |                          |  |

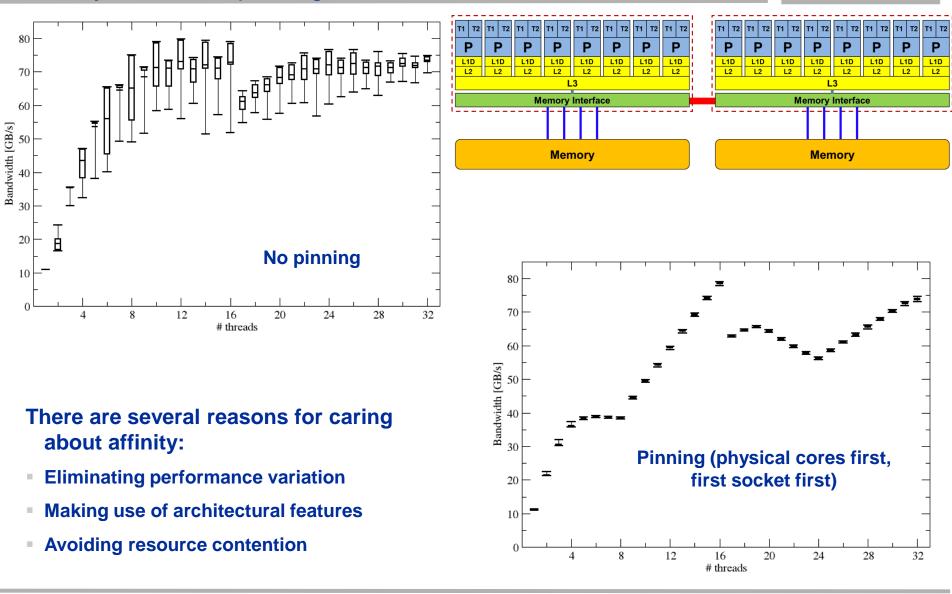

# Enforcing thread/process-core affinity under the Linux OS

- Standard tools and OS affinity facilities under program control

- likwid-pin

- aprun (Cray)

#### **Example: STREAM benchmark on 16-core Sandy Bridge:**

#### Anarchy vs. thread pinning

#### (c) RRZE 2013

#### **Generic thread/process-core affinity under Linux** *Overview*

- taskset [OPTIONS] [MASK | -c LIST ] \

[PID | command [args]...]

- taskset restricts processes/threads to a set of CPUs. Examples:

```

taskset 0x0006 ./a.out

taskset -c 4 33187

```

- Processes/threads can still move within the set!

- Alternative: let process/thread bind itself by executing syscall #include <sched.h> int sched\_setaffinity(pid\_t pid, unsigned int len, unsigned long \*mask);

- Disadvantage: which CPUs should you bind to on a non-exclusive machine?

- Still of value on multicore/multisocket cluster nodes, UMA or ccNUMA

Complementary tool: numactl

Example: numactl --physcpubind=0,1,2,3 command [args] Restricts process to specified physical core numbers

Example: numactl --cpunodebind=1 command [args] Restricts process to specified ccNUMA node(s)

- Many more options (e.g., interleave memory across nodes)

→ see section on ccNUMA optimization

- Diagnostic command (see earlier): numactl --hardware

Again, this is not suitable for a shared machine

#### Highly OS-dependent system calls

But available on all systems

```

Linux: sched_setaffinity(), PLPA (see below) → hwloc

Windows: SetThreadAffinityMask()

```

- Support for "semi-automatic" pinning in some compilers/environments

- Intel compilers > V9.1 (KMP\_AFFINITY environment variable)

- PGI, Pathscale, GNU

- SGI Altix dplace (works with logical CPU numbers!)

- Generic Linux: taskset, numactl, likwid-pin (see below)

- OpenMP 4.0 (see OpenMP tutorial)

### Affinity awareness in MPI libraries

- SGI MPT

- OpenMPI

- Intel MPI

- • •

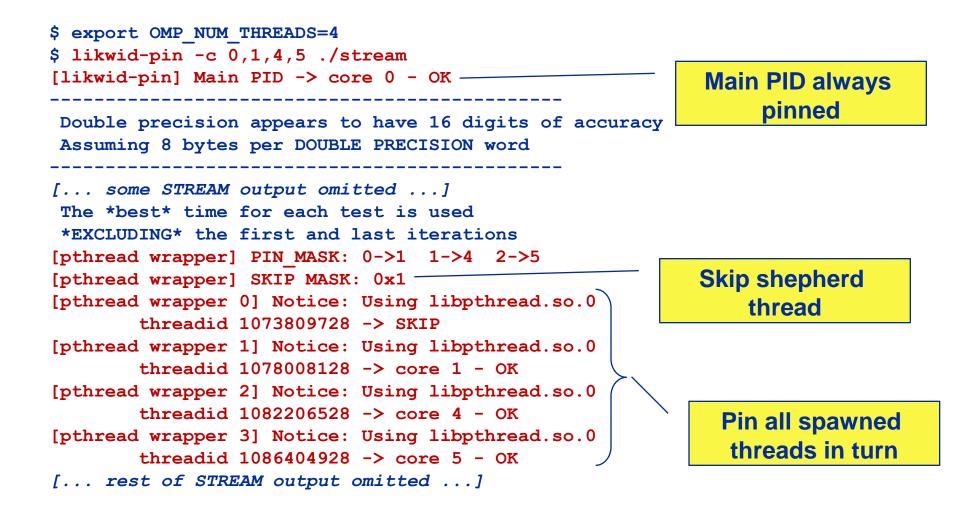

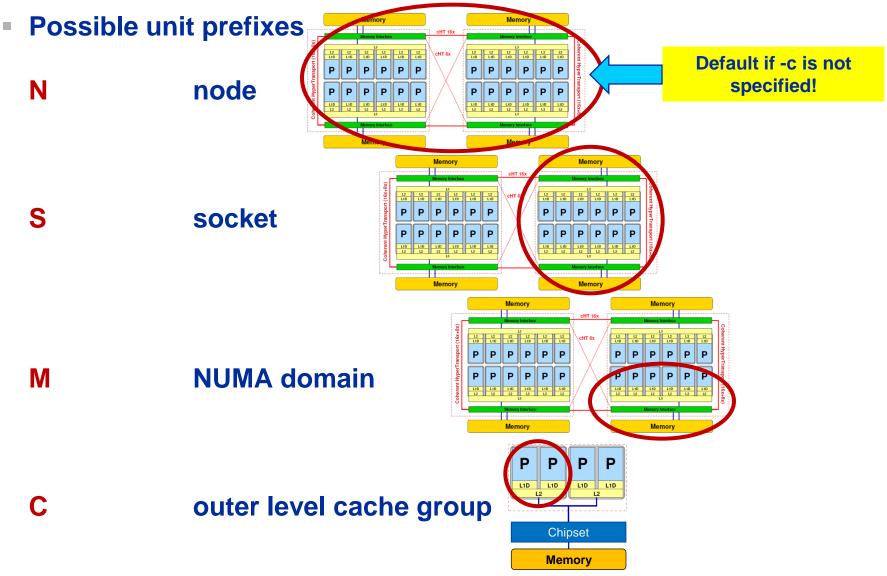

#### Likwid-pin Overview

- Pins processes and threads to specific cores without touching code

- Directly supports pthreads, gcc OpenMP, Intel OpenMP

- Based on combination of wrapper tool together with overloaded pthread library

binary must be dynamically linked!

- Can also be used as a superior replacement for taskset

- Supports logical core numbering within a node and within an existing CPU set

- Useful for running inside CPU sets defined by someone else, e.g., the MPI start mechanism or a batch system

#### Usage examples:

- Physical numbering (as given by likwid-topology): likwid-pin -c 0,2,4-6 ./myApp parameters

- Logical numbering by topological entities: likwid-pin -c S0:0-3 ./myApp parameters

#### Running the STREAM benchmark with likwid-pin:

#### (c) RRZE 2013

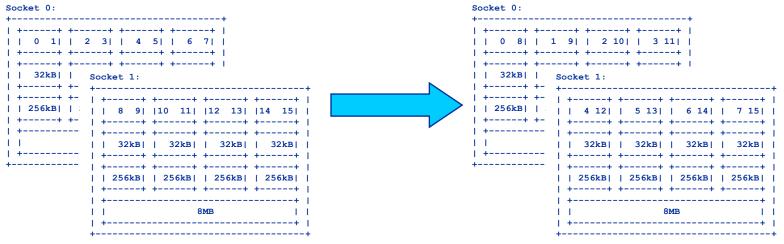

- Core numbering may vary from system to system even with identical hardware

- Likwid-topology delivers this information, which can then be fed into likwidpin

- Alternatively, likwid-pin can abstract this variation and provide a purely logical numbering (physical cores first)

Across all cores in the node:

OMP\_NUM\_THREADS=8 likwid-pin -c N:0-7 ./a.out

Across the cores in each socket and across sockets in each node: OMP\_NUM\_THREADS=8 likwid-pin -c S0:0-3@S1:0-3 ./a.out

#### (c) RRZE 2013

#### Likwid-pin Using logical core numbering

#### (c) RRZE 2013

# DEMO

# Multicore performance tools: Probing performance behavior

likwid-perfctr

- 1. Runtime profile / Call graph (gprof)

- 2. Instrument those parts which consume a significant part of runtime

- 3. Find performance signatures

**Possible signatures:**

- Bandwidth saturation

- Instruction throughput limitation (real or language-induced)

- Latency impact (irregular data access, high branch ratio)

- Load imbalance

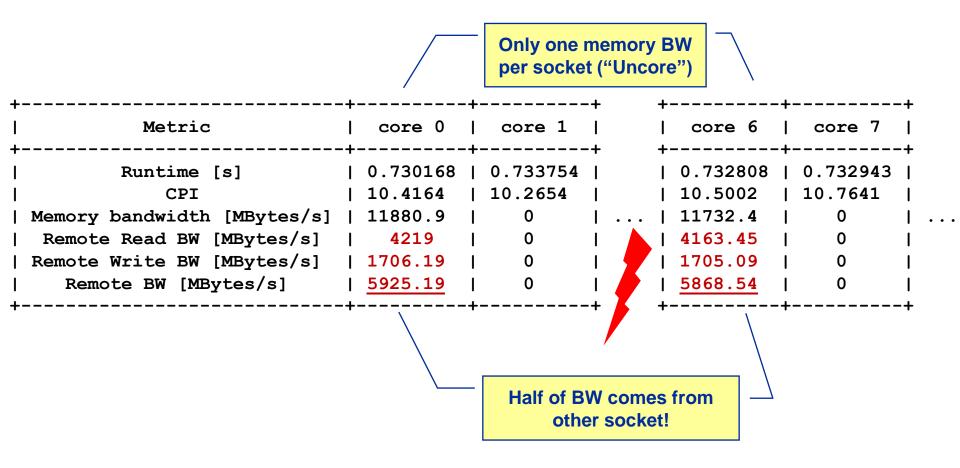

- ccNUMA issues (data access across ccNUMA domains)

- Pathologic cases (false cacheline sharing, expensive operations)

# **Probing performance behavior**

#### How do we find out about the performance properties and requirements of a parallel code?

Profiling via advanced tools is often overkill

#### A coarse overview is often sufficient

- likwid-perfctr (similar to "perfex" on IRIX, "hpmcount" on AIX, "lipfpm" on Linux/Altix)

- Simple end-to-end measurement of hardware performance metrics

- "Marker" API for starting/stopping counters

- Multiple measurement region support

- Preconfigured and extensible metric groups, list with likwid-perfctr -a

```

BRANCH: Branch prediction miss rate/ratio

CACHE: Data cache miss rate/ratio

CLOCK: Clock of cores

DATA: Load to store ratio

FLOPS_DP: Double Precision MFlops/s

FLOPS_SP: Single Precision MFlops/s

FLOPS_X87: X87 MFlops/s

L2: L2 cache bandwidth in MBytes/s

L2CACHE: L2 cache miss rate/ratio

L3: L3 cache bandwidth in MBytes/s

L3CACHE: L3 cache miss rate/ratio

MEM: Main memory bandwidth in MBytes/s

TLB: TLB miss rate/ratio

```

#### **likwid-perfctr** *Example usage with preconfigured metric group*

| <pre>\$ env OMP_NUM_THREADS=4 likwid-perfctr -C N:0-3 -g FLOPS_DP ./stream.exe<br/>CPU type: Intel Core Lynnfield processor</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                        |                                                         |                                      |                                                                            |                    |                    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--|--|

| CPU clock: 2.93 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                        |                                                         |                                      |                                                                            |                    |                    |  |  |

| Measuring group FLOPS_DP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                        | Always                                                  |                                      |                                                                            | Configured metrics |                    |  |  |

| YOUR PROGRAM OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                        | measured                                                |                                      |                                                                            | (this grou         | <b>p)</b>          |  |  |

| Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        | core 0                                                  | core 1                               | ec                                                                         | ore 2              | core 3             |  |  |

| INSTR_RETIRED_ANY         1.97463e+08   2.31001e+08   2.30963e+08   2.31885e+08         CPU_CLK_UNHALTED_CORE       9.56999e+08   9.58401e+08   9.58637e+08   9.57338e+08         FF_COMP_OFS_EXE_SSE_FF_DACKED         4.00294e+07   3.08927e+07   3.08866e+07   3.08904e+07         FF_COMP_OPS_EXE_SSE_FF_SCALAR       882   0   0   0         FF_COMP_OPS_EXE_SSE_SINGLE_PRECISION       0   0       0         FF_COMP_OPS_EXE_SSE_DOUBLE_PRECISION       0   0       0         FF_COMP_OPS_EXE_SSE_DOUBLE_PRECISION       4.00303e+07   3.08927e+07   3.08866e+07   3.08904e+07 |                                                                        |                                                         |                                      |                                                                            |                    |                    |  |  |

| ++<br>  Metric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ++<br>  core 0   c                                                     | +<br>core 1   c                                         | +<br>core 2                          | +<br>core 3                                                                | ,<br>L <b>\</b>    |                    |  |  |

| Runtime [s]         CPI         DP MFlops/s (DP assumed)         Packed MUOPS/s         Scalar MUOPS/s         SP MUOPS/s         DP MUOPS/s                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.84647   4<br>  245.399   1<br>  122.698   9<br>  0.00270351  <br>  0 | 4.14891   4.<br>189.108   18<br>94.554   94<br>0  <br>0 | 89.024   1<br>4.5121   9<br>0  <br>0 | 0.326358  <br>4.12849  <br>L89.304  <br>94.6519  <br>0  <br>0  <br>94.6519 |                    | Derived<br>metrics |  |  |

#### (c) RRZE 2013

#### likwid-perfctr

Best practices for runtime counter analysis

# Things to look at (in roughly this order)

- Load balance (flops, instructions, BW)

- In-socket memory BW saturation

- Shared cache BW saturation

- Flop/s, loads and stores per flop metrics

- SIMD vectorization

- CPI metric

- # of instructions, branches, mispredicted branches

#### Caveats

- Load imbalance may not show in CPI or # of instructions

- Spin loops in OpenMP barriers/MPI blocking calls

- Looking at "top" or the Windows Task Manager does not tell you anything useful

- In-socket performance saturation may have various reasons

- Cache miss metrics are overrated

- If I really know my code, I can often calculate the misses

- Runtime and resource utilization is much more important

#### (c) RRZE 2013

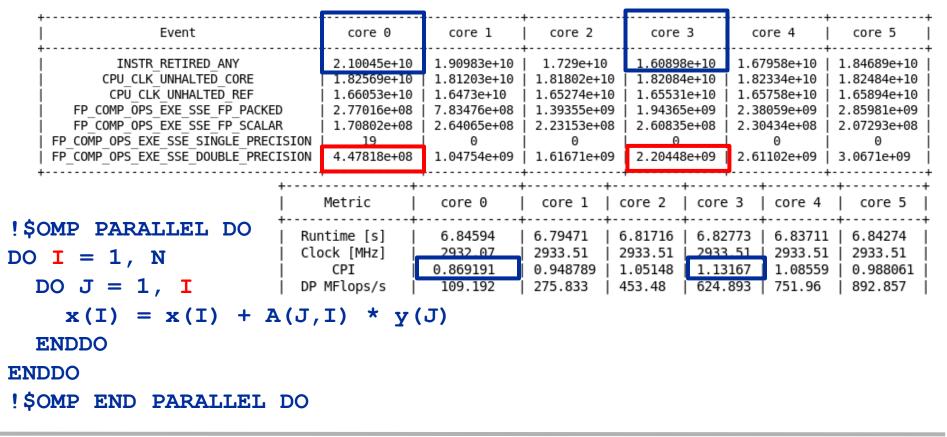

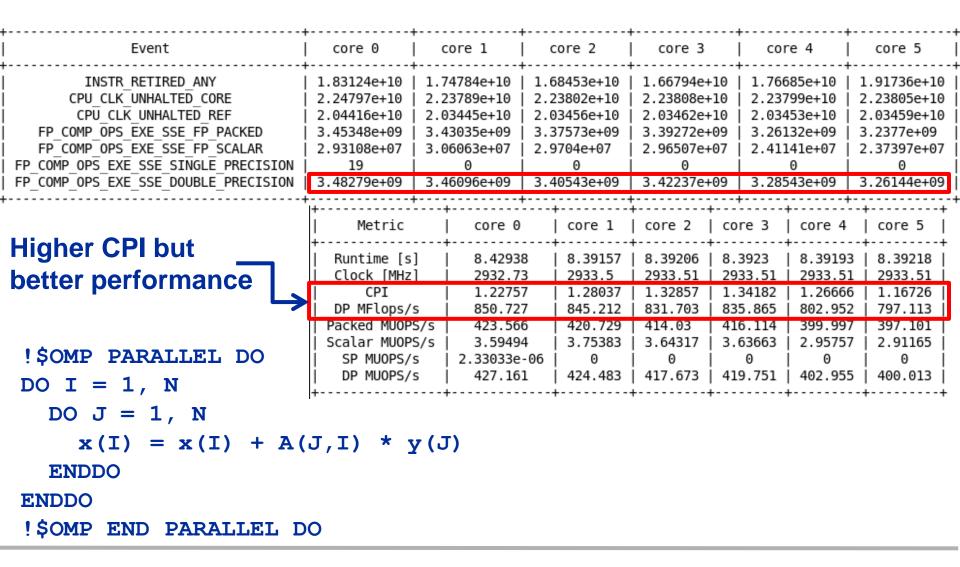

#### likwid-perfctr Identify load imbalance...

- Instructions retired / CPI may not be a good indication of useful workload – at least for numerical / FP intensive codes....

- Floating Point Operations Executed is often a better indicator

- Waiting / "Spinning" in barrier generates a high instruction count

#### env OMP\_NUM\_THREADS=6 likwid-perfctr -C S0:0-5 -g FLOPS\_DP ./a.out

(c) RRZE 2013

likwid-perfctr counts events on cores; it has no notion of what kind of code is running (if any)

This enables to listen on what currently happens without any overhead:

likwid-perfctr -c N:0-11 -g FLOPS\_DP -s 10

- It can be used as cluster/server monitoring tool

- A frequent use is to measure a certain part of a long running parallel application from outside

Iikwid-perfctr supports time resolved measurements of full node: likwid-perfctr -c N:0-11 -g MEM -d 50ms > out.txt

(c) RRZE 2013

#### likwid-perfctr Marker API

- To measure only parts of an application a marker API is available.

- The API only turns counters on/off. The configuration of the counters is still done by likwid-perfctr application.

- Multiple named regions can be measured

- Results on multiple calls are accumulated

- Inclusive and overlapping Regions are allowed

```

likwid_markerInit(); // must be called from serial region

likwid_markerStartRegion("Compute");

....

likwid_markerStopRegion("Compute");

likwid_markerStartRegion("postprocess");

....

likwid_markerStopRegion("postprocess");

```

likwid\_markerClose(); // must be called from serial region

#### **likwid-perfctr** *Group files*

SHORT PSTI

EVENTSET FIXCO INSTR RETIRED ANY FIXC1 CPU CLK UNHALTED CORE FIXC2 CPU CLK UNHALTED REF FP COMP OPS EXE SSE FP PACKED PMC0 PMC1 FP COMP OPS EXE SSE FP SCALAR FP\_COMP\_OPS\_EXE\_SSE\_SINGLE\_PRECISION PMC2 FP COMP OPS EXE SSE DOUBLE PRECISION PMC3 UPMCO UNC QMC NORMAL READS ANY UPMC1 UNC QMC WRITES FULL ANY UPMC2 UNC QHL REQUESTS REMOTE READS UPMC3 UNC QHL REQUESTS LOCAL READS METRICS Runtime [s] FIXC1\*inverseClock CPI FIXC1/FIXC0 Clock [MHz] 1.E-06\*(FIXC1/FIXC2)/inverseClock DP MFlops/s (DP assumed) 1.0E-06\*(PMC0\*2.0+PMC1)/time Packed MUOPS/s 1.0E-06\*PMC0/time Scalar MUOPS/s 1.0E-06\*PMC1/time SP MUOPS/s 1.0E-06\*PMC2/time DP MUOPS/s 1.0E-06\*PMC3/time Memory bandwidth [MBytes/s] 1.0E-06\*(UPMC0+UPMC1)\*64/time; Remote Read BW [MBytes/s] 1.0E-06\*(UPMC2)\*64/time; LONG Formula:

Groups are architecture-specificThey are defined in simple text files

- Codo is concrated on recompile of

- Code is generated on recompile of likwid

- likwid-perfctr -a outputs list of groups

- For every group an extensive documentation is available

DP MFlops/s = (FP\_COMP\_OPS\_EXE\_SSE\_FP\_PACKED\*2 + FP\_COMP\_OPS\_EXE\_SSE\_FP\_SCALAR) / runtime.

# Measuring energy consumption with LIKWID

| Measuring energy consumption<br>likwid-powermeter and likwid-perfctr -g ENERGY |                                                                        |  |  |  |  |  |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|

| -                                                                              | ts Intel RAPL interface (Sandy Bridge)<br>Running average power limit" |  |  |  |  |  |

| CPU name:                                                                      |                                                                        |  |  |  |  |  |

| CPU clock:                                                                     | 3.49 GHz                                                               |  |  |  |  |  |

| Base clock:                                                                    |                                                                        |  |  |  |  |  |

| Minimal clock                                                                  | : 1600.00 MHz                                                          |  |  |  |  |  |

| Turbo Boost St                                                                 | teps:                                                                  |  |  |  |  |  |

| C1 3900.00 MH:                                                                 | z                                                                      |  |  |  |  |  |

| C2 3800.00 MH:                                                                 | Ζ                                                                      |  |  |  |  |  |

| СЗ 3700.00 МН:                                                                 | Ζ                                                                      |  |  |  |  |  |

| C4 3600.00 MH:                                                                 | Ζ                                                                      |  |  |  |  |  |

| Thermal Spec 1                                                                 | Power: 95 Watts                                                        |  |  |  |  |  |

| Minimum Power                                                                  | r: 20 Watts                                                            |  |  |  |  |  |

| Maximum Power                                                                  | r: 95 Watts                                                            |  |  |  |  |  |

| Maximum Time                                                                   | Window: 0.15625 micro sec                                              |  |  |  |  |  |

#### **Example:** A medical image reconstruction code on Sandy Bridge

#### Sandy Bridge EP (8 cores, 2.7 GHz base freq.)

| Test case          | Runtime [s] | Power [W] |                    | Energy [J] |

|--------------------|-------------|-----------|--------------------|------------|

| 8 cores, plain C   | 90.43       | 90        | Fas<br><b>→</b> le | 8110       |

| 8 cores, SSE       | 29.63       | 93        | ter (<br>ss e      | 2750       |

| 8 cores (SMT), SSE | 22.61       | 102       | code               | 2300       |

| 8 cores (SMT), AVX | 18.42       | 111       |                    | 2040       |

|                    | •           |           |                    |            |

# Agenda

- Preliminaries

- Introduction to multicore architecture

- Cores, caches, chips, sockets, ccNUMA, SIMD

- LIKWID tools

# Microbenchmarking for architectural exploration

- Streaming benchmarks: throughput mode

- Streaming benchmarks: work sharing

- Roadblocks for scalability: Saturation effects and OpenMP overhead

- Lunch break

- Node-level performance modeling

- The Roofline Model

- Case study: 3D Jacobi solver and model-guided optimization

- Optimal resource utilization

- SIMD parallelism

- ccNUMA

- Simultaneous multi-threading (SMT)

- Optional: The ECM multicore performance model

# Microbenchmarking for architectural exploration

Probing of the memory hierarchy Saturation effects in cache and memory Typical OpenMP overheads

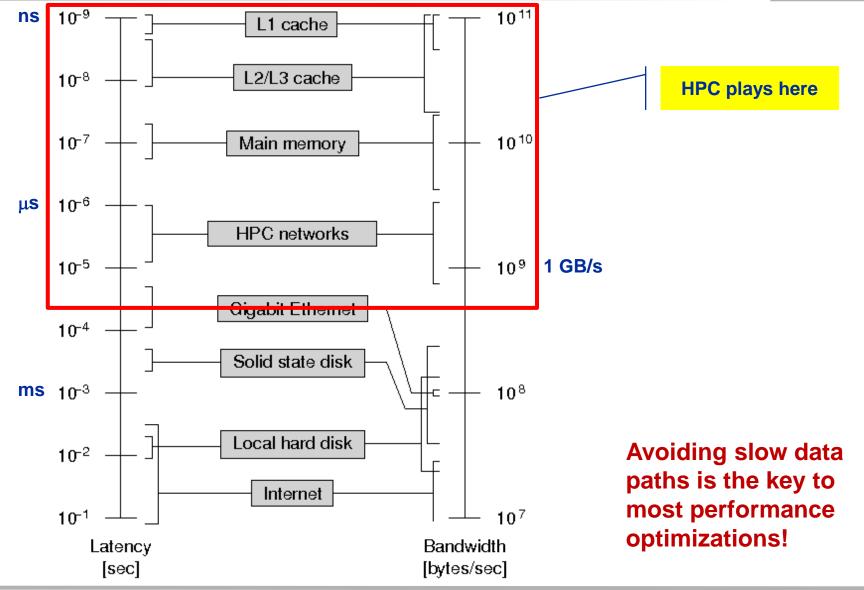

## Latency and bandwidth in modern computer environments

(c) RRZE 2013

# Recap: Data transfers in a memory hierarchy

- How does data travel from memory to the CPU and back?

- Example: Array copy A(:)=C(:)

(c) RRZE 2013

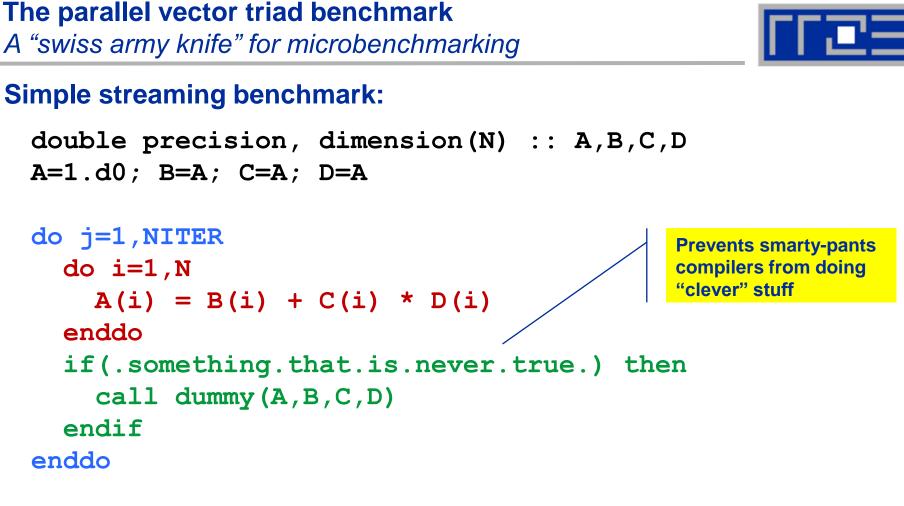

- Report performance for different N

- Choose NITER so that accurate time measurement is possible

- This kernel is limited by data transfer performance for all memory levels on all current architectures!

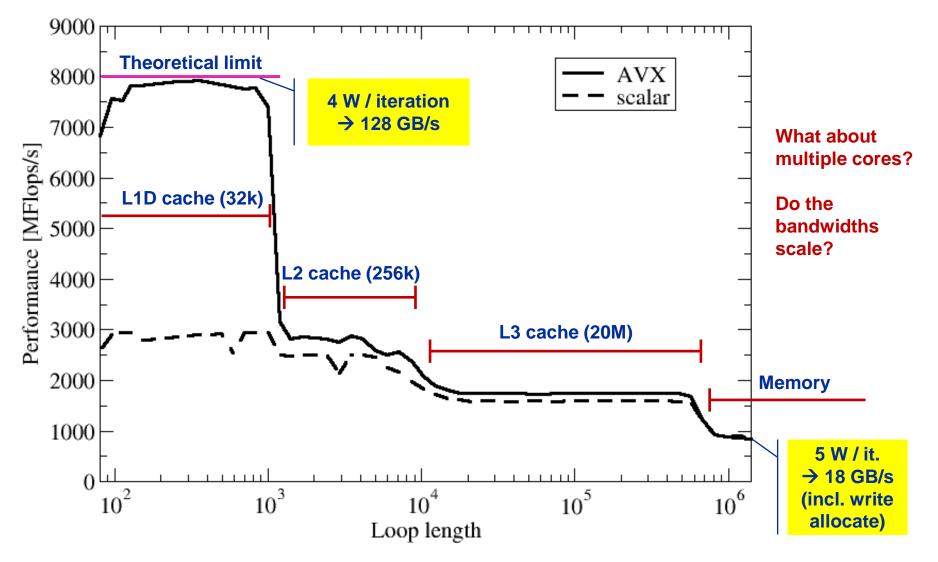

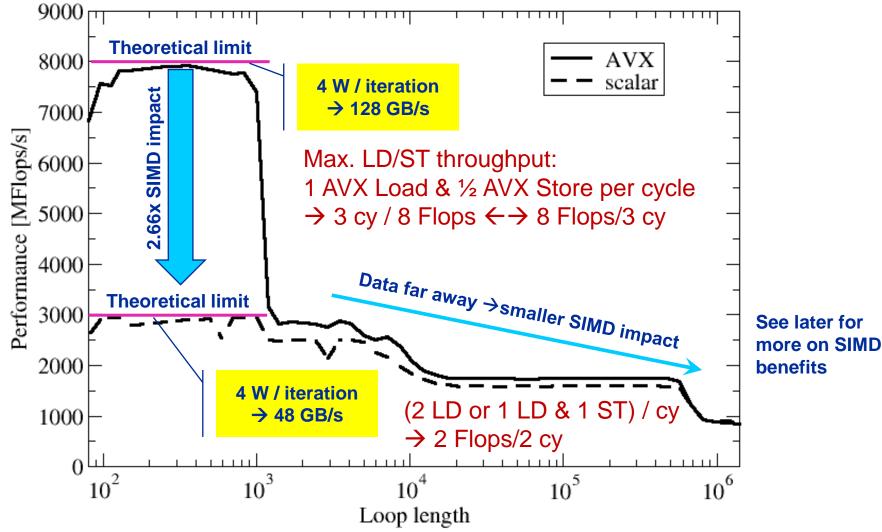

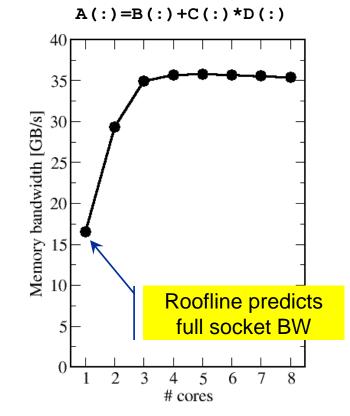

## A(:)=B(:)+C(:)\*D(:) on one Sandy Bridge core (3 GHz)

(c) RRZE 2013

(c) RRZE 2013

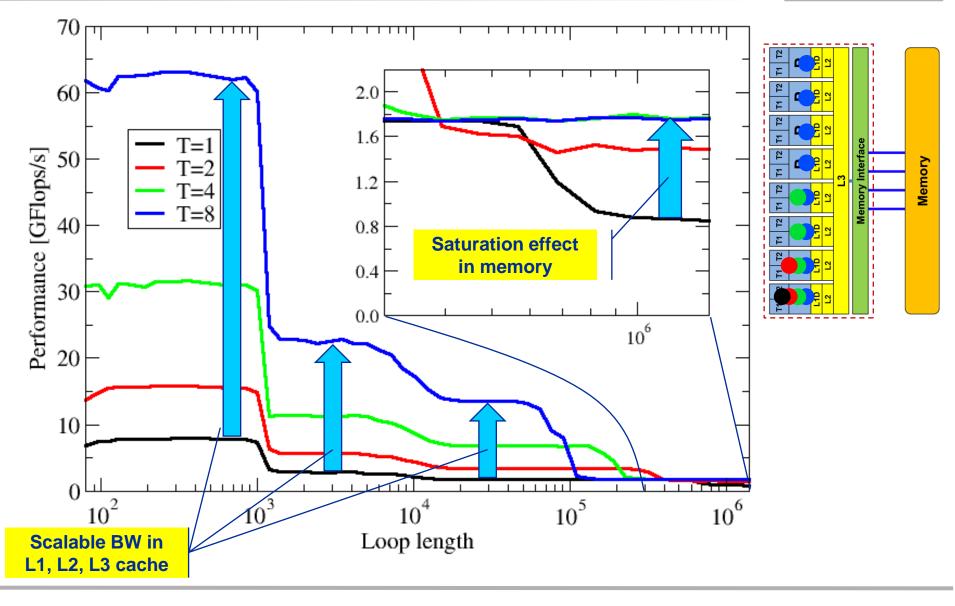

## Every core runs its own, independent triad benchmark

```

double precision, dimension(:), allocatable :: A,B,C,D

```

```

!$OMP PARALLEL private(i,j,A,B,C,D)

allocate(A(1:N), B(1:N), C(1:N), D(1:N))

A=1.d0; B=A; C=A; D=A

do j=1,NITER

do i=1,N

A(i) = B(i) + C(i) * D(i)

enddo

if(.something.that.is.never.true.) then

call dummy (A, B, C, D)

endif

enddo

!$OMP END PARALLEL

```

# → pure hardware probing, no impact from OpenMP overhead

```

(c) RRZE 2013

```

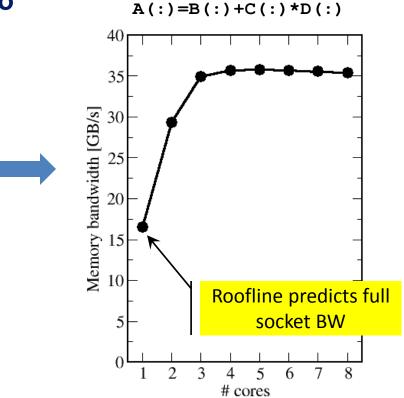

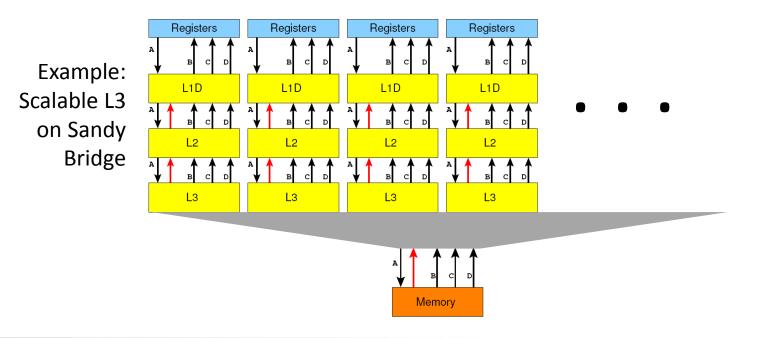

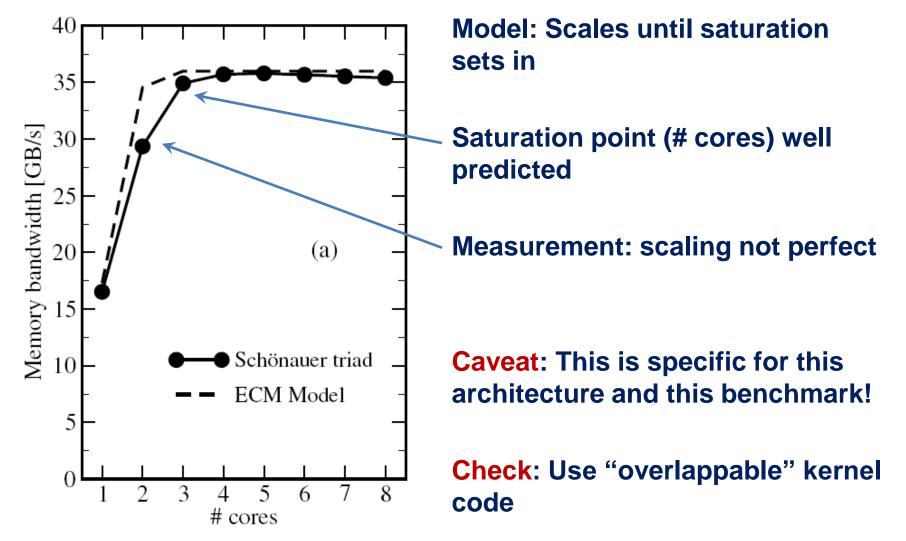

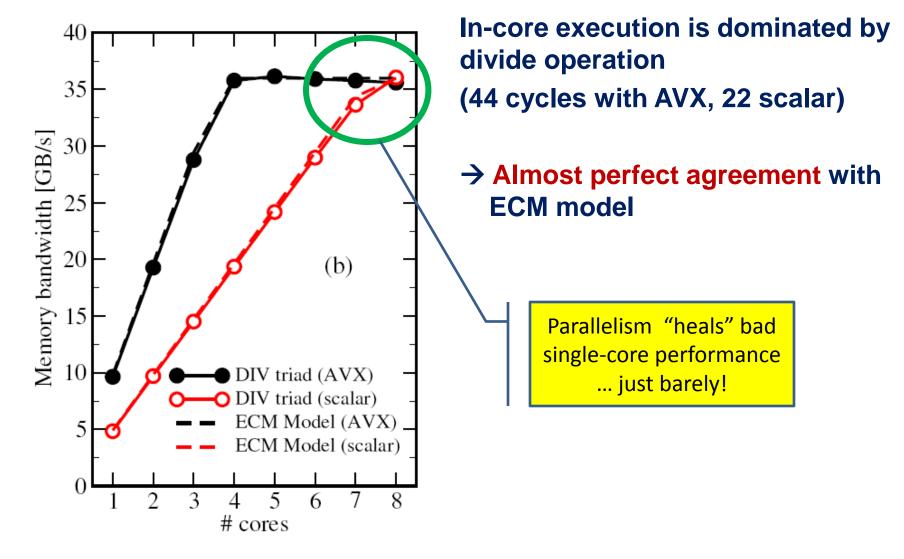

## **Throughput vector triad on Sandy Bridge socket (3 GHz)**

(c) RRZE 2013

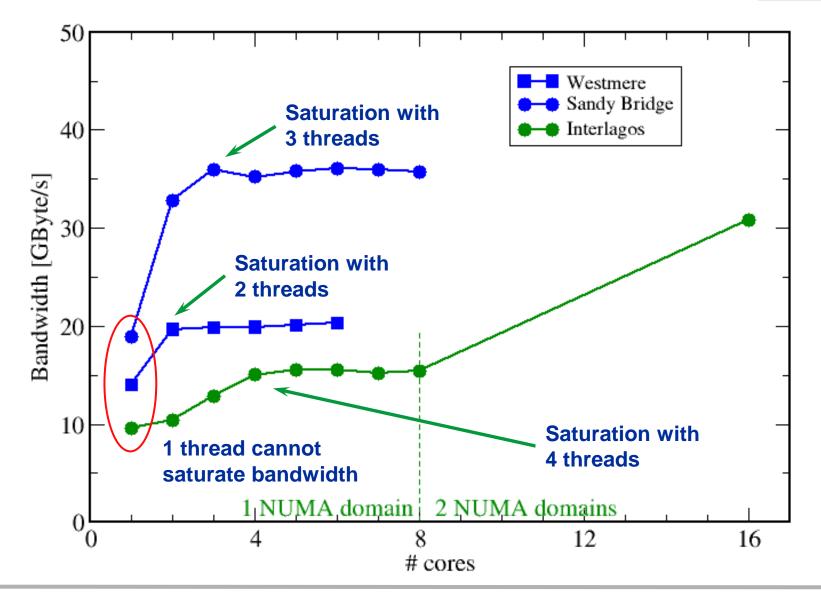

## **Bandwidth limitations: Main Memory**

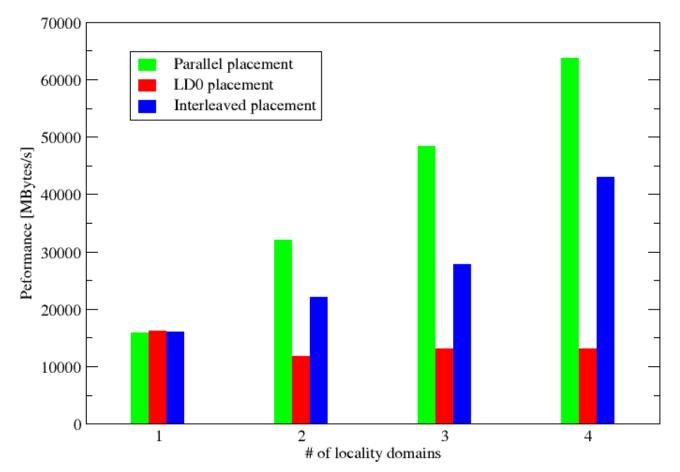

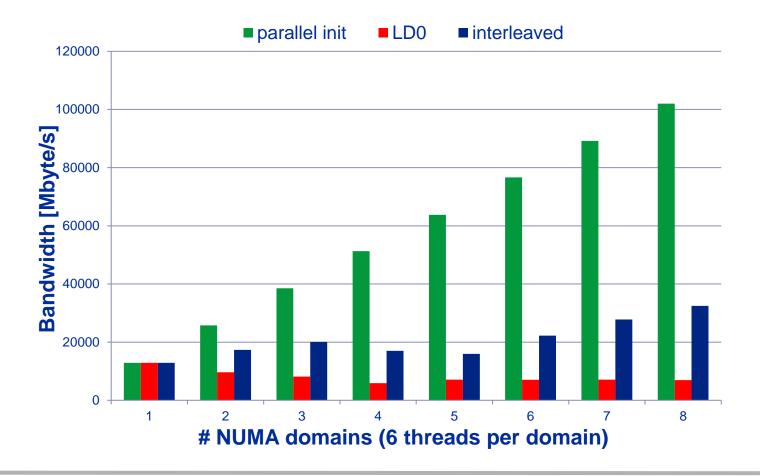

Scalability of shared data paths inside a NUMA domain (V-Triad)

(c) RRZE 2013

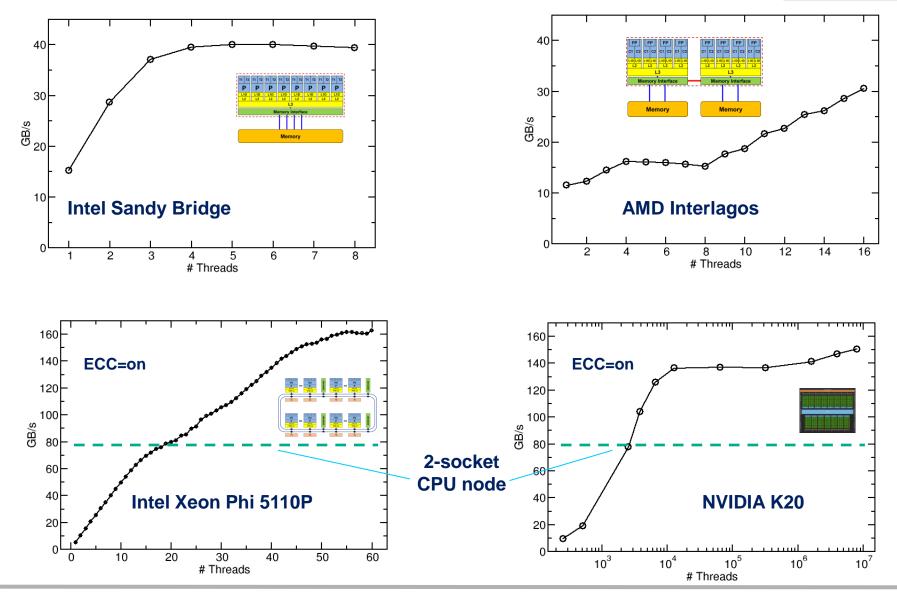

## **Attainable memory bandwidth: Comparing architectures**

(c) RRZE 2013

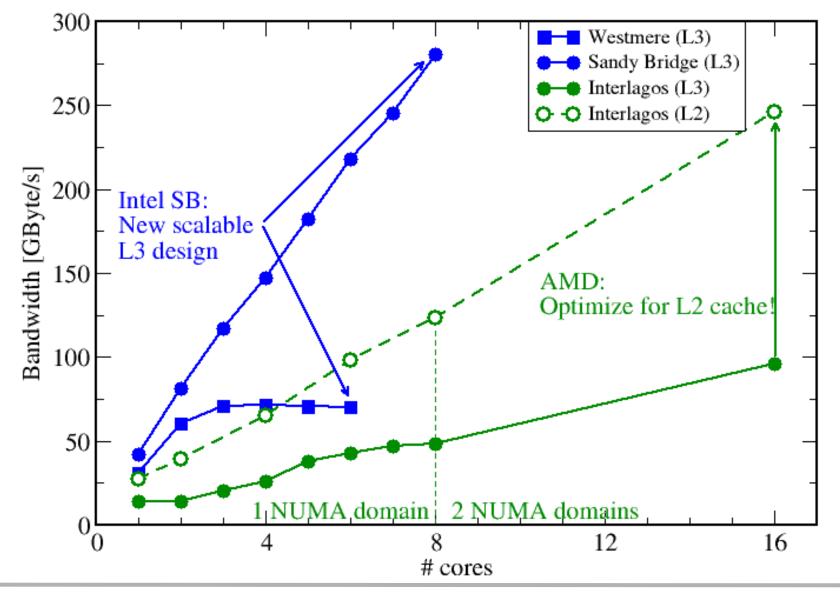

#### **Bandwidth limitations: Outer-level cache**

Scalability of shared data paths in L3 cache

(c) RRZE 2013

## **OpenMP work sharing in the benchmark loop**

```

double precision, dimension(:), allocatable :: A,B,C,D

```

```

allocate(A(1:N), B(1:N), C(1:N), D(1:N))

A=1.d0; B=A; C=A; D=A

!$OMP PARALLEL private(i,j)

do j=1, NITER

!$OMP DO

do i=1,N

A(i) = B(i) + C(i) * D(i)

enddo

Implicit barrier

!SOMP END DO

if(.something.that.is.never.true.) then

call dummy (A, B, C, D)

endif

enddo

!$OMP END PARALLEL

```

# **OpenMP vector triad on Sandy Bridge socket (3 GHz)**

(c) RRZE 2013

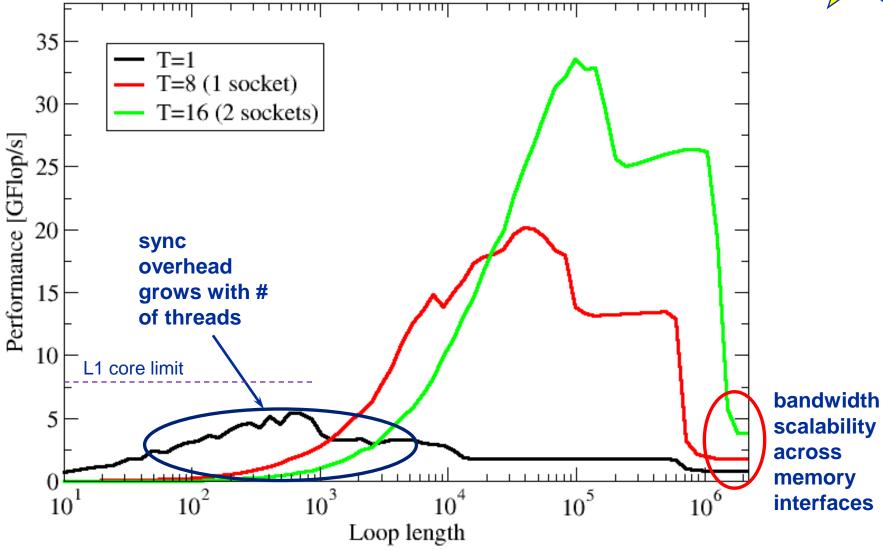

# **OpenMP performance issues** on multicore

Synchronization (barrier) overhead

**!\$OMP PARALLEL** ...

\$0MP BARRIER

!\$OMP DO

•••

!\$OMP ENDDO !\$OMP END PARALLEL Threads are synchronized at **explicit** AND **implicit** barriers. These are a main source of overhead in OpenMP progams.

Determine costs via modified OpenMP Microbenchmarks testcase (epcc)

# On x86 systems there is no hardware support for synchronization!

- Next slide: Test OpenMP Barrier performance...

- for different compilers

- and different topologies:

- shared cache

- shared socket

- between sockets

- and different thread counts

- 2 threads

- full domain (chip, socket, node)

#### (c) RRZE 2013

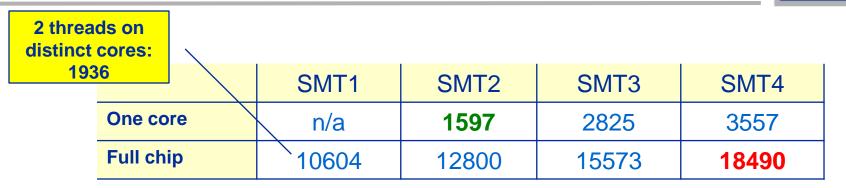

# **Thread synchronization overhead on SandyBridge-EP** *Barrier overhead in CPU cycles*

| 2 Threads    | Intel 13.1.0 | GCC 4.7.0 | GCC 4.6.1 |

|--------------|--------------|-----------|-----------|

| Shared L3    | 384          | 5242      | 4616      |

| SMT threads  | 2509         | 3726      | 3399      |

| Other socket | 1375         | 5959      | 4909      |

| Full domain | Intel 13.1.0 | GCC 4.7.0 | GCC 4.6.1 |

|-------------|--------------|-----------|-----------|

| Socket      | 1497         | 14546     | 14418     |

| Node        | 3401         | 34667     | 29788     |

| Node +SMT   | 6881         | 59038     | 58898     |

### (c) RRZE 2013

# Thread synchronization overhead on Intel Xeon Phi

Barrier overhead in CPU cycles

That does not look bad for 240 threads!

Still the pain may be much larger, as more work can be done in one cycle on Phi compared to a full Sandy Bridge node

3.75 x cores (16 vs 60) on Phi

2 x more operations per cycle on Phi

2.7 x more barrier penalty (cycles) on Phi

7.5 x more work done on Xeon Phi per cycle

One barrier causes  $2.7 \times 7.5 = 20 \times \text{more pain} \odot$ .

#### (c) RRZE 2013

# Affinity matters!

- Almost all performance properties depend on the position of

- Data

- Threads/processes

- Consequences

- Know where your threads are running

- Know where your data is

- Bandwidth bottlenecks are ubiquitous

- Synchronization overhead may be an issue

- ... and also depends on affinity!

- Many-core poses new challenges in terms of synchronization

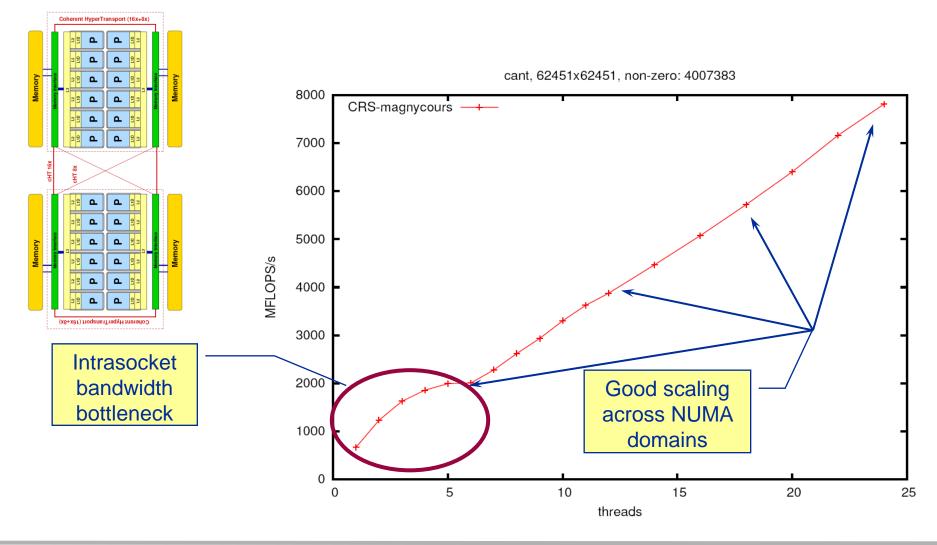

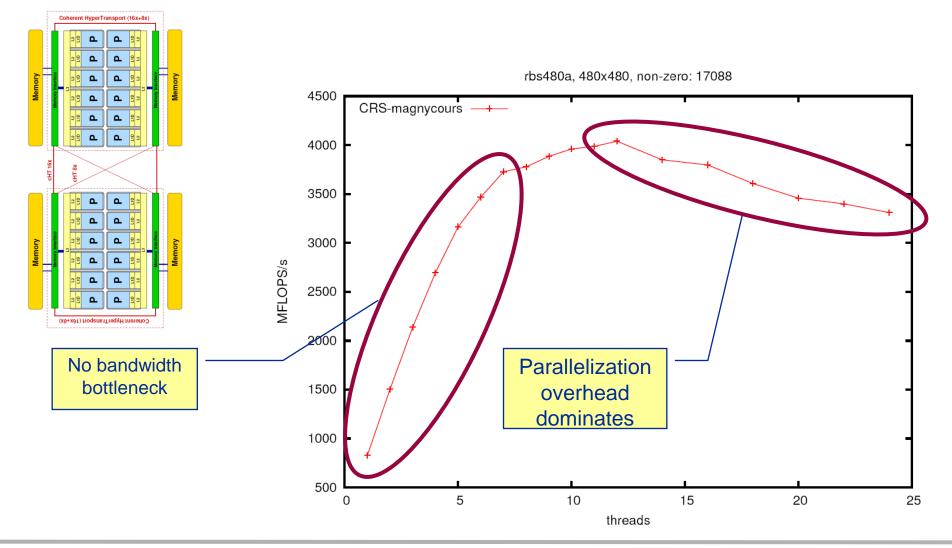

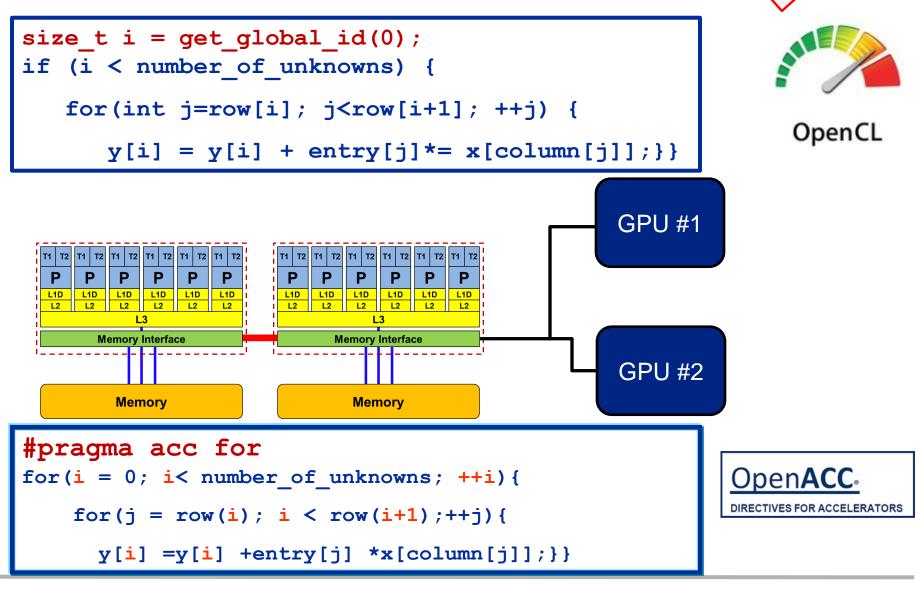

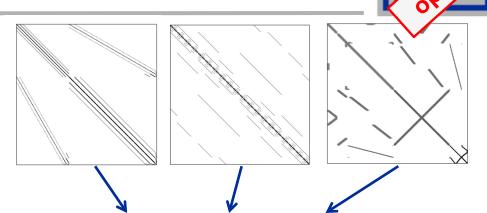

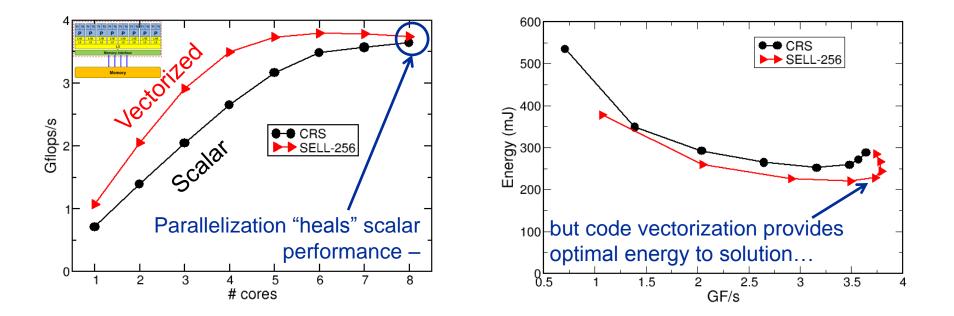

# Case study: OpenMP-parallel sparse matrix-vector multiplication (part 1)

A simple (but sometimes not-so-simple) example for bandwidth-bound code and saturation effects in memory

# **Case study: Sparse matrix-vector multiply**

- Important kernel in many applications (matrix diagonalization, solving linear systems)

- Strongly memory-bound for large data sets

- Streaming, with partially indirect access:

```

!$OMP parallel do

do i = 1,Nr

do j = row_ptr(i), row_ptr(i+1) - 1

c(i) = c(i) + val(j) * b(col_idx(j))

enddo

enddo

!$OMP end parallel do

```

- Usually many spMVMs required to solve a problem

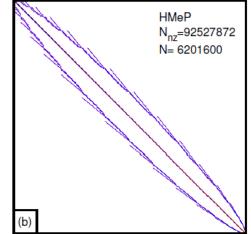

- Following slides: Performance data on one 24-core AMD Magny Cours node

# **Application: Sparse matrix-vector multiply**

Strong scaling on one XE6 Magny-Cours node

## Case 1: Large matrix

(c) RRZE 2013

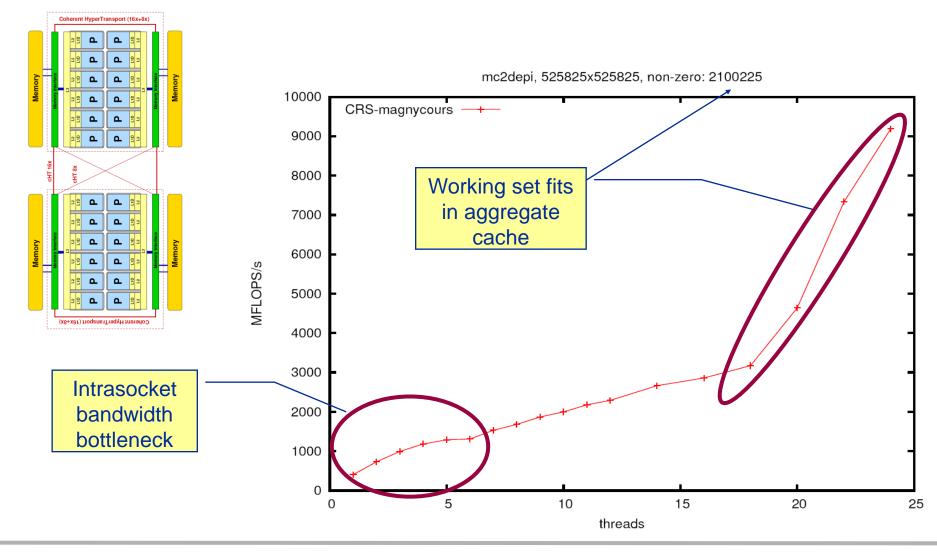

# **Application: Sparse matrix-vector multiply**

Strong scaling on one XE6 Magny-Cours node

# Case 2: Medium size

(c) RRZE 2013

# **Application: Sparse matrix-vector multiply**

Strong scaling on one Magny-Cours node

# Case 3: Small size

(c) RRZE 2013

- If the problem is "large", bandwidth saturation on the socket is a reality

- → There are "spare cores"

- Very common performance pattern

- What to do with spare cores?

- Let them idle → saves energy with minor loss in time to solution

- Use them for other tasks, such as MPI communication

# Can we predict the saturated performance?

- Bandwidth-based performance modeling!

- What is the significance of the indirect access?<sup>2</sup> Can it be modeled?

- Can we predict the saturation point?

- ... and why is this important?

# (c) RRZE 2013

# Agenda

- Preliminaries

- Introduction to multicore architecture

- Cores, caches, chips, sockets, ccNUMA, SIMD

- LIKWID tools

- Microbenchmarking for architectural exploration

- Streaming benchmarks: throughput mode

- Streaming benchmarks: work sharing

- Roadblocks for scalability: Saturation effects and OpenMP overhead

- Lunch break

# Node-level performance modeling

- The Roofline Model

- Case study: 3D Jacobi solver and model-guided optimization

- Optimal resource utilization

- SIMD parallelism

- ccNUMA

- Simultaneous multi-threading (SMT)

- Optional: The ECM multicore performance model

# "Simple" performance modeling: The Roofline Model

Loop-based performance modeling: Execution vs. data transfer Example: array summation Example: A 3D Jacobi solver Model-guided optimization

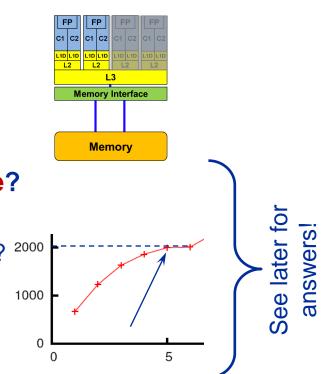

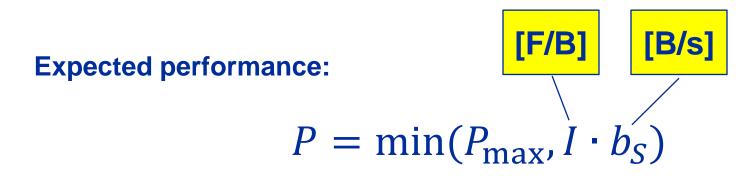

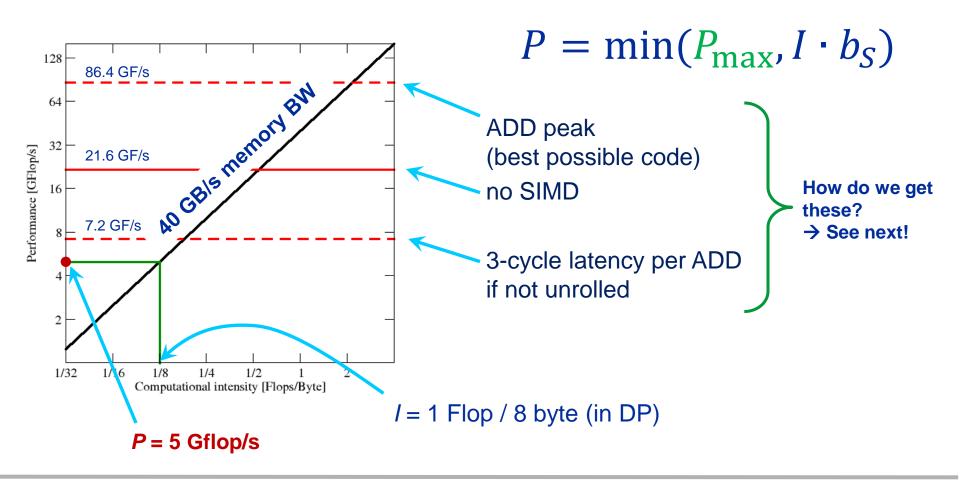

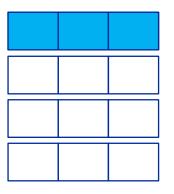

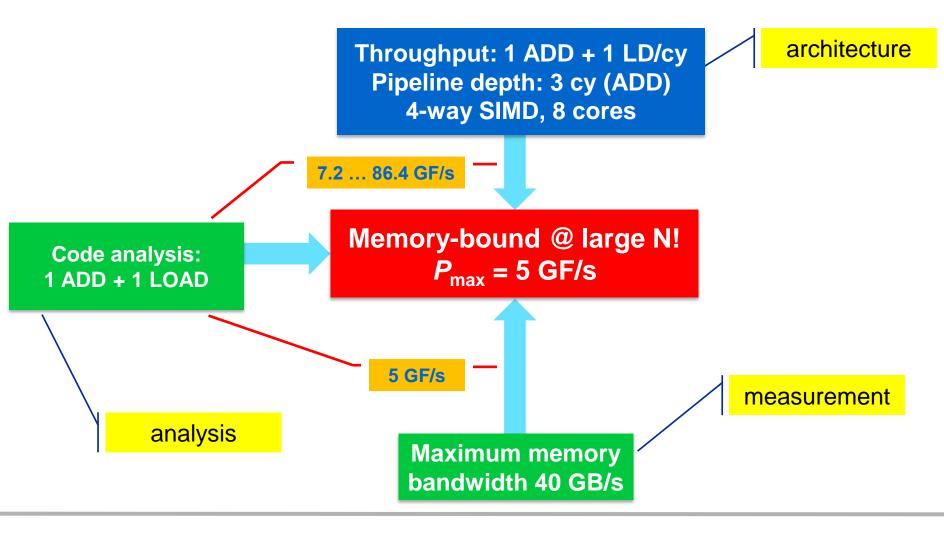

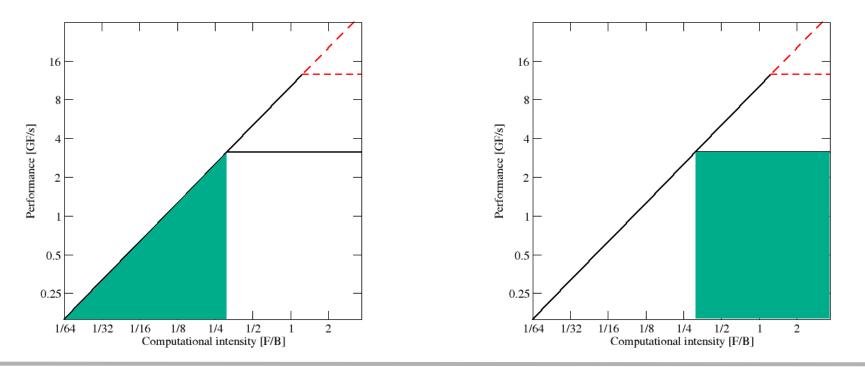

# The Roofline Model<sup>1,2</sup>

- 1.  $P_{\text{max}}$  = Applicable peak performance of a loop, assuming that data comes from L1 cache (this is not necessarily  $P_{\text{peak}}$ )

- 2. *I* = Computational intensity ("work" per byte transferred) over the slowest data path utilized ("the bottleneck")

- Code balance  $B_{\rm C} = I^{-1}$

- 3.  $b_s = Applicable peak bandwidth of the slowest data path utilized$

<sup>1</sup> W. Schönauer: <u>Scientific Supercomputing: Architecture and Use of Shared and Distributed Memory Parallel Computers</u>. (2000) <sup>2</sup> S. Williams: <u>Auto-tuning Performance on Multicore Computers</u>. UCB Technical Report No. UCB/EECS-2008-164. PhD thesis (2008)

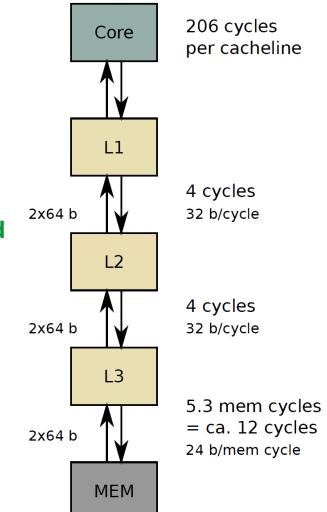

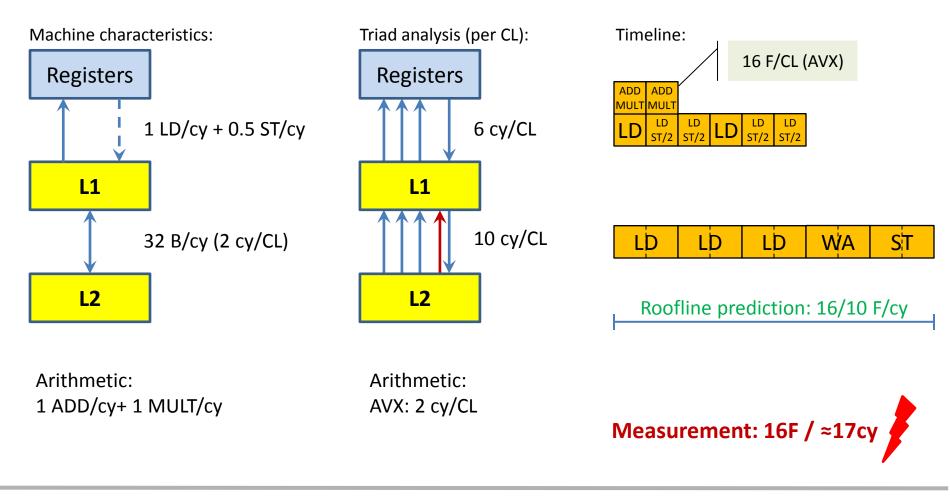

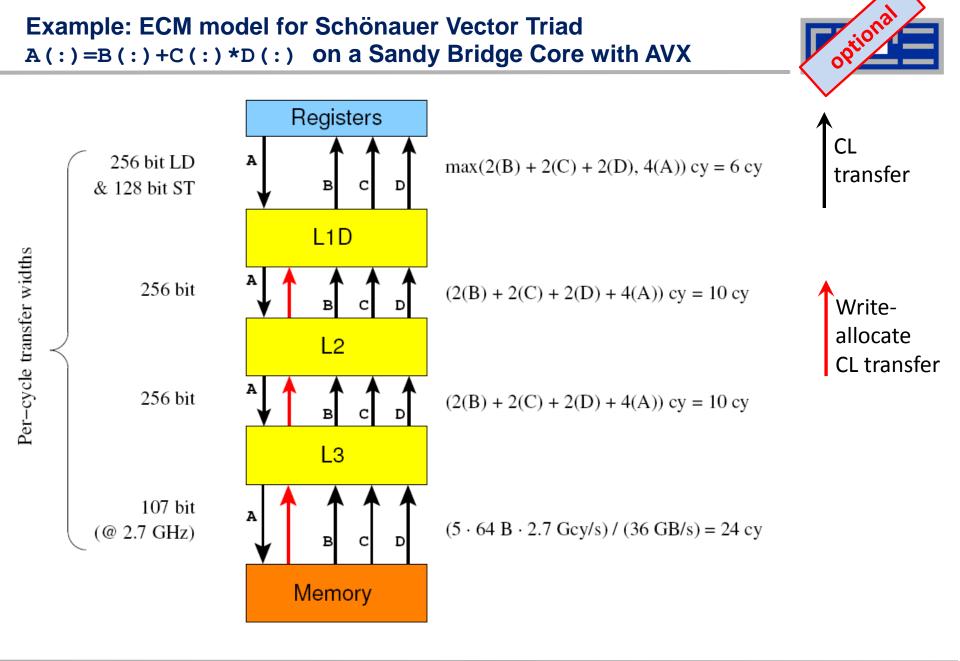

Example: Vector triad A(:)=B(:)+C(:)\*D(:) on a 2.7 GHz 8-core Sandy Bridge chip (AVX vectorized)

- *b*<sub>S</sub> = **40 GB/s**

- B<sub>c</sub> = (4+1) Words / 2 Flops = 2.5 W/F (including write allocate)

→ *I* = 0.4 F/W = 0.05 F/B

- $\rightarrow$  /  $\cdot$  b<sub>S</sub> = 2.0 GF/s (1.2 % of peak performance)

- P<sub>peak</sub> = 173 Gflop/s (8 FP units x (4+4) Flops/cy x 2.7 GHz)

- $P_{\text{max}}$ ? → Observe LD/ST throughput maximum of 1 AVX Load and ½ AVX store per cycle → 3 cy / 8 Flops →  $P_{\text{max}}$  = **57.6 Gflop/s** (33% peak)

- $P = \min(P_{\max}, I \cdot b_S) = \min(57.6, 2.0) \text{ GFlop/s}$ = 2.0 GFlop/s

(c) RRZE 2013

Example: Vector triad A(:)=B(:)+C(:)\*D(:) on a 1.05 GHz 60-core Intel Xeon Phi chip (vectorized)

- *b*<sub>S</sub> = **160 GB/s**

- B<sub>c</sub> = (4+1) Words / 2 Flops = 2.5 W/F (including write allocate)

→ *I* = 0.4 F/W = 0.05 F/B

- $\rightarrow$  /  $\cdot$  b<sub>S</sub> = 8.0 GF/s (0.8 % of peak performance)

- P<sub>peak</sub> = 1008 Gflop/s (60 FP units x (8+8) Flops/cy x 1.05 GHz)

- P<sub>max</sub>? → Observe LD/ST throughput maximum of 1 Load or 1 Store per cycle → 4 cy / 16 Flops → P<sub>max</sub> = 252 Gflop/s (25% of peak)

- $P = \min(P_{\max}, I \cdot b_S) = \min(252, 8.0) \text{ GFlop/s}$ = 8.0 GFlop/s

(c) RRZE 2013

# A not so simple Roofline example

in double precision on a 2.7 GHz Sandy Bridge socket @ "large" N

(c) RRZE 2013

## Plain scalar code, no SIMD

```

LOAD r1.0 ← 0

i ← 1

loop:

LOAD r2.0 ← a(i)

ADD r1.0 ← r1.0+r2.0

++i →? loop

result ← r1.0

```

$\rightarrow$  1/12 of ADD peak

# Scalar code, 3-way unrolling

```

LOAD r1.0 \leftarrow 0

LOAD r2.0 \leftarrow 0

LOAD r3.0 \leftarrow 0

i \leftarrow 1

```

#### loop:

| LOAD | r4.0        | ← | a(i)   |

|------|-------------|---|--------|

| LOAD | <b>r5.0</b> | ← | a(i+1) |

| LOAD | <b>r6.0</b> | ← | a(i+2) |

ADD r1.0  $\leftarrow$  r1.0+r4.0 ADD r2.0  $\leftarrow$  r2.0+r5.0 ADD r3.0  $\leftarrow$  r3.0+r6.0

```

i+=3 \rightarrow? loop

result \leftarrow r1.0+r2.0+r3.0

```

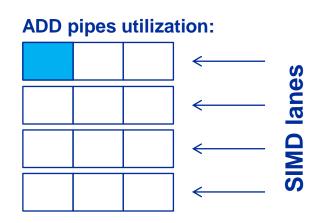

#### ADD pipes utilization:

#### $\rightarrow$ 1/4 of ADD peak

#### (c) RRZE 2013

# Applicable peak for the summation loop

**ADD** pipes utilization: SIMD-vectorized, 3-way unrolled LOAD  $[r1.0, ..., r1.3] \leftarrow [0,0]$ LOAD  $[r2.0, ..., r2.3] \leftarrow [0,0]$ LOAD  $[r3.0, ..., r3.3] \leftarrow [0,0]$ i ← 1  $\rightarrow$  ADD peak loop: LOAD  $[r4.0,...,r4.3] \leftarrow [a(i),...,a(i+3)]$ LOAD  $[r5.0,...,r5.3] \leftarrow [a(i+4),...,a(i+7)]$ LOAD  $[r6.0,...,r6.3] \leftarrow [a(i+8),...,a(i+11)]$ ADD r1  $\leftarrow$  r1+r4 ADD r2  $\leftarrow$  r2+r5 ADD r3  $\leftarrow$  r3+r6 i+=12 →? loop result  $\leftarrow$  r1.0+r1.1+...+r3.2+r3.3

# ... on the example of do i=1,N; s=s+a(i); enddo

(c) RRZE 2013

- There is a clear concept of "work" vs. "traffic"

- "work" = flops, updates, iterations...

- "traffic" = required data to do "work"

- Attainable bandwidth of code = input parameter! Determine effective bandwidth via simple streaming benchmarks to model more complex kernels and applications

- Data transfer and core execution overlap perfectly!

- Slowest data path is modeled only; all others are assumed to be infinitely fast

- If data transfer is the limiting factor, the bandwidth of the slowest data path can be utilized to 100% ("saturation")

- Latency effects are ignored, i.e. perfect streaming mode

# **Bandwidth-bound (simple case)**

- Accurate traffic calculation (writeallocate, strided access, ...)

- Practical ≠ theoretical BW limits

- Erratic access patterns

# **Core-bound (may be complex)**

- Multiple bottlenecks: LD/ST, arithmetic, pipelines, SIMD, execution ports

- Limit is linear in # of cores

### (c) RRZE 2013

# **Complexities of in-core execution**

#### Multiple bottlenecks:

- L1 Icache (LD/ST) bandwidth

- Decode/retirement throughput

- Port contention (direct or indirect)

- Arithmetic pipeline stalls (dependencies)

- Overall pipeline stalls (branching)

- L1 Dcache bandwidth (LD/ST throughput)

- Scalar vs. SIMD execution

Register pressure

. . .

Alignment issues

(c) RRZE 2013

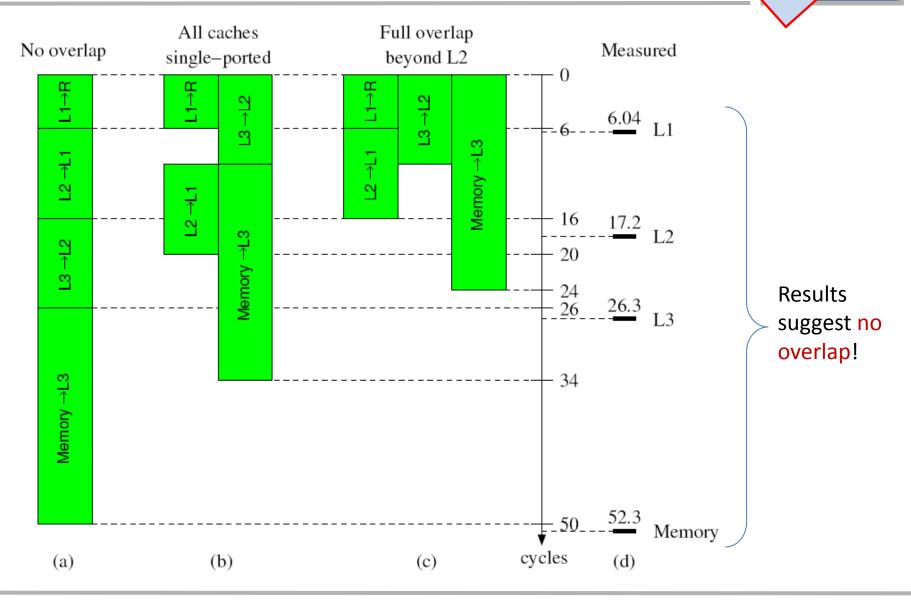

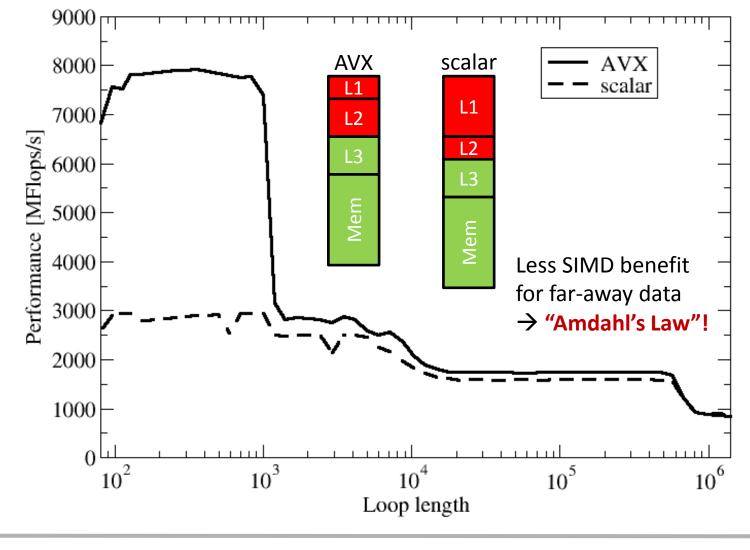

#### Shortcomings of the roofline model

- Saturation effects in multicore chips are not explained

- Reason: "saturation assumption"

- Cache line transfers and core execution do sometimes not overlap perfectly

- Only increased "pressure" on the memory interface can saturate the bus

→ need more cores!

- ECM model gives more insight (see later)

#### (c) RRZE 2013

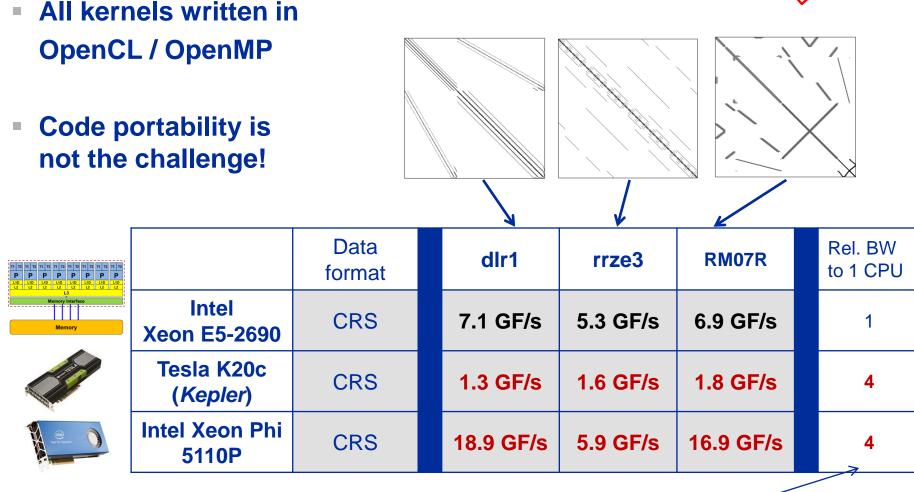

#### Case study: OpenMP-parallel sparse matrix-vector multiplication (part 2)

Putting Roofline to use where it should not work

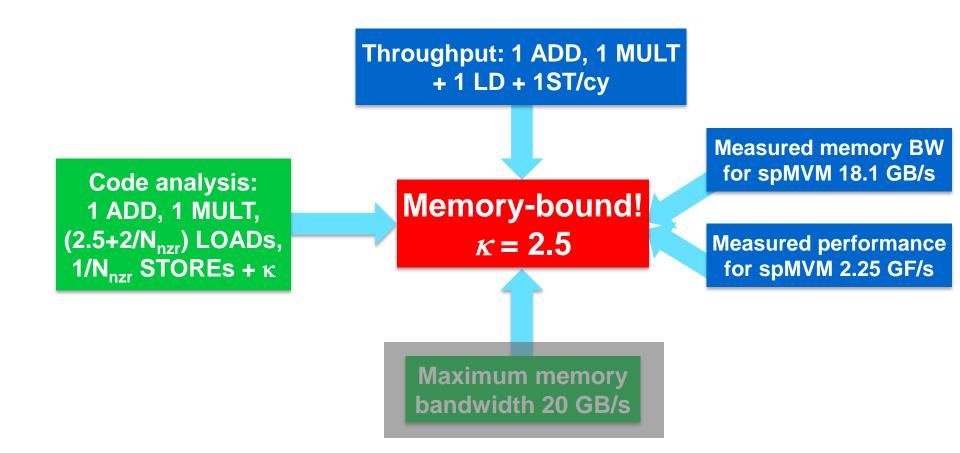

#### Example: SpMVM node performance model

Sparse MVM in double precision w/ CRS data storage:

do i = 1,

$$N_r$$

do j = row\_ptr(i), row\_ptr(i+1) - 1

$C(i) = C(i) + val(j) * B(col_idx(j))$

enddo

enddo

DP CRS comp. intensity

*κ* quantifies extra traffic for loading RHS more than once

$$I_{\text{CRS}} = \frac{2}{12 + 24/N_{\text{nzr}} + \kappa} \frac{\text{Flops}}{\text{Byte}}$$

$$= \left(6 + \frac{12}{N_{\text{nzr}}} + \frac{\kappa}{2}\right)^{-1} \frac{\text{Flops}}{\text{Byte}}$$

- Expected performance =  $b_{\rm S} \times I_{\rm CRS}$

- Determine  $\kappa$  by measuring performance and actual memory bandwidth

- Maximum memory BW may not be achieved with spMVM

#### Analysis for HMeP matrix on Nehalem EP socket

- BW used by spMVM kernel  $b = 18.1 \text{ GB/s} \rightarrow$  should get  $\approx 2.66 \text{ Gflop/s}$  spMVM performance if  $\kappa = 0$

- Measured spMVM performance = 2.25 Gflop/s

- Solve 2.25 Gflop/s =  $b \times I_{CRS}$  for  $\kappa \approx 2.5$

→ 37.5 extra bytes per row

→ RHS is loaded 6 times from memory

→ about 33% of BW goes into RHS

Conclusion: Even if the roofline model does not work 100%, we can still learn something from the deviations

#### ... on the example of spMVM with HMeP matrix

#### (c) RRZE 2013

## DEMO

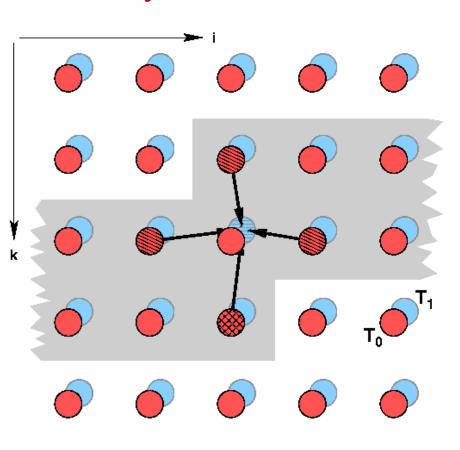

#### Case study: A 3D Jacobi smoother

The basics in two dimensions Roofline performance analysis and modeling

#### A Jacobi smoother

### - Laplace equation in 2D: $\Delta \Phi = 0$

## Solve with Dirichlet boundary conditions using Jacobi iteration scheme:

```

double precision, dimension(0:imax+1,0:kmax+1,0:1) :: phi

integer :: t0,t1

t0 = 0; t1 = 1

do it = 1, itmax ! choose suitable number of sweeps

do k = 1, kmax

Re-use when computing

do i = 1, imax

phi(i+2,k,t1)

! four flops, one store, four loads

phi(i,k,t1) = (phi(i+1,k,t0) + phi(i-1,k,t0))

+ phi(i,k+1,t0) + phi(i,k-1,t0) ) * 0.25

enddo

enddo

Naive balance (incl. write allocate):

! swap arrays

0 ; t0=t1 ; t1=i

phi(:,:,t0):3 LD +

enddo

phi(:,:,t1):1 ST+1LD

\rightarrow B<sub>c</sub> = 5 W / 4 FLOPs = 1.25 W / F

WRITE ALLOCATE:

LD + ST phi(i,k,t1)

```

(c) RRZE 2013

## Modern cache subsystems may further reduce memory traffic → "layer conditions"

If cache is large enough to hold at least 2 rows (shaded region): Each phi(:,:,t0) is loaded once from main memory and re-used 3 times from cache:

phi(:,:,t0): 1 LD + phi(:,:,t1): 1 ST+ 1LD  $\rightarrow B_c = 3 W / 4 F = 0.75 W / F$

If cache is too small to hold one row: phi(:,:,t0): 2 LD + phi(:,:,t1): 1 ST + 1LD $\rightarrow B_c = 5 W / 4 F = 1.25 W / F$

#### Alternative implementation ("Macho FLOP version")

- MFlops/sec increases by 7/4 but time to solution remains the same

- Better metric (for many iterative stencil schemes): Lattice Site Updates per Second (LUPs/sec)

2D Jacobi example: Compute LUPs/sec metric via

$$P[LUPs / s] = \frac{it_{\max} \cdot i_{\max} \cdot k_{\max}}{T_{\text{wall}}}$$

#### (c) RRZE 2013

#### $2D \rightarrow 3D$

#### 3D sweep:

- Best case balance: 1 LD phi(i,j,k+1,t0) 1 ST + 1 write allocate phi(i,j,k,t1) 6 flops  $\rightarrow$  B<sub>c</sub> = 0.5 W/F (24 bytes/LUP)

- No 2-layer condition but 2 rows fit: B<sub>c</sub> = 5/6 W/F (40 bytes/LUP)

- Worst case (2 rows do not fit):

B<sub>c</sub> = 7/6 W/F (56 bytes/LUP)

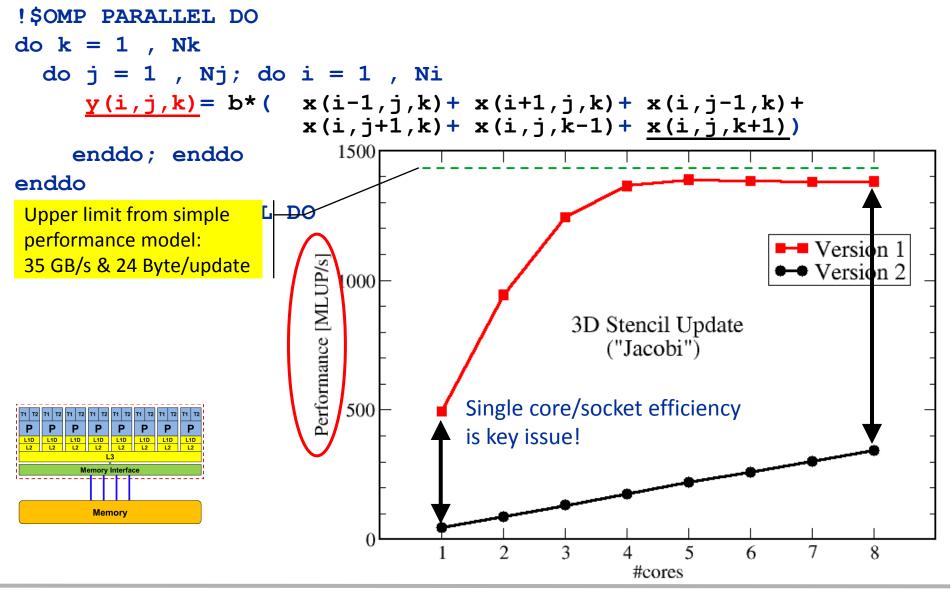

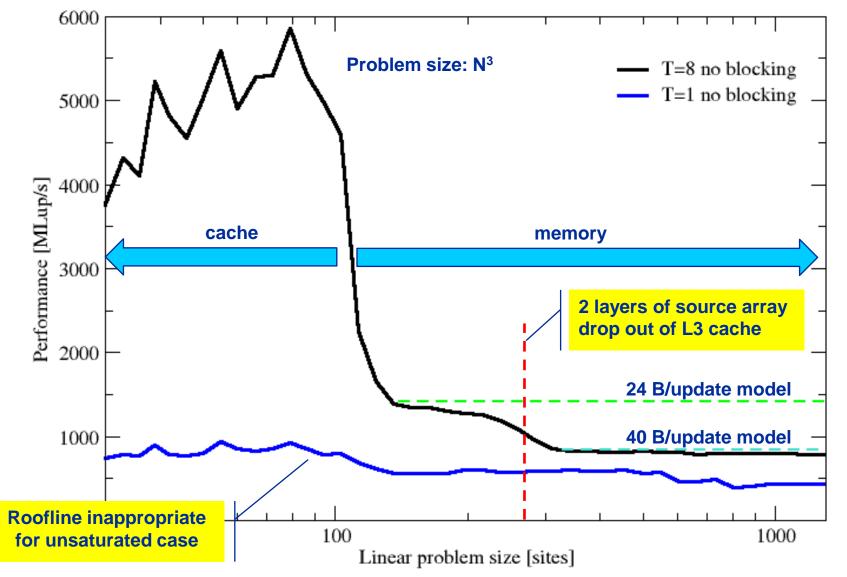

#### **3D Jacobi solver**

Performance of vanilla code on one Sandy Bridge chip (8 cores)

(c) RRZE 2013

- We have made sense of the memory-bound performance vs. problem size

- "Layer conditions" lead to predictions of code balance

- Achievable memory bandwidth is input parameter

- The model works only if the bandwidth is "saturated"

- In-cache modeling is more involved

Optimization == reducing the code balance by code transformations

See below

#### **Data access optimizations**

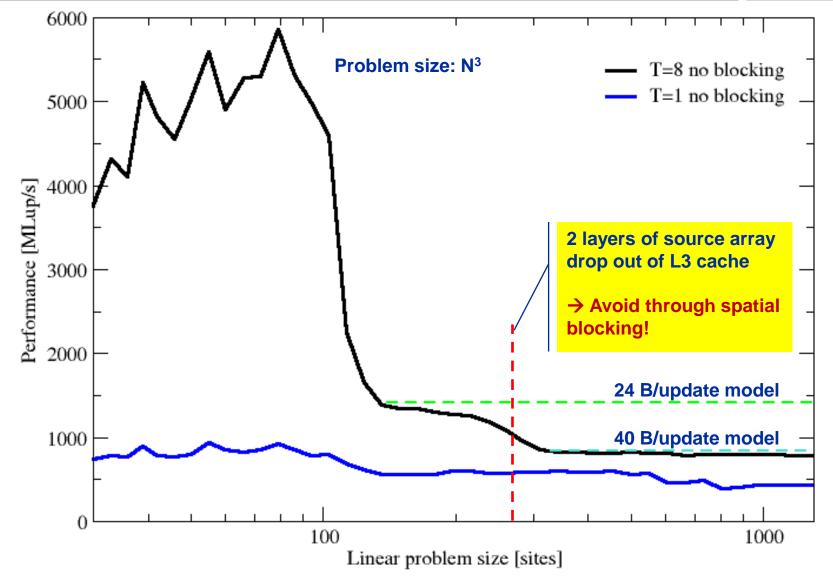

#### Case study: Optimizing the 3D Jacobi solver

#### Remember the 3D Jacobi solver on Sandy Bridge?

(c) RRZE 2013

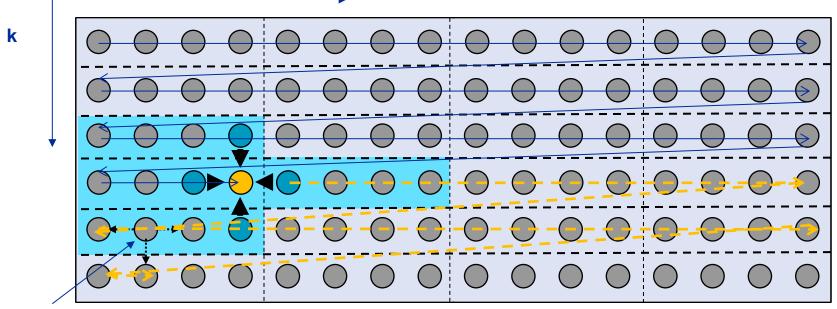

## **FFEE**

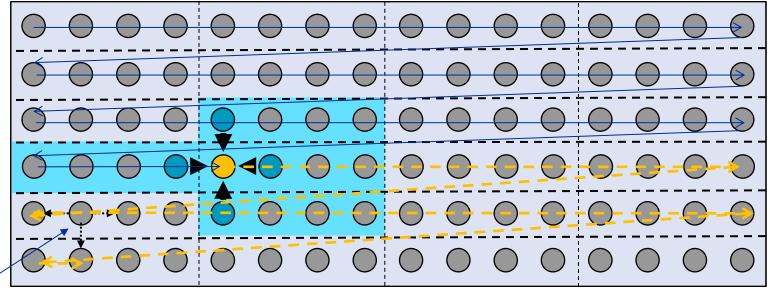

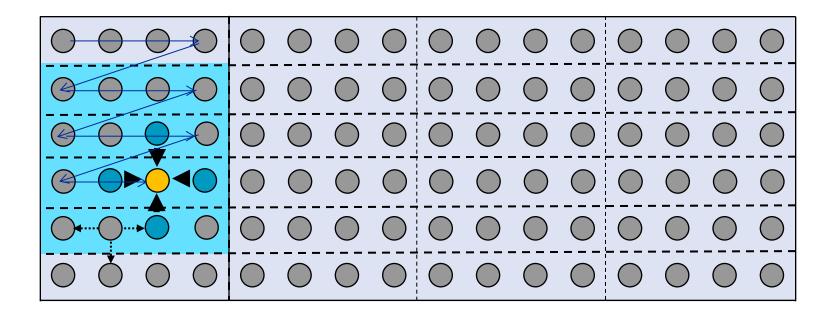

#### Assumptions:

- cache can hold 32 elements (16 for each array)

- Cache line size is 4 elements

- Perfect eviction strategy for source array

This element is needed for three more updates; but 29 updates happen before this element is used for the last time

#### (c) RRZE 2013

#### Assumptions:

- cache can hold 32 elements (16 for each array)

- Cache line size is 4 elements

- Perfect eviction strategy for source array

This element is needed for three more updates but has been evicted

#### (c) RRZE 2013

- Divide system into blocks

- Update block after block

- Same performance as if three complete rows of the systems fit into cache

Some excess traffic at boundaries may be unavoidable

```

(c) RRZE 2013

```

- Spatial blocking reorders traversal of data to account for the data update rule of the code

- →Elements stay sufficiently long in cache to be fully reused

## → Spatial blocking improves temporal locality!

(Continuous access in inner loop ensures spatial locality)

This element remains in cache until it is fully used (only 6 updates happen before last use of this element)

#### (c) RRZE 2013

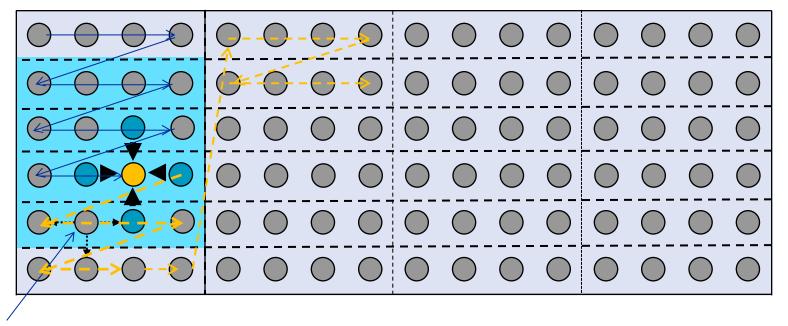

#### Jacobi iteration (3D): Spatial blocking **Implementation:** loop over i-blocks do ioffset=1,imax,iblock loop over j-blocks do joffset=1,jmax,jblock do k=1, kmaxdo j=joffset, min(jmax,joffset+jblock-1) do i=ioffset, min(imax,ioffset+iblock-1) phi(i,j,k,t1) = (phi(i-1,j,k,t0)+phi(i+1,j,k,t0))+ ... + phi(i,j,k-1,t0)+phi(i,j,k+1,t0) )/6.d0 enddo enddo enddo enddo $2 \cdot iblock \cdot jblock \cdot 8 byte \cdot #cores < (cache size)/2$ enddo

#### Guidelines:

- Blocking of inner loop levels (traversing continuously through main memory)

- Blocking sizes large enough to fulfill "layer condition"

- Cache size is a hard limit!

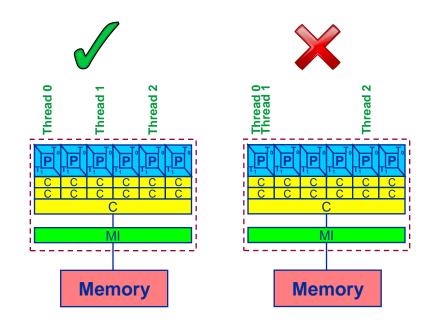

- Blocking loops may have some impact on ccNUMA page placement

#### (c) RRZE 2013

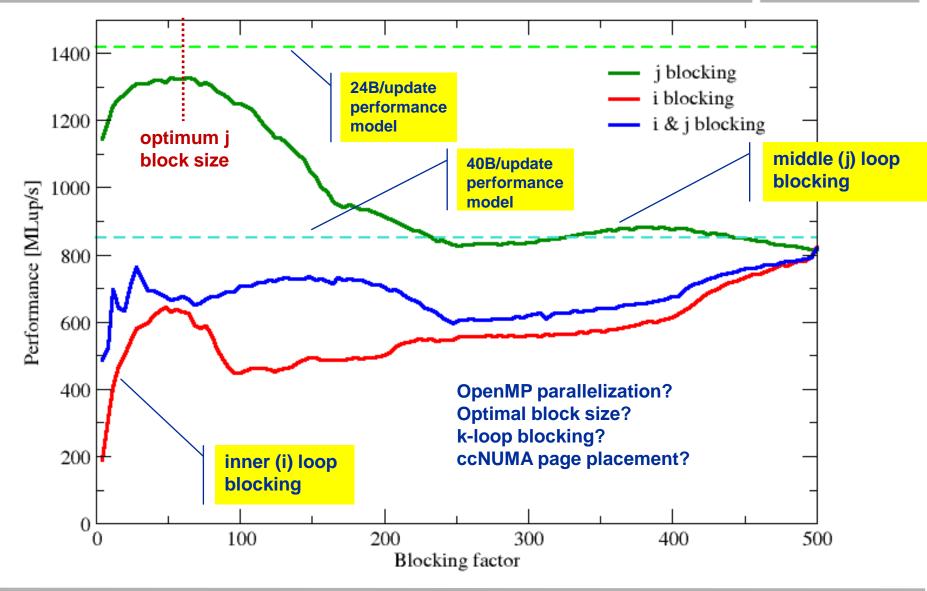

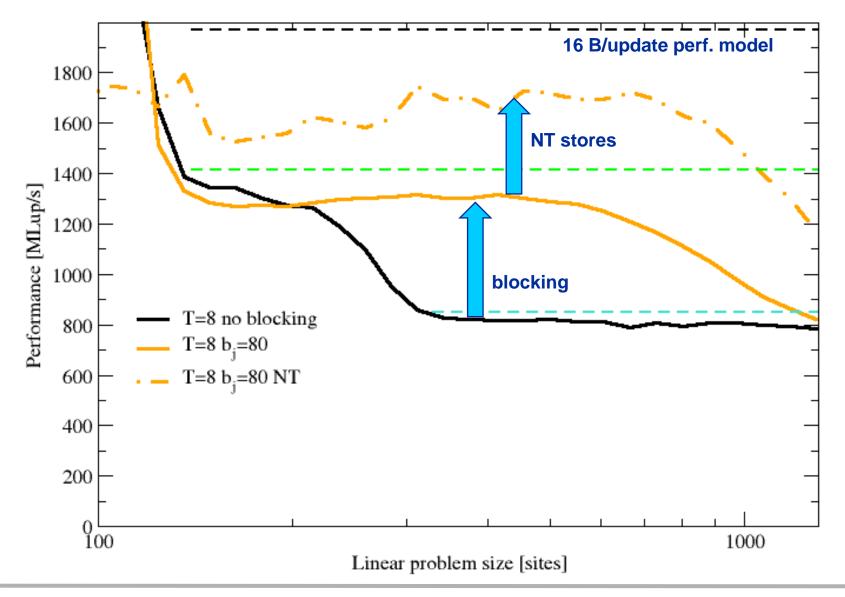

#### 3D Jacobi solver (problem size 500<sup>3</sup>)

Blocking different loop levels (8 cores Sandy Bridge)

(c) RRZE 2013

## Intel x86: NT stores are packed SIMD stores with 16-byte aligned address

- Sometimes hard to apply

- AMD x86: Scalar NT stores without alignment restrictions available

#### Options for using NT stores

- Let the compiler decide  $\rightarrow$  unreliable

- Use compiler options

- Intel: -opt-streaming-stores never|always|auto

- Use compiler directives

- Intel: !DEC\$ vector [non]temporal

- Cray: !DIR\$ LOOP\_INFO cache[\_nt](...)

- Compiler must be able to "prove" that the use of SIMD and NT stores is "safe"!

- "line update kernel" concept: Make critical loop its own subroutine

#### Line update kernel (separate compilation unit or -fno-inline):

```

subroutine jacobi_line(d,s,top,bottom,front,back,n)

integer :: n,i,start

double precision, dimension(*) :: d,s,top,bottom,front,back

double precision, parameter :: oos=1.d0/6.d0

!DEC$ VECTOR NONTEMPORAL

do i=2,n-1

d(i) = oos*(s(i-1)+s(i+1)+top(i)+bottom(i)+front(i)+back(i))

enddo

end subroutine

```

#### Main loop:

enddo enddo

#### 3D Jacobi solver

#### Spatial blocking + nontemporal stores

(c) RRZE 2013

- "What part of the data comes from where" is a crucial question

- Avoiding slow data paths == re-establishing the most favorable layer condition

- Improved code showed the speedup predicted by the model

- Optimal blocking factor can be estimated

- Be guided by the cache size the layer condition

- No need for exhaustive scan of "optimization space"

### Agenda

- Preliminaries

- Introduction to multicore architecture

- Cores, caches, chips, sockets, ccNUMA, SIMD

- LIKWID tools

- Microbenchmarking for architectural exploration

- Streaming benchmarks: throughput mode

- Streaming benchmarks: work sharing

- Roadblocks for scalability: Saturation effects and OpenMP overhead

- Lunch break

- Node-level performance modeling

- The Roofline Model

- Case study: 3D Jacobi solver and model-guided optimization

- Optimal resource utilization

- SIMD parallelism

- ccNUMA

- Simultaneous multi-threading (SMT)

- Optional: The ECM multicore performance model

#### **Optimal utilization of parallel resources**

Exploiting SIMD parallelism and reading assembly code Simultaneous multi-threading (SMT): facts & myths Programming for ccNUMA memory architecture

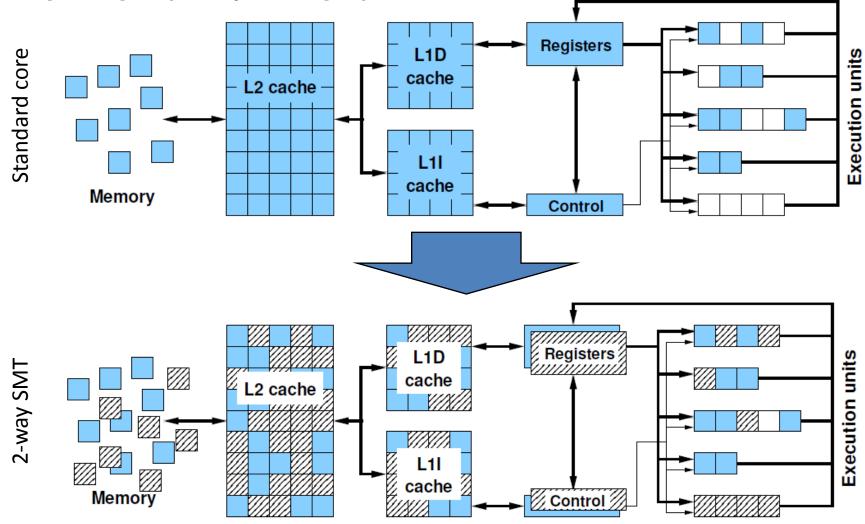

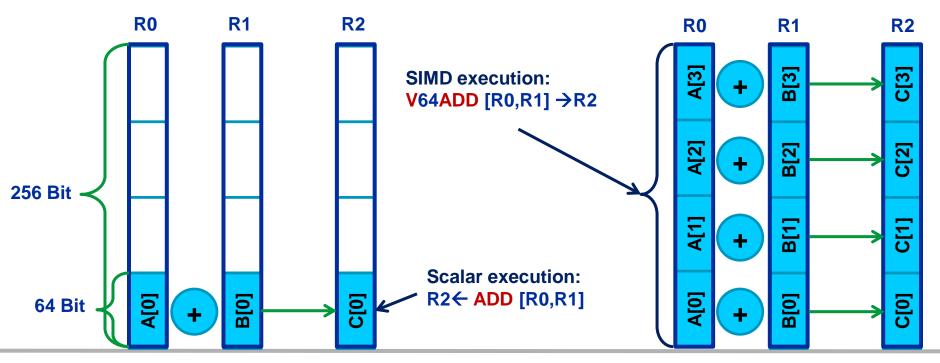

- Single Instruction Multiple Data (SIMD) operations allow the concurrent execution of the same operation on "wide" registers.

- x86 SIMD instruction sets:

- SSE: register width = 128 Bit  $\rightarrow$  2 double precision floating point operands

- AVX: register width = 256 Bit  $\rightarrow$  4 double precision floating point operands

- Adding two registers holding double precision floating point operands

(c) RRZE 2013

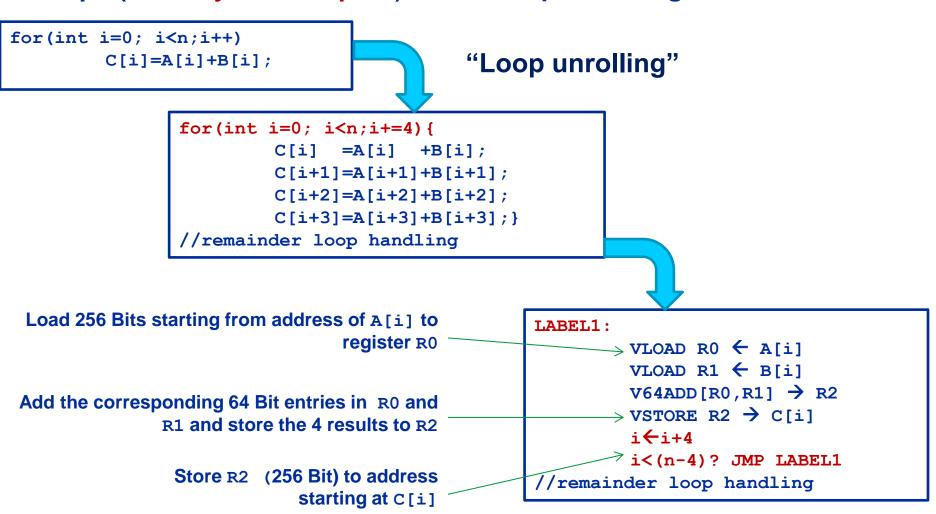

#### **SIMD** processing – Basics

#### Steps (done by the compiler) for "SIMD processing"

(c) RRZE 2013

#### No SIMD vectorization for loops with data dependencies:

for(int i=0; i<n;i++)

A[i]=A[i-1]\*s;</pre>

Pointer aliasing" may prevent SIMDfication

```

void scale_shift(double *A, double *B, double *C, int n) {

for(int i=0; i<n; ++i)

C[i] = A[i] + B[i];

}</pre>

```

• C/C++ allows that  $\mathbf{A} \rightarrow \&C[-1]$  and  $\mathbf{B} \rightarrow \&C[-2]$  $\rightarrow C[i] = C[i-1] + C[i-2]$ : dependency  $\rightarrow No SIMD$

If "pointer aliasing" is not used, tell it to the compiler, e.g. use -fno-alias switch for Intel compiler → SIMD

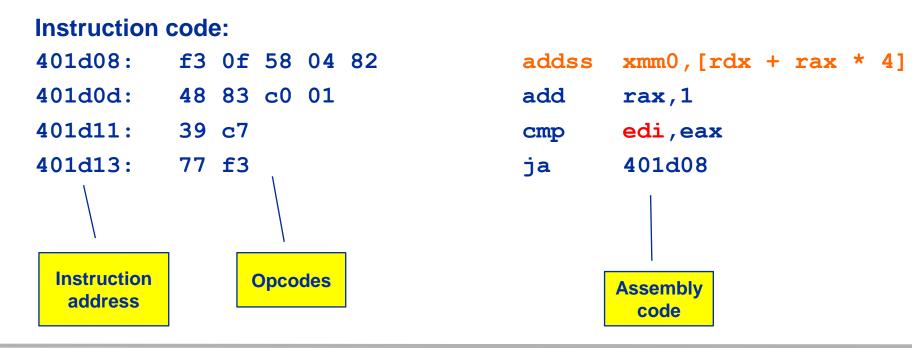

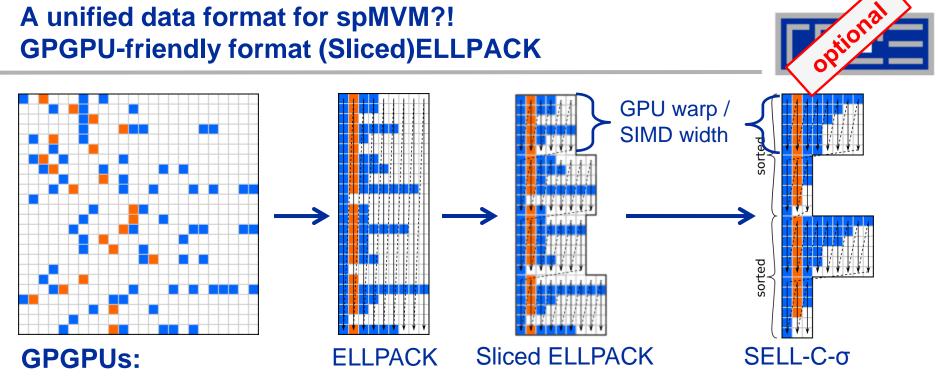

## Reading x86 assembly code and exploting SIMD parallelism

Understanding SIMD execution by inspecting assembly code SIMD vectorization how-to Intel compiler options and features for SIMD Sparse MVM part 3: SIMD-friendly data layouts

#### Why check the assembly code?

- Sometimes the only way to make sure the compiler "did the right thing"

- Example: "LOOP WAS VECTORIZED" message is printed, but Loads & Stores may still be scalar!

- Get the assembler code (Intel compiler): icc -S -O3 -xHost triad.c -o a.out

- Disassemble Executable:

- objdump -d ./a.out | less

#### The x86 ISA is documented in:

Intel Software Development Manual (SDM) 2A and 2B AMD64 Architecture Programmer's Manual Vol. 1-5

```

16 general Purpose Registers (64bit):

rax, rbx, rcx, rdx, rsi, rdi, rsp, rbp, r8-r15

alias with eight 32 bit register set:

eax, ebx, ecx, edx, esi, edi, esp, ebp

```

#### Floating Point SIMD Registers:

| xmm0-xmm15 | SSE (128bit) | alias with 256-bit registers |

|------------|--------------|------------------------------|

| ymm0-ymm15 | AVX (256bit) |                              |

# SIMD instructions are distinguished by:AVX (VEX) prefix:vOperation:mul, add, movModifier:nontemporal (nt), unaligned (u), aligned

| Modifier:  | nontemporal (nt), unaligned (u), aligned (a), high (h) |

|------------|--------------------------------------------------------|

| Width:     | scalar (s), packed (p)                                 |

| Data type: | single (s), double (d)                                 |

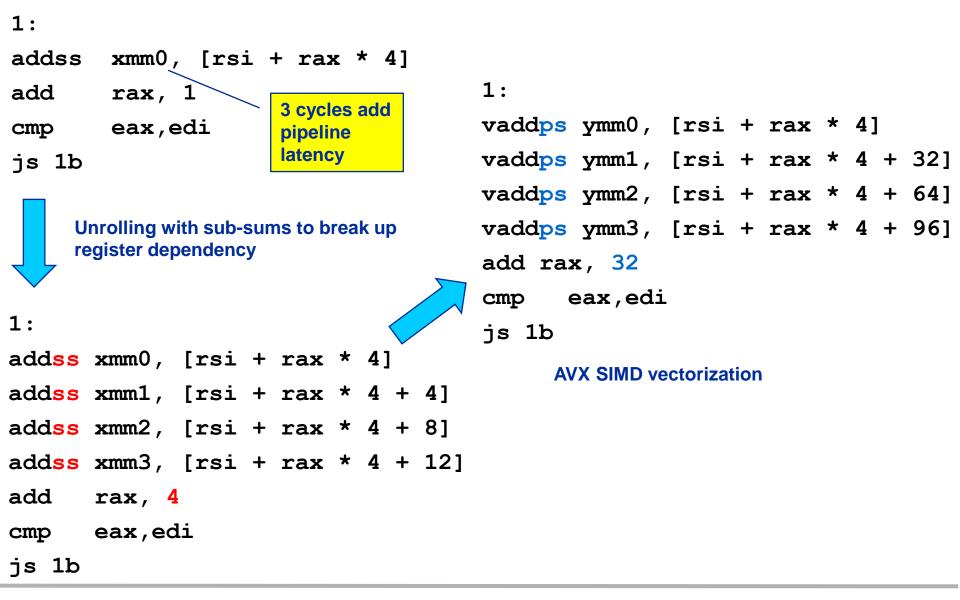

Case Study: Simplest code for the summation of the elements of a vector (single precision)

```

float sum = 0.0;

```

```

for (int j=0; j<size; j++) {

sum += data[j];

}</pre>

```

To get object code use objdump -d on object file or executable or compile with -S

(c) RRZE 2013

#### Summation code (single precision): Improvements

#### **Alternatives:**

- The compiler does it for you (but: aliasing, alignment, language)

- Compiler directives (pragmas)

- Alternative programming models for compute kernels (OpenCL, ispc)

- Intrinsics (restricted to C/C++)

- Implement directly in assembler

#### To use intrinsics the following headers are available:

- xmmintrin.h (SSE)

- pmmintrin.h (SSE2)

- immintrin.h (AVX)

- x86intrin.h (all instruction set extensions)

- See next slide for an example

# Example: array summation using C intrinsics (SSE, single precision)

\_m128 sum0, sum1, sum2, sum3;

\_\_m128 t0, t1, t2, t3;

float scalar\_sum;

- sum0 = \_mm\_setzero\_ps();

- sum1 = \_mm\_setzero\_ps();

- sum2 = mm setzero ps();

- sum3 = \_mm\_setzero\_ps();

for (int j=0; j<size; j+=16) {

t0 = \_mm\_loadu\_ps(data+j);

t1 = \_mm\_loadu\_ps(data+j+4);

t2 = \_mm\_loadu\_ps(data+j+8);

t3 = \_mm\_loadu\_ps(data+j+12);

sum0 = \_mm\_add\_ps(sum0, t0);

sum1 = \_mm\_add\_ps(sum1, t1);

sum2 = \_mm\_add\_ps(sum2, t2);

sum3 = \_mm\_add\_ps(sum3, t3);

}</pre>

- sum0 = \_mm\_add\_ps(sum0, sum1); sum0 = \_mm\_add\_ps(sum0, sum2); sum0 = \_mm\_add\_ps(sum0, sum3);

- sum0 = \_mm\_hadd\_ps(sum0, sum0);

- sum0 = \_mm\_hadd\_ps(sum0, sum0);

- \_mm\_store\_ss(&scalar\_sum, sum0);

(c) RRZE 2013

#### **Example: array summation from intrinsics, instruction code**

| 14: | 0f 57 c9          | xorps  | %xmm1,%xmm1                                                 |           |

|-----|-------------------|--------|-------------------------------------------------------------|-----------|

| 17: | 31 c0             | xor    | %eax,%eax                                                   |           |

| 19: | 0f 28 d1          | movaps | %xmm1,%xmm2                                                 |           |

| 1c: | 0f 28 c1          | movaps | %xmm1,%xmm0                                                 |           |

| 1f: | 0f 28 d9          | movaps | %xmm1,%xmm3                                                 |           |

| 22: | 66 Of 1f 44 00 00 | nopw   | 0x0(%rax,%rax,1)                                            |           |

| 28: | 0f 10 3e          | movups | (%rsi),%xmm7                                                |           |

| 2b: | 0f 10 76 10       | movups | 0x10(%rsi),%xmm6                                            |           |

| 2f: | 0f 10 6e 20       | movups | 0x20(%rsi),%xmm5                                            |           |

| 33: | 0f 10 66 30       | movups | 0x30(%rsi),%xmm4                                            |           |

| 37: | 83 c0 10          | add    | \$0x10,%eax                                                 |           |

| 3a: | 48 83 c6 40       | add    | \$0x40,%rsi                                                 |           |

| 3e: | 0f 58 df          | addps  | %xmm7,%xmm3                                                 |           |

| 41: | 0f 58 c6          | addps  | %xmm6,%xmm0                                                 |           |

| 44: | 0f 58 d5          | addps  | %xmm5,%xmm2                                                 |           |

| 47: | 0f 58 cc          | addps  | %xmm4,%xmm1                                                 |           |

| 4a: | 39 c7             | cmp    | <pre>%eax,%edi</pre>                                        |           |

| 4c: | 77 da             | ja     | <pre>28 <compute_sum_sse+0x18></compute_sum_sse+0x18></pre> | Loop body |

| 4e: | 0f 58 c3          | addps  | %xmm3,%xmm0                                                 |           |

| 51: | 0f 58 c2          | addps  | %xmm2,%xmm0                                                 |           |

| 54: | 0f 58 c1          | addps  | %xmm1,%xmm0                                                 |           |

| 57: | f2 0f 7c c0       | haddps | %xmm0,%xmm0                                                 |           |

| 5b: | f2 0f 7c c0       | haddps | %xmm0,%xmm0                                                 |           |

| 5f: | c3                | retq   |                                                             |           |

|     |                   |        |                                                             |           |

#### (c) RRZE 2013

- Intel compiler will try to use SIMD instructions when enabled to do so

- "Poor man's vector computing"

- Compiler can emit messages about vectorized loops (not by default):

```

plain.c(11): (col. 9) remark: LOOP WAS VECTORIZED.

```

- Use option -vec\_report3 to get full compiler output about which loops were vectorized and which were not and why (data dependencies!)

- Some obstructions will prevent the compiler from applying vectorization even if it is possible

- You can use source code directives to provide more information to the compiler

- The compiler will vectorize starting with -02.

- To enable specific SIMD extensions use the –x option:

```

-xSSE2 vectorize for SSE2 capable machines

Available SIMD extensions:

SSE2, SSE3, SSE3, SSE4.1, SSE4.2, AVX

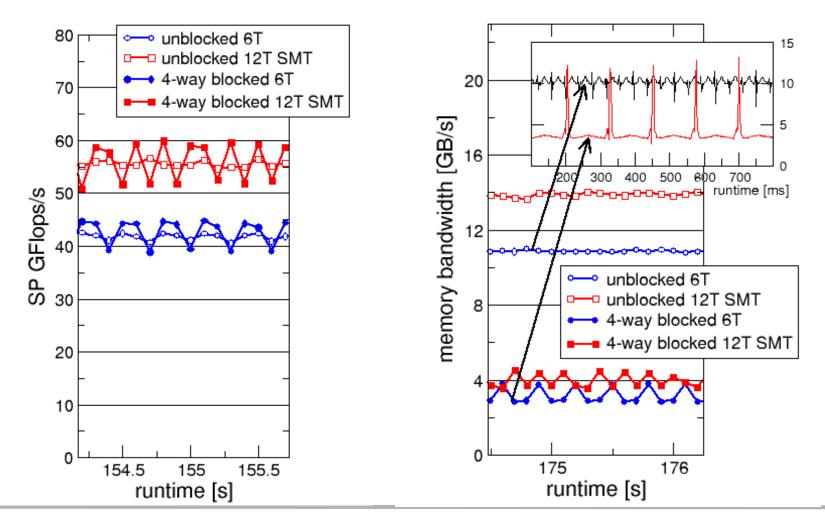

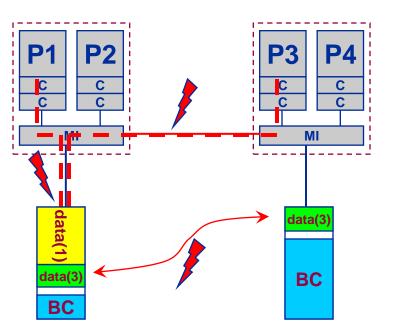

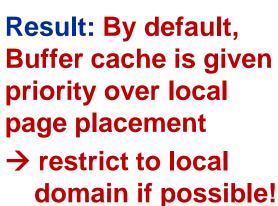

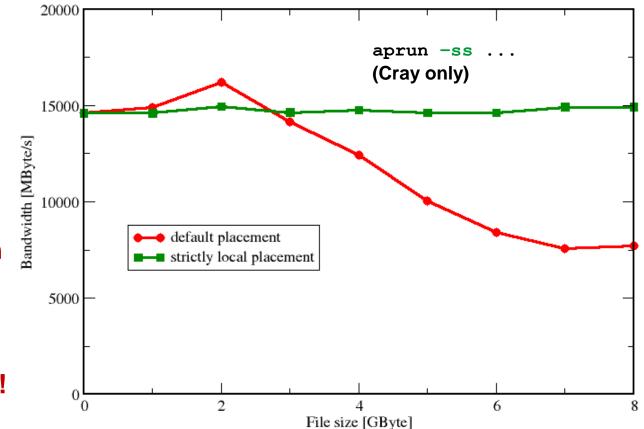

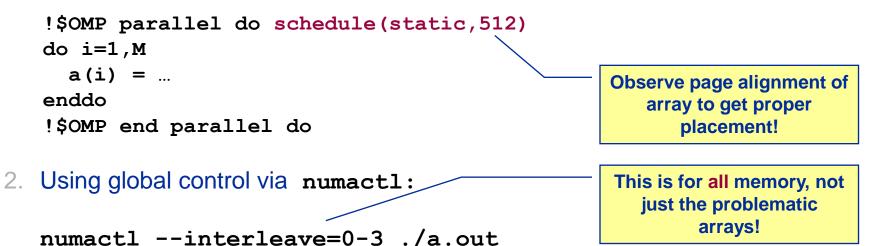

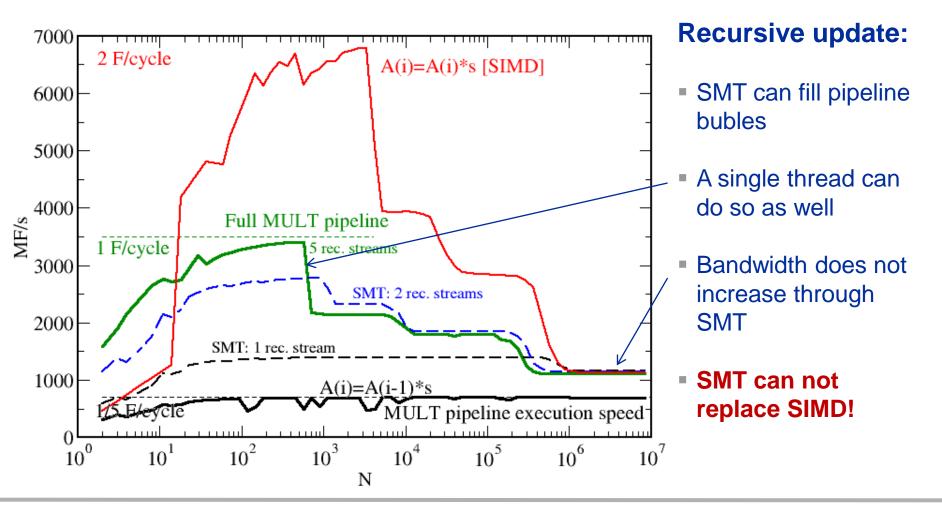

```