# Node-Level Performance Engineering https://tiny.cc/NLPE-SC23

Georg Hager, Thomas Gruber, Gerhard Wellein Erlangen National High Performance Computing Center (NHR@FAU)

SC23 Full-Day Tutorial Monday, November 13, 2023

Friedrich-Alexander-Universität Erlangen-Nürnberg

# **Node-Level Performance Engineering**

### https://tiny.cc/NLPE-SC23

Georg Hager, Thomas Gruber, Gerhard Wellein Erlangen National High Performance Computing Center (NHR@FAU)

SC23 Full-Day Tutorial Monday, November 13, 2023

# Agenda

#### Part I

- Introduction to compute node architecture

- Performance tools 1: topology and affinity

- Microbenchmarking as a tool

- Demo

- Introduction to the Roofline model

- Performance tools 2: hardware performance counters

- Demo

#### Part II

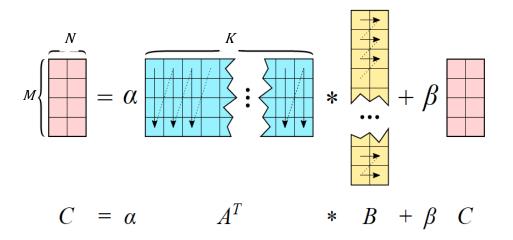

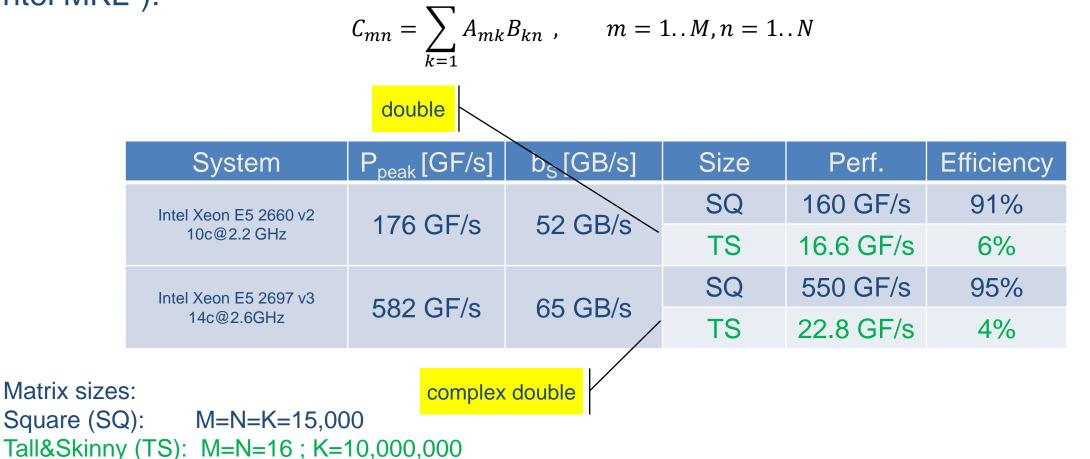

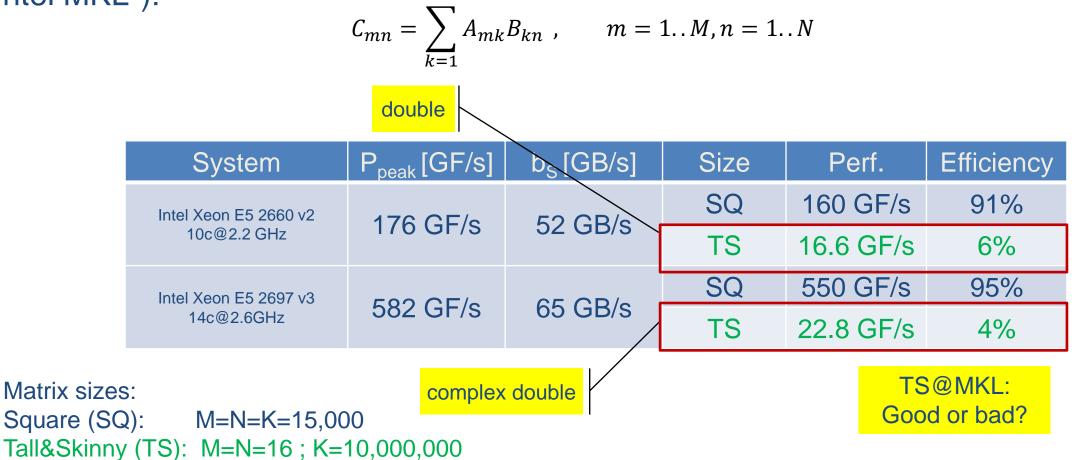

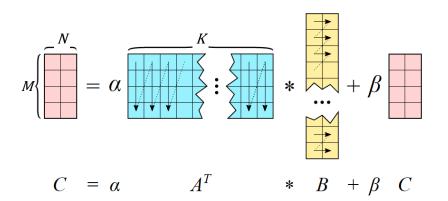

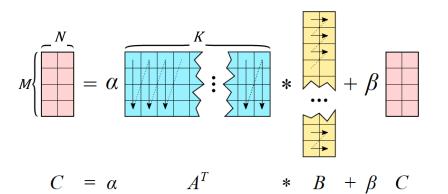

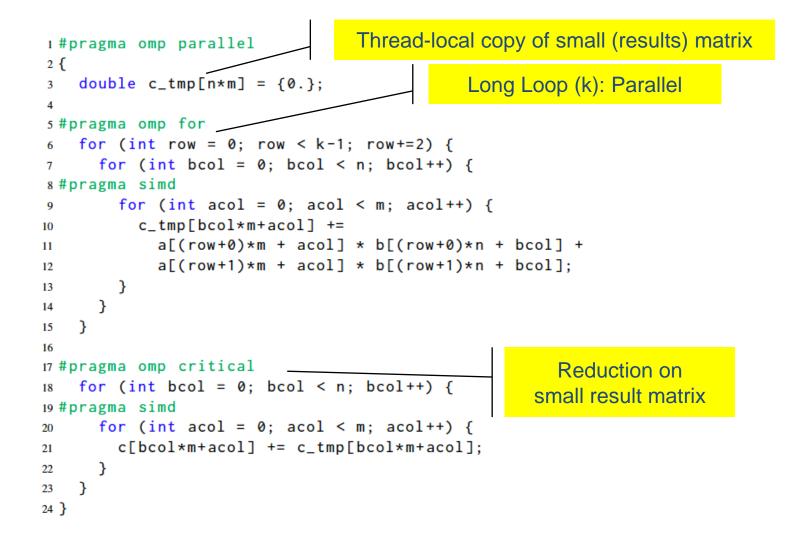

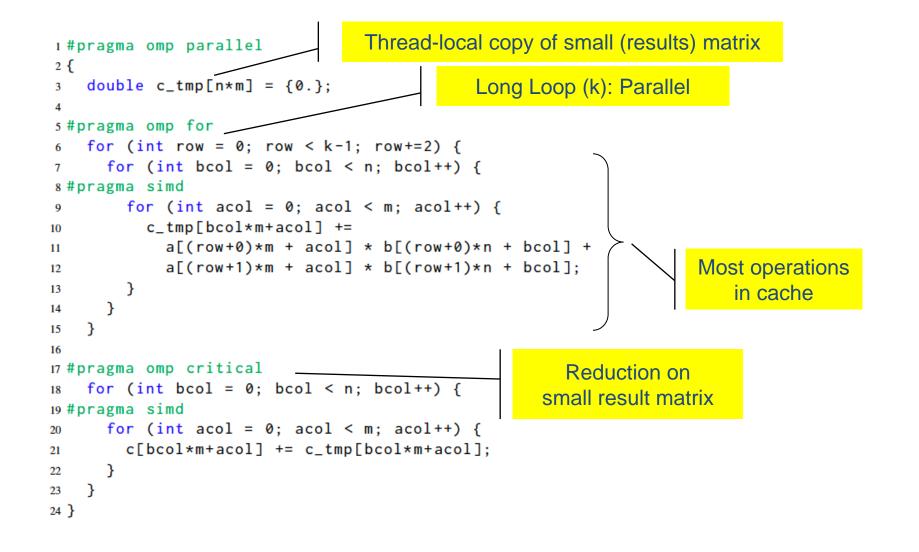

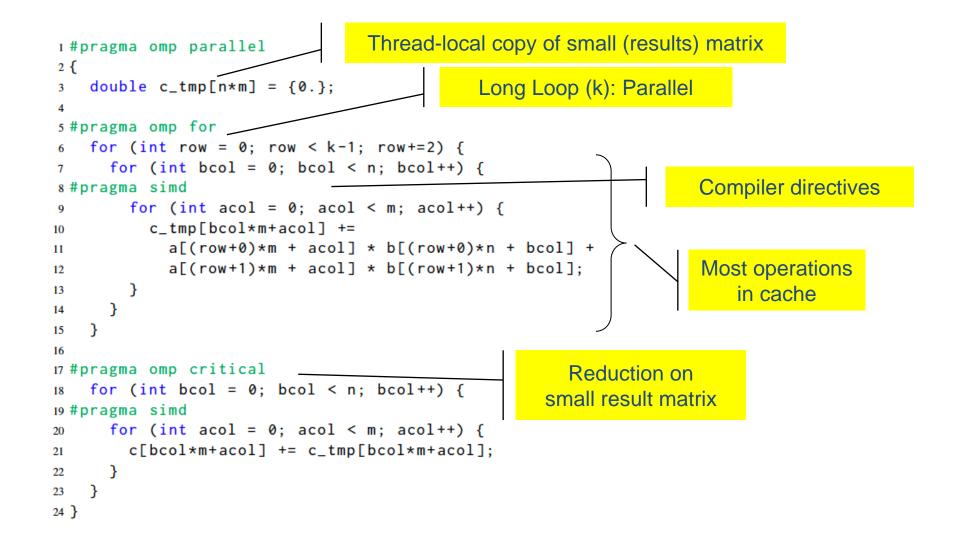

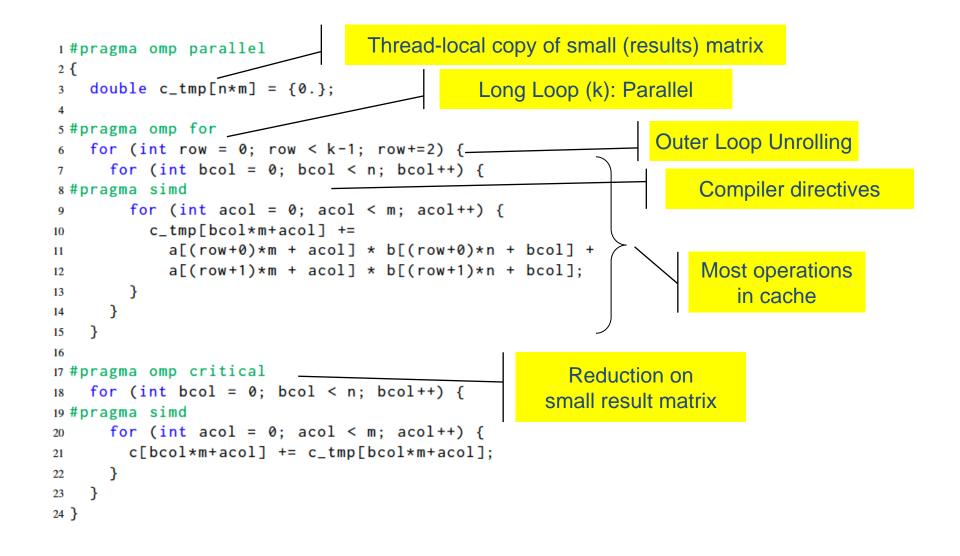

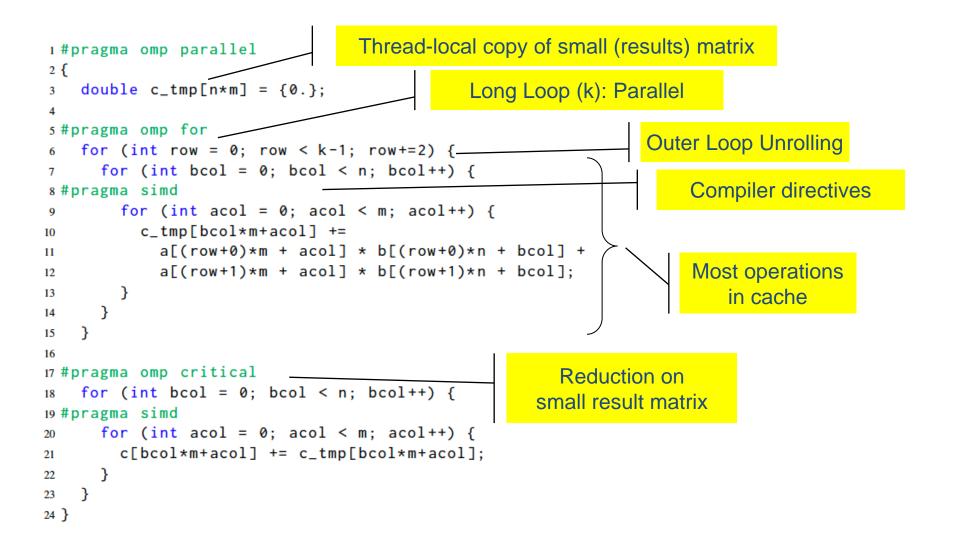

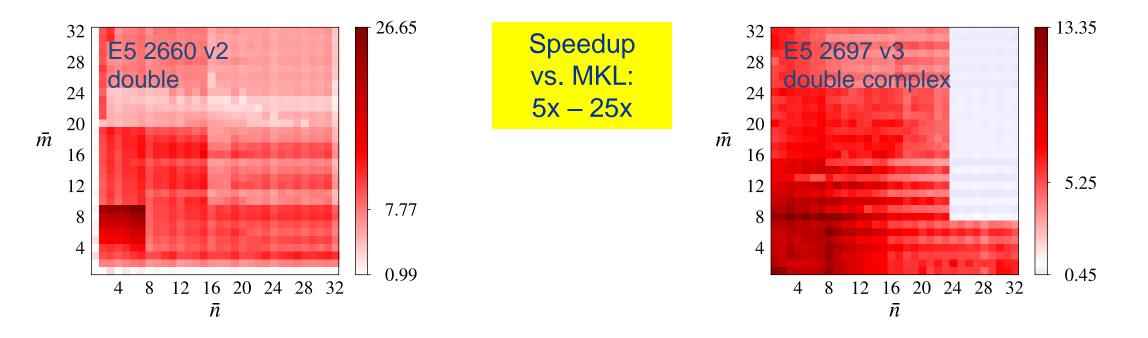

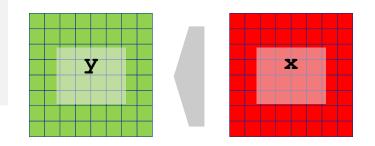

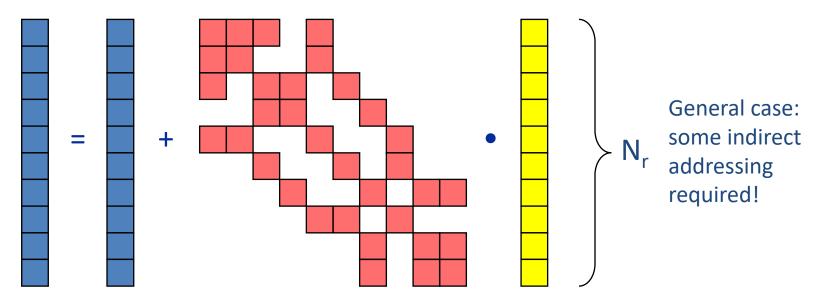

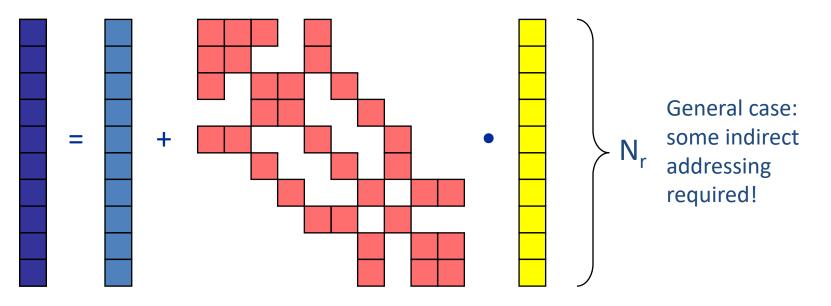

- Case study: tall & skinny matrix-matrix multiplication

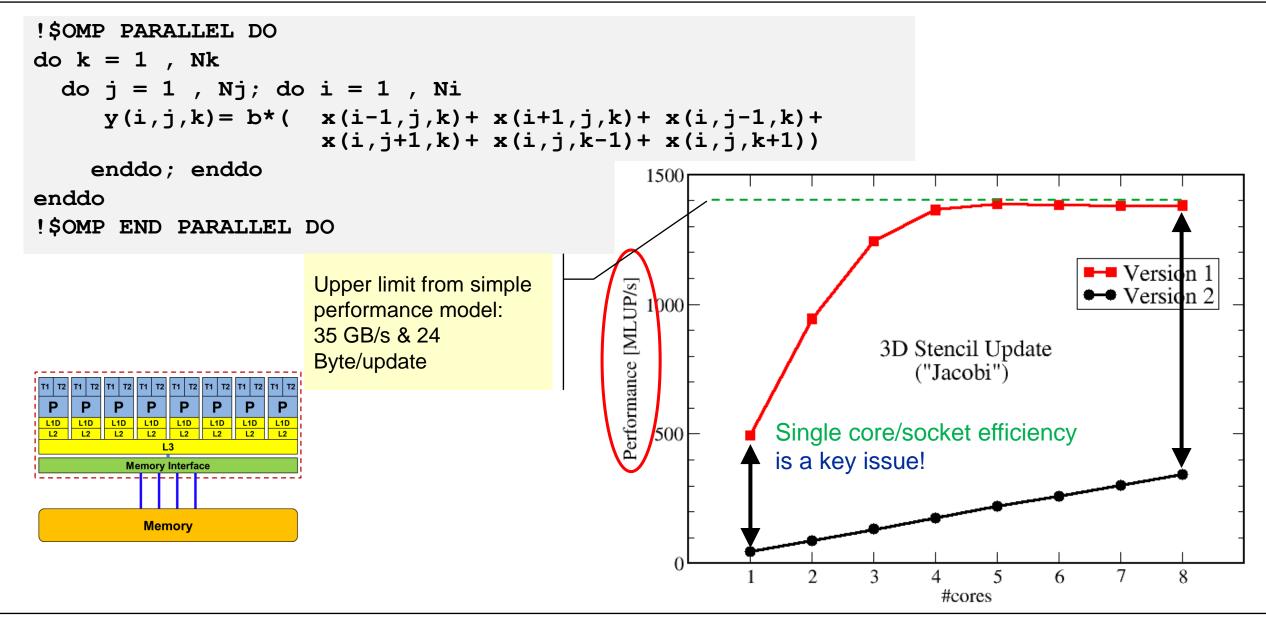

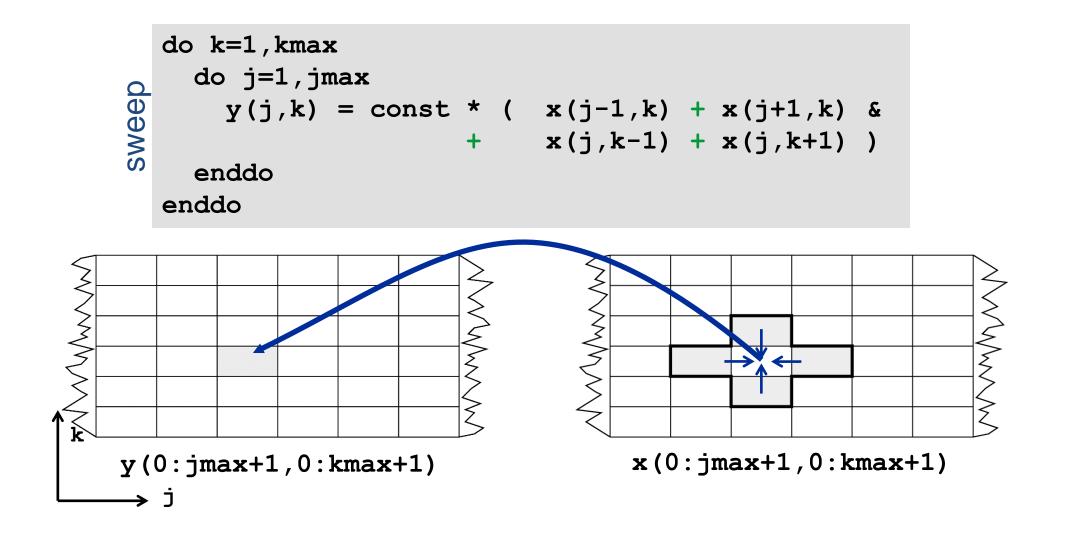

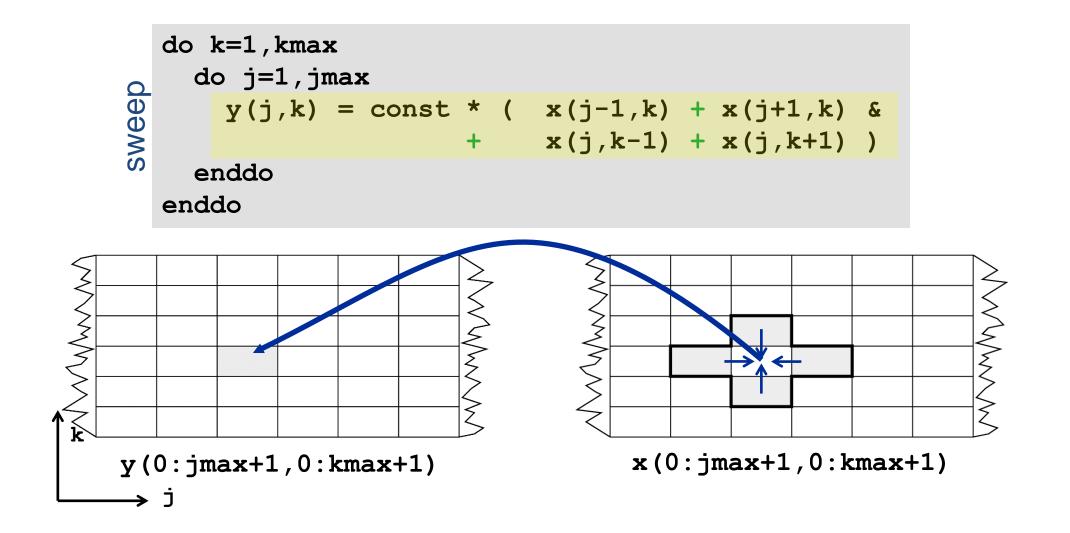

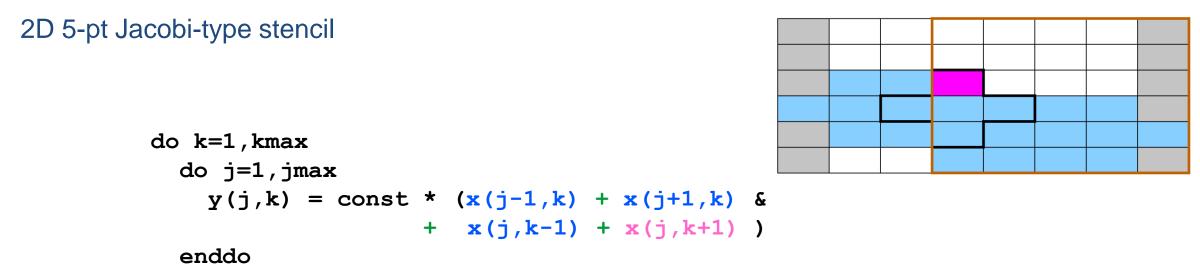

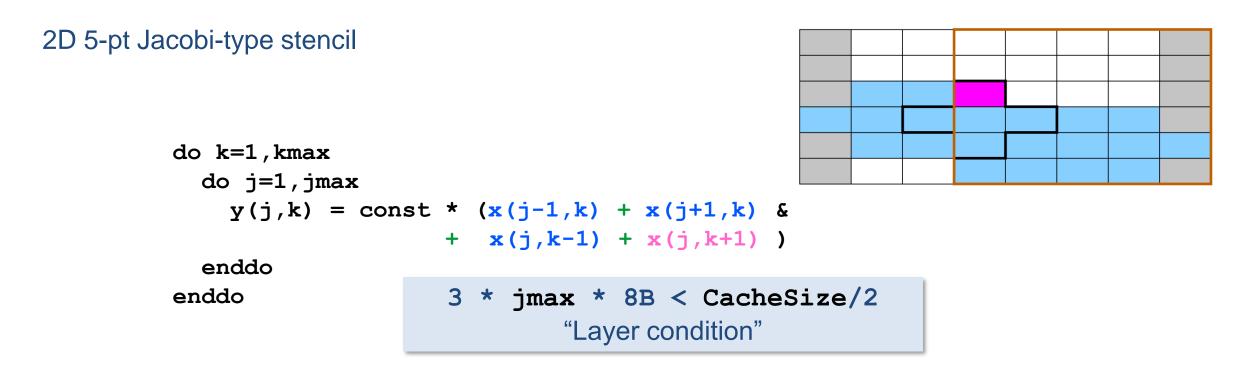

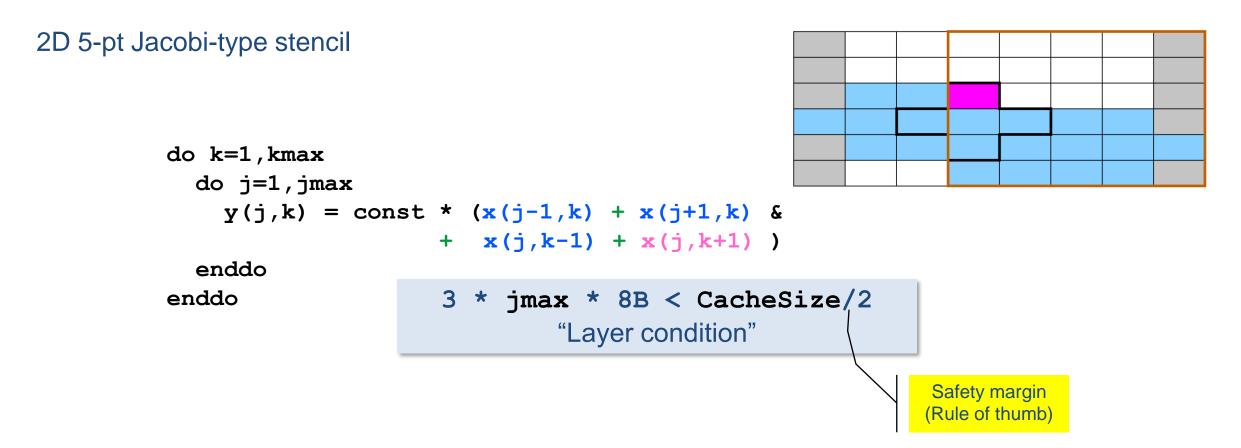

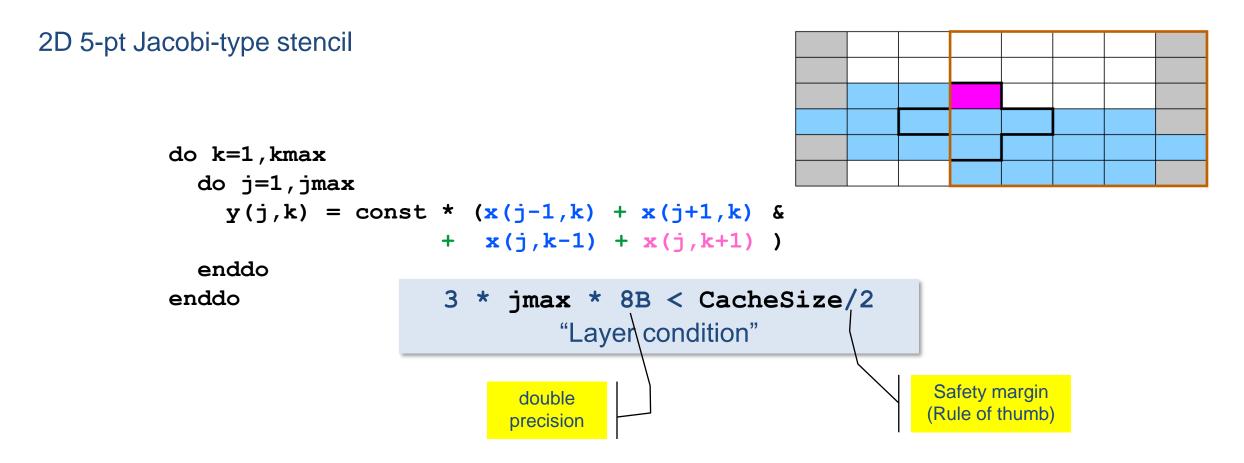

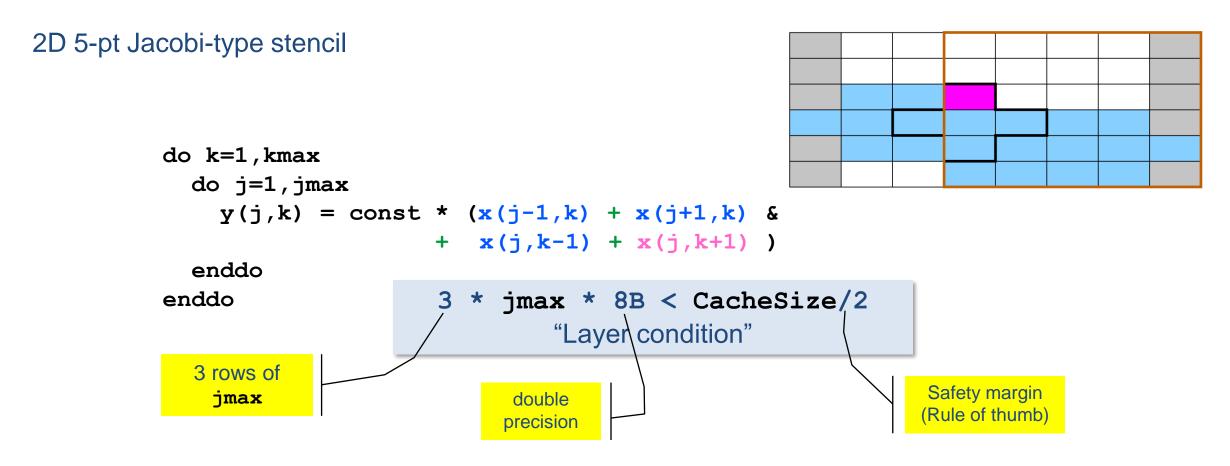

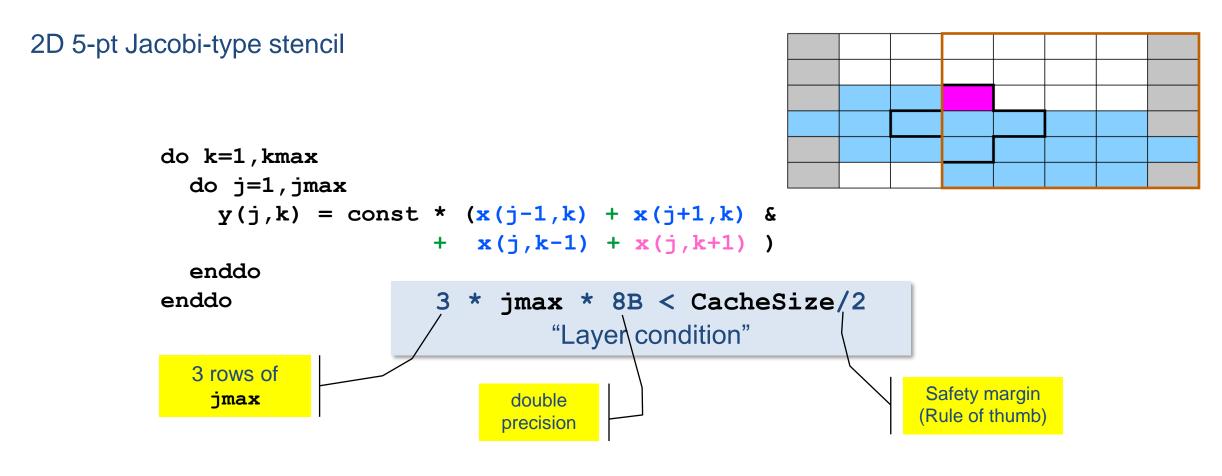

- Case study: Stencil codes

- Demo

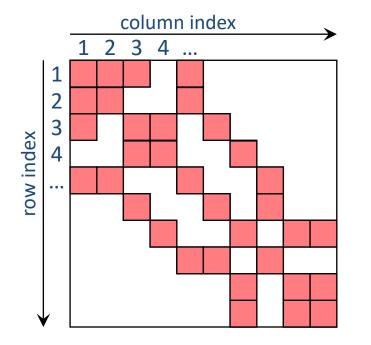

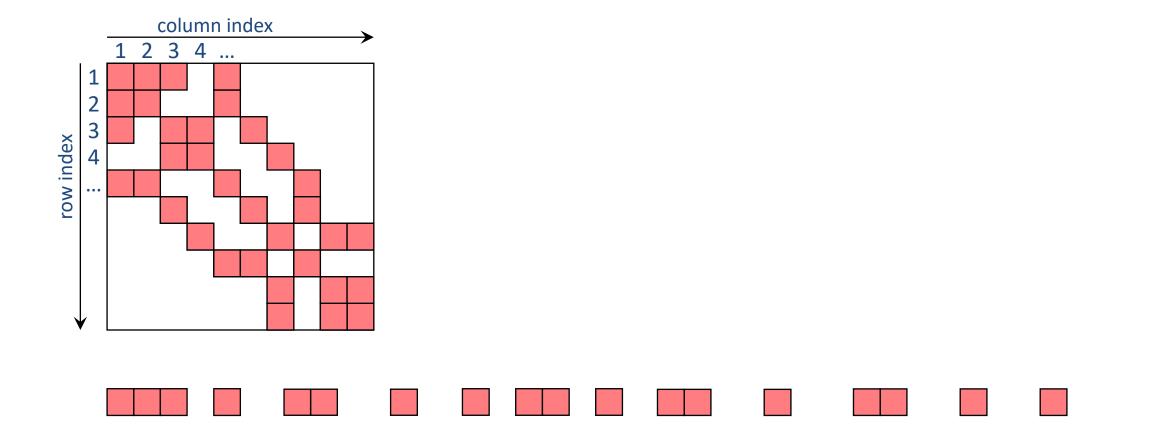

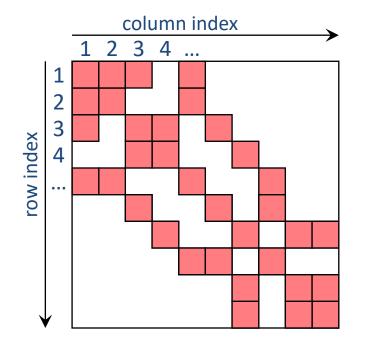

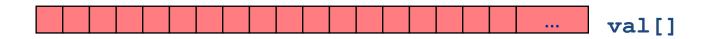

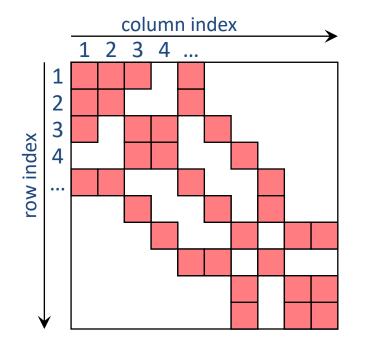

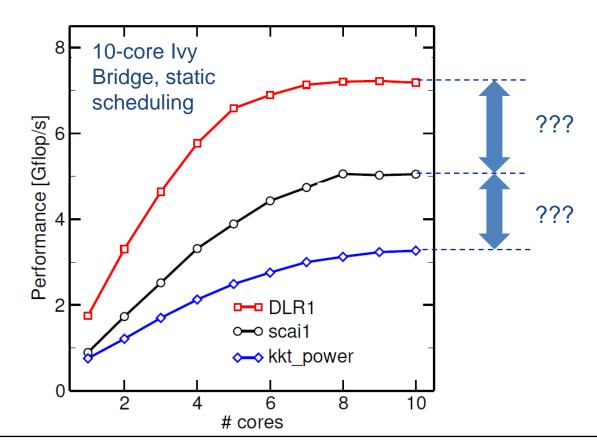

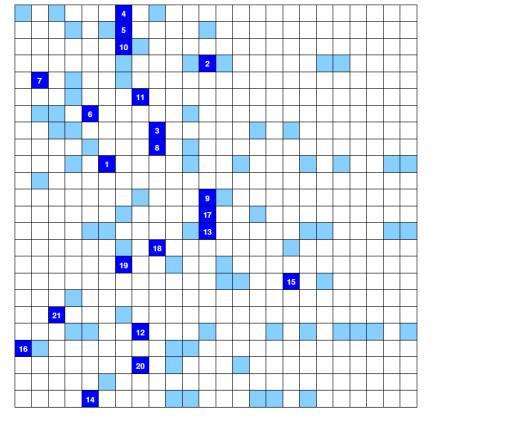

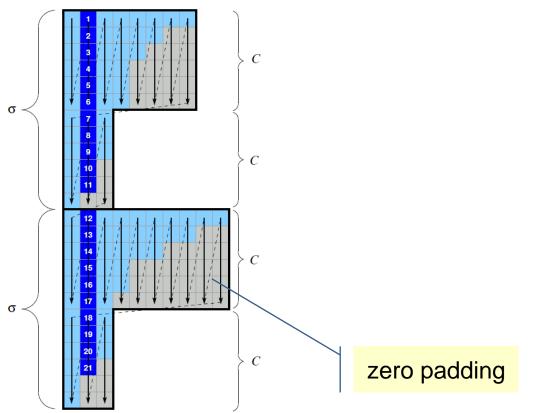

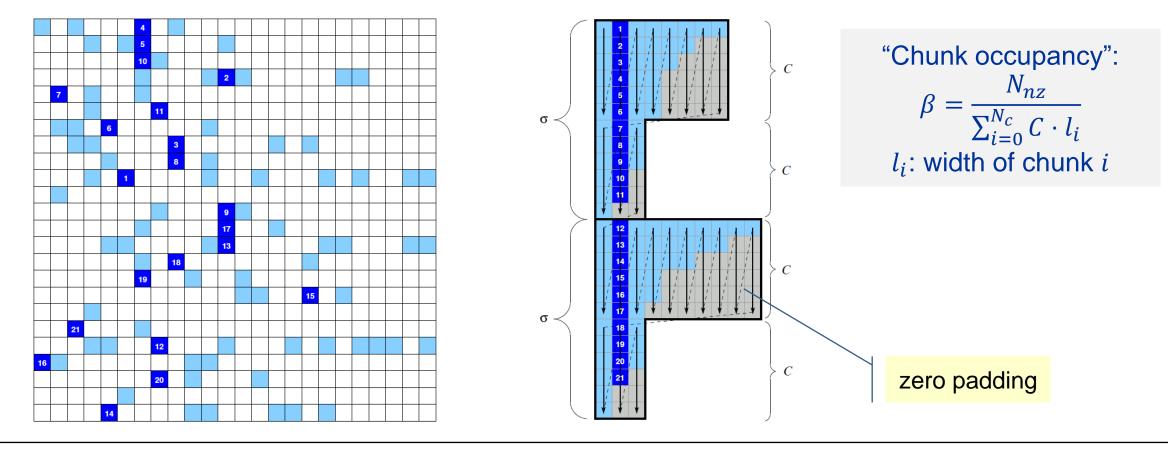

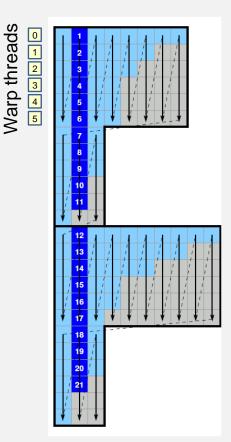

- Case study: sparse matrix-vector multiplication

- Programming for Single Instruction Multiple Data (SIMD) parallelism

- Programming for ccNUMA

Friedrich-Alexander-Universität Erlangen-Nürnberg

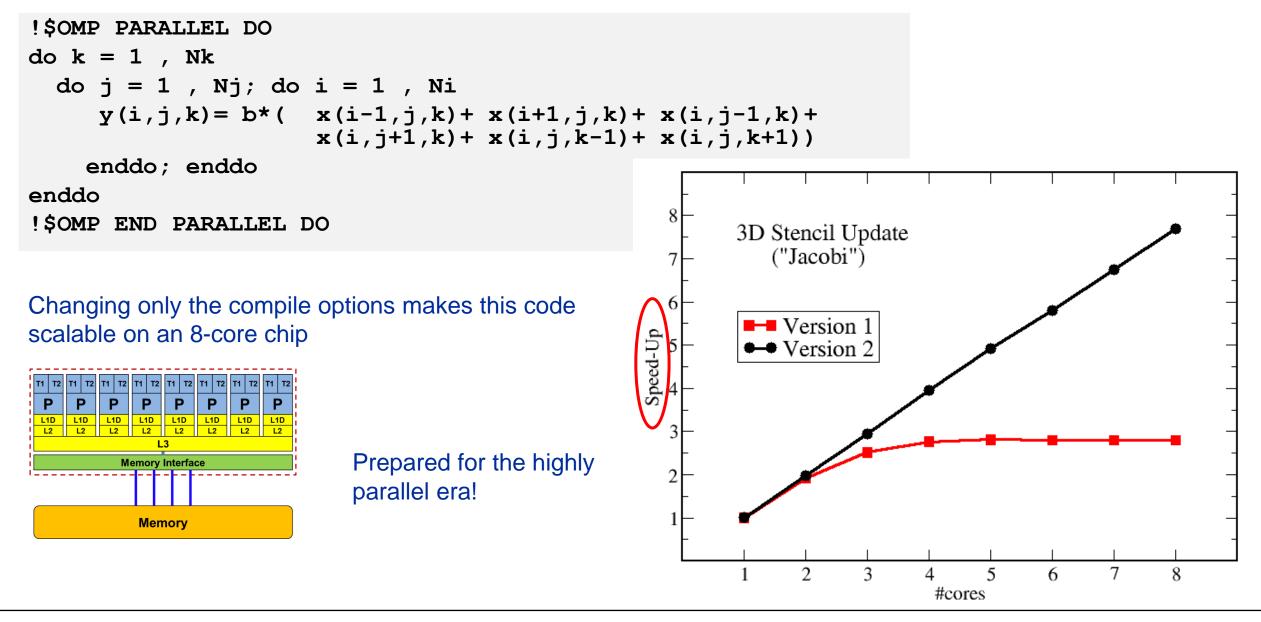

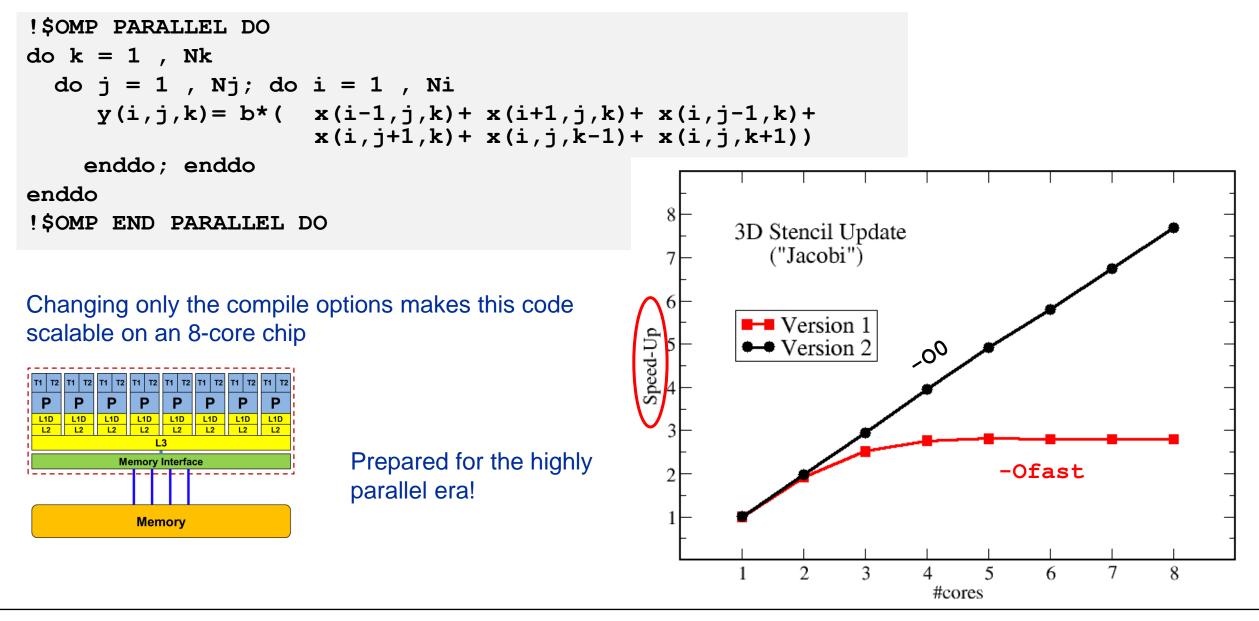

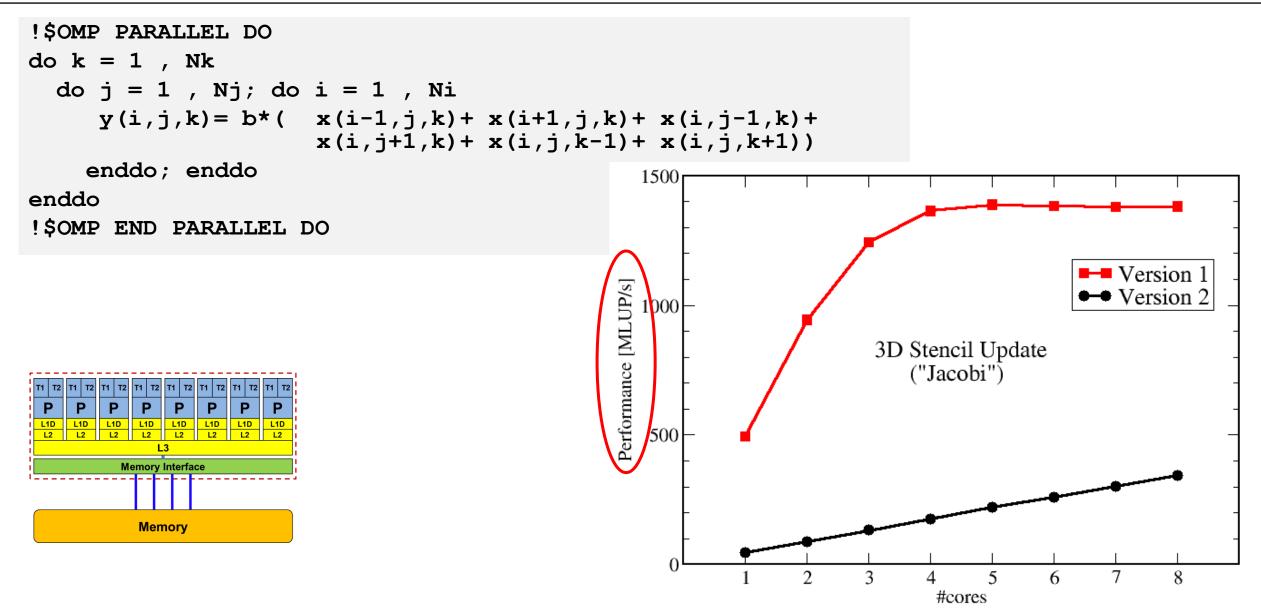

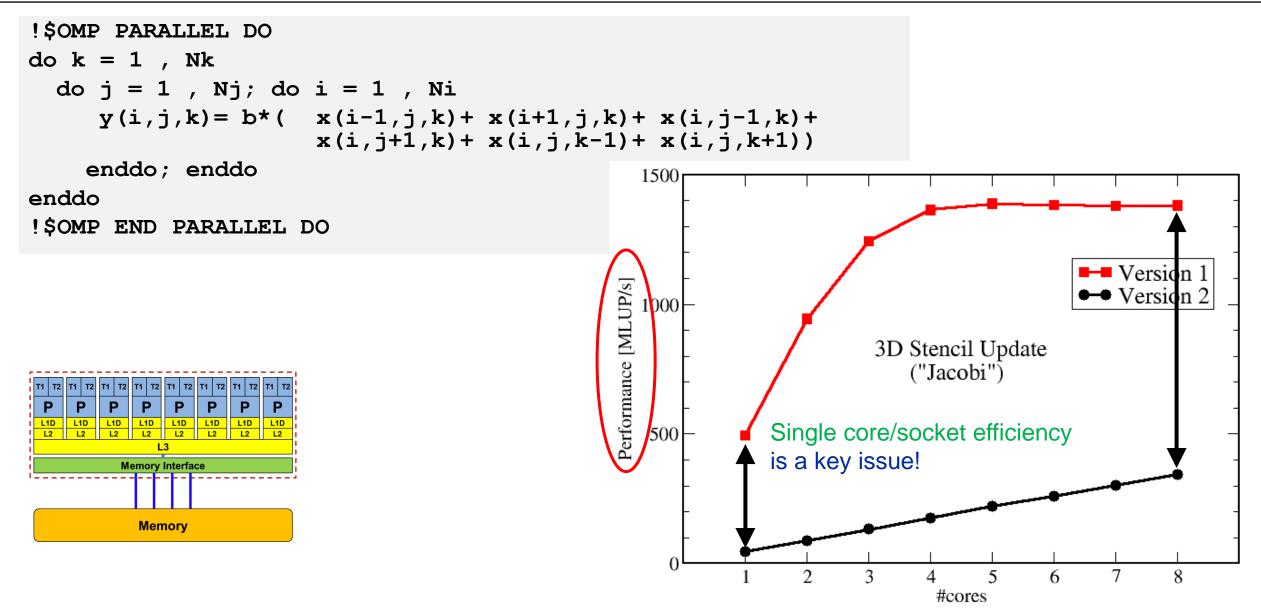

# Prelude: Scalability 4 teh win!

# Questions to ask in high performance computing

- Do I understand the performance behavior of my code?

- Does the performance behave in accordance with a model I have made?

- What is the optimal performance for my code on a given machine?

High Performance Computing == Computing at the bottleneck

- Can I change my code so that the "optimal performance" gets higher?

Circumventing/ameliorating the impact of the bottleneck

- My model yields wrong predictions what's wrong?

- This is the good case, because you learn something

- Performance monitoring / microbenchmarking may help clear up the situation

Friedrich-Alexander-Universität Erlangen-Nürnberg

# Modern computer architecture

### An introduction for software developers

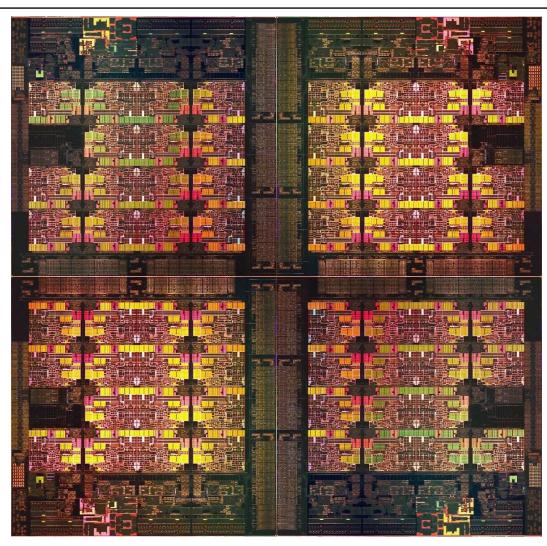

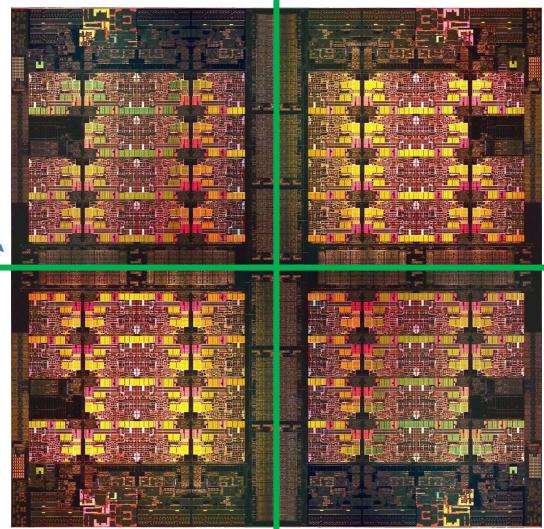

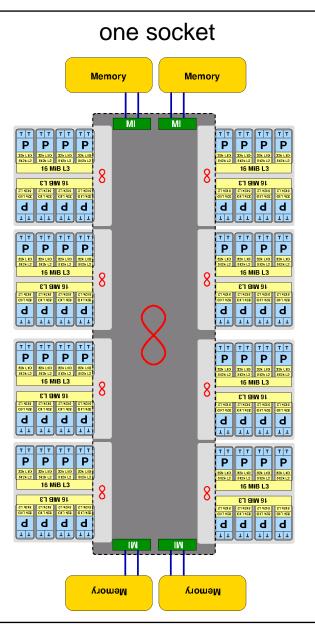

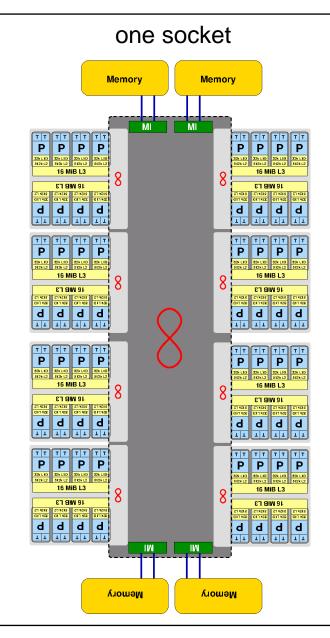

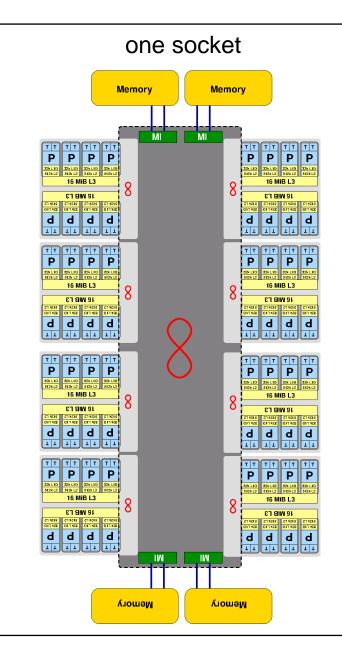

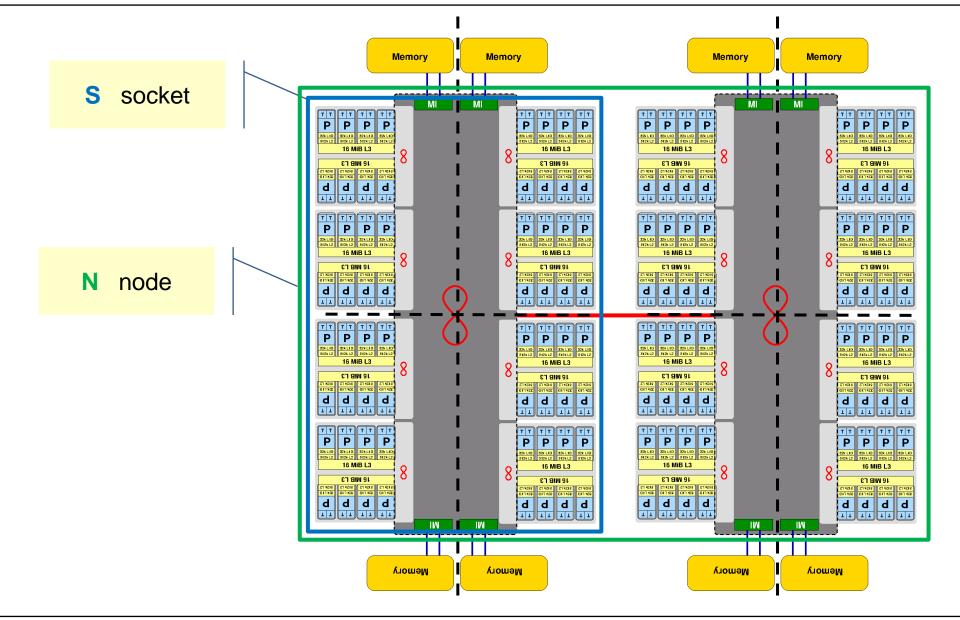

# Multi-core today: Intel Xeon Sapphire Rapids (2023)

- Xeon "Sapphire Rapids" (Platinum/Gold/Silver/Bronze): Up to 60 cores running at 1.7+ GHz (+ "Turbo Mode" 4.8 GHz),

- Simultaneous Multithreading

→ reports as 120-way chip

- "Intel 7" process / up to 350 W

- Multi-die package (4 chips)

- Clock frequency: flexible <sup>(i)</sup>

https://www.techpowerup.com/292204/intel-sapphire-rapids-xeon-4-tile-mcm-annotated

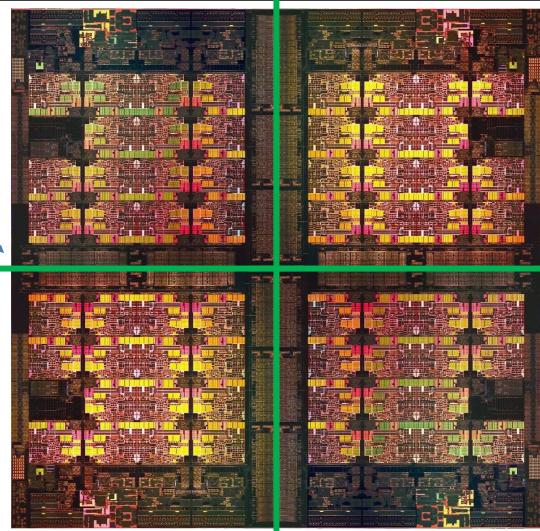

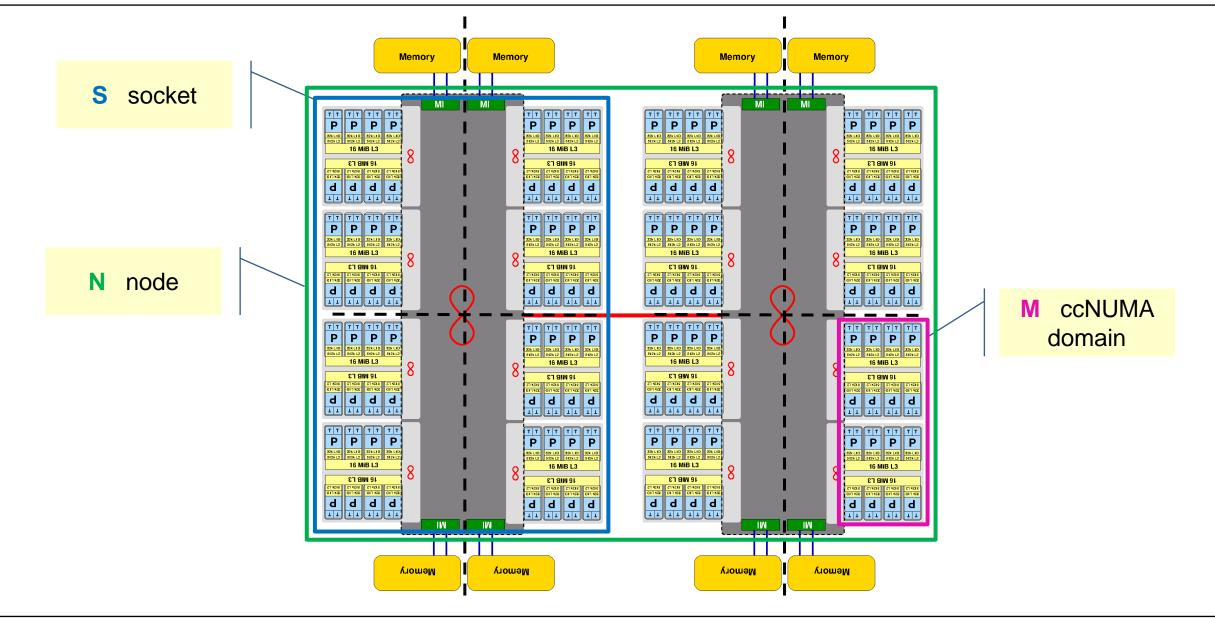

# Multi-core today: Intel Xeon Sapphire Rapids (2023)

- Xeon "Sapphire Rapids" (Platinum/Gold/Silver/Bronze): Up to 60 cores running at 1.7+ GHz (+ "Turbo Mode" 4.8 GHz),

- Simultaneous Multithreading

→ reports as 120-way chip

- "Intel 7" process / up to 350 W

- Multi-die package (4 chips)

- Clock frequency: flexible <sup>(i)</sup>

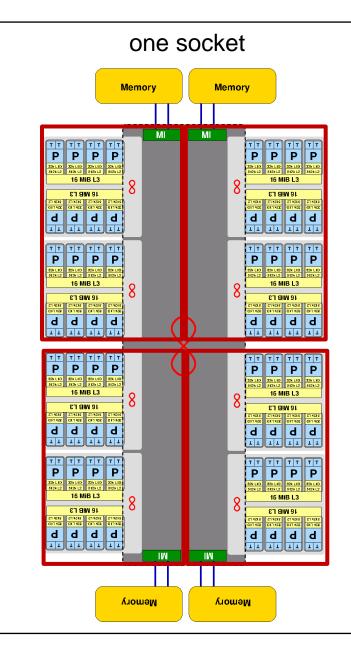

Optional: "Sub-NUMA Clustering" (SNC) mode boot option

→ One memory domain per die

https://www.techpowerup.com/292204/intel-sapphire-rapids-xeon-4-tile-mcm-annotated

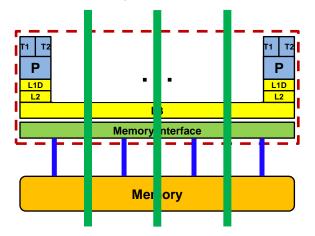

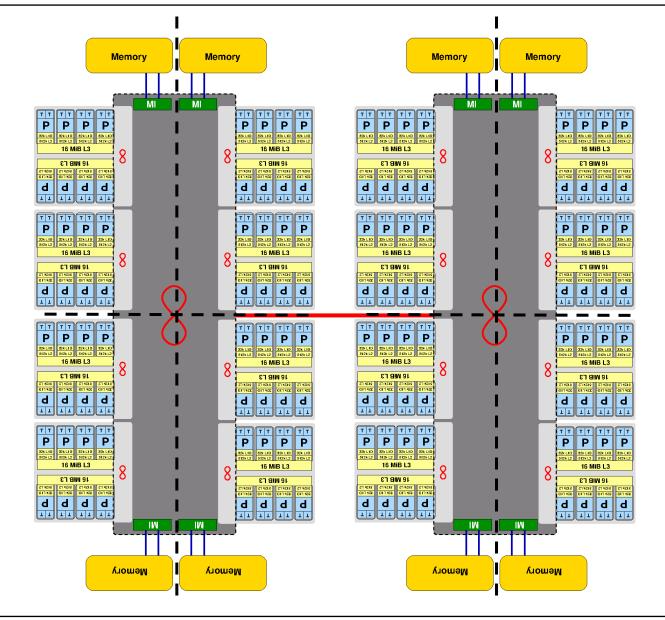

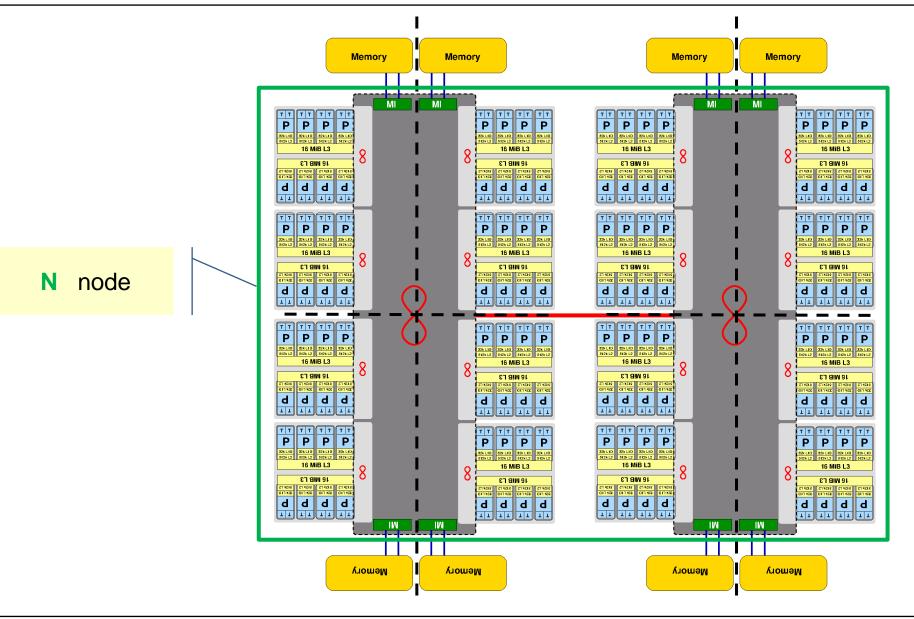

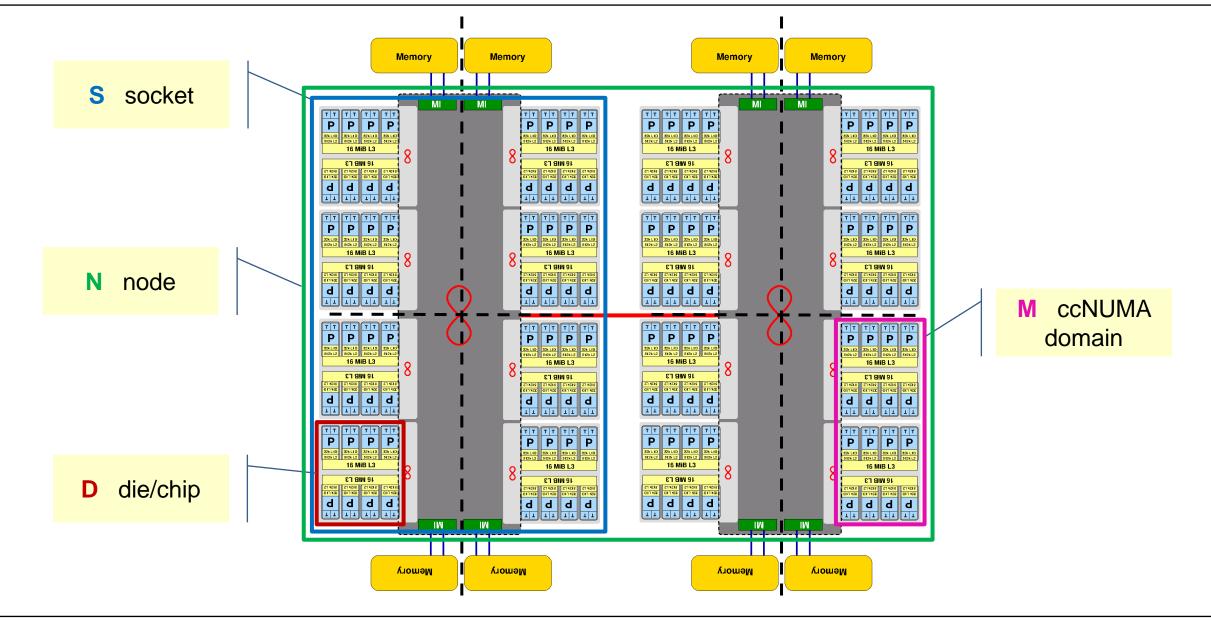

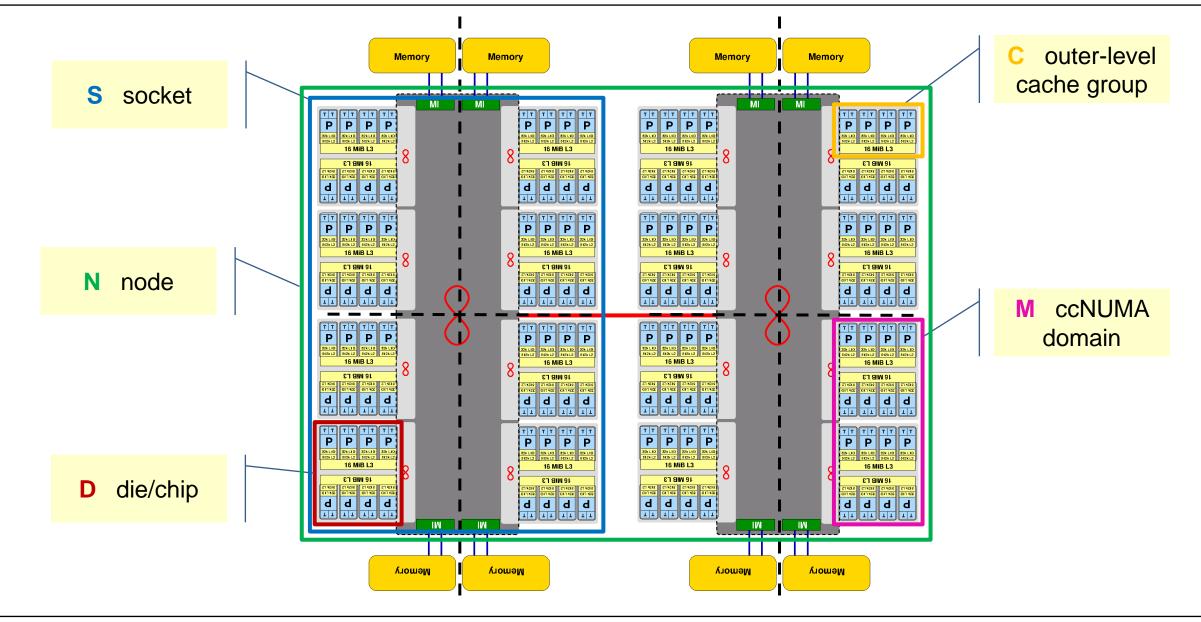

# Multi-core today: Intel Xeon Sapphire Rapids (2023)

- Xeon "Sapphire Rapids" (Platinum/Gold/Silver/Bronze): Up to 60 cores running at 1.7+ GHz (+ "Turbo Mode" 4.8 GHz),

- Simultaneous Multithreading

→ reports as 120-way chip

- "Intel 7" process / up to 350 W

- Multi-die package (4 chips)

- Clock frequency: flexible <sup>(i)</sup>

Optional: "Sub-NUMA Clustering" (SNC) mode boot option

→ One memory domain per die

https://www.techpowerup.com/292204/intel-sapphire-rapids-xeon-4-tile-mcm-annotated

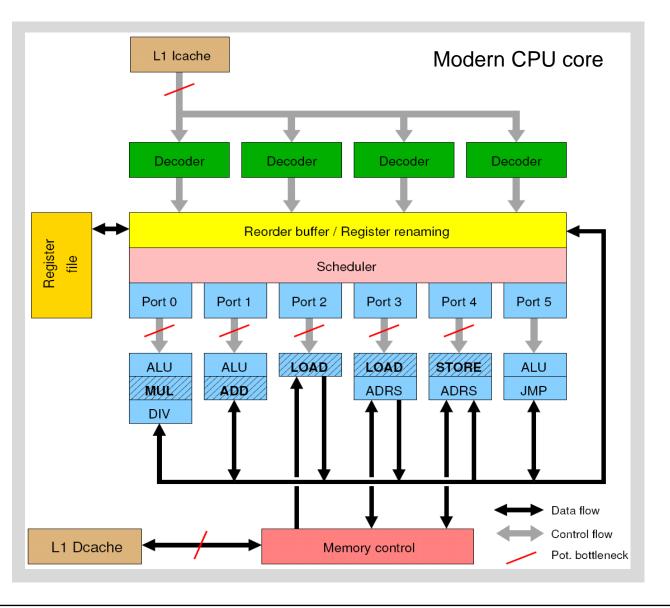

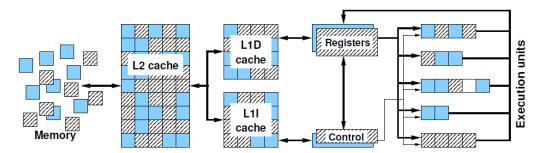

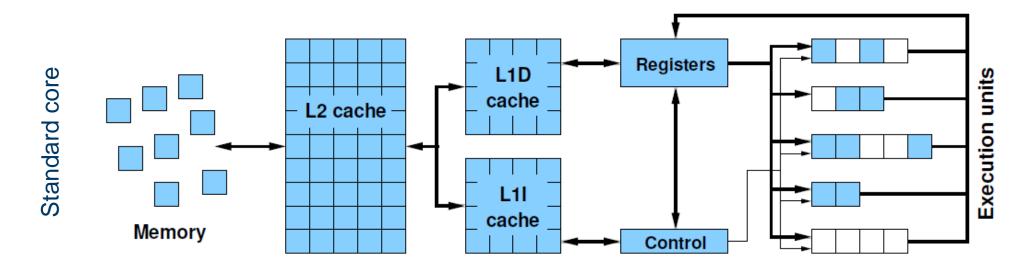

### General-purpose cache-based microprocessor core

- Implements "Stored Program Computer" concept (Turing 1936)

- Similar designs on all modern systems

- (Still) multiple potential bottlenecks

The clock cycle is the "heartbeat" of the core

Friedrich-Alexander-Universität Erlangen-Nürnberg

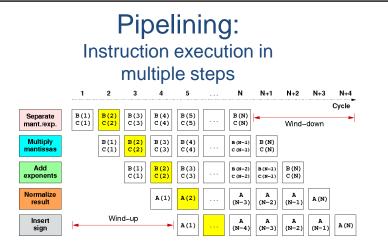

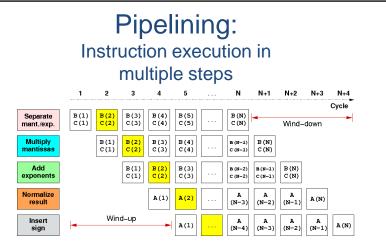

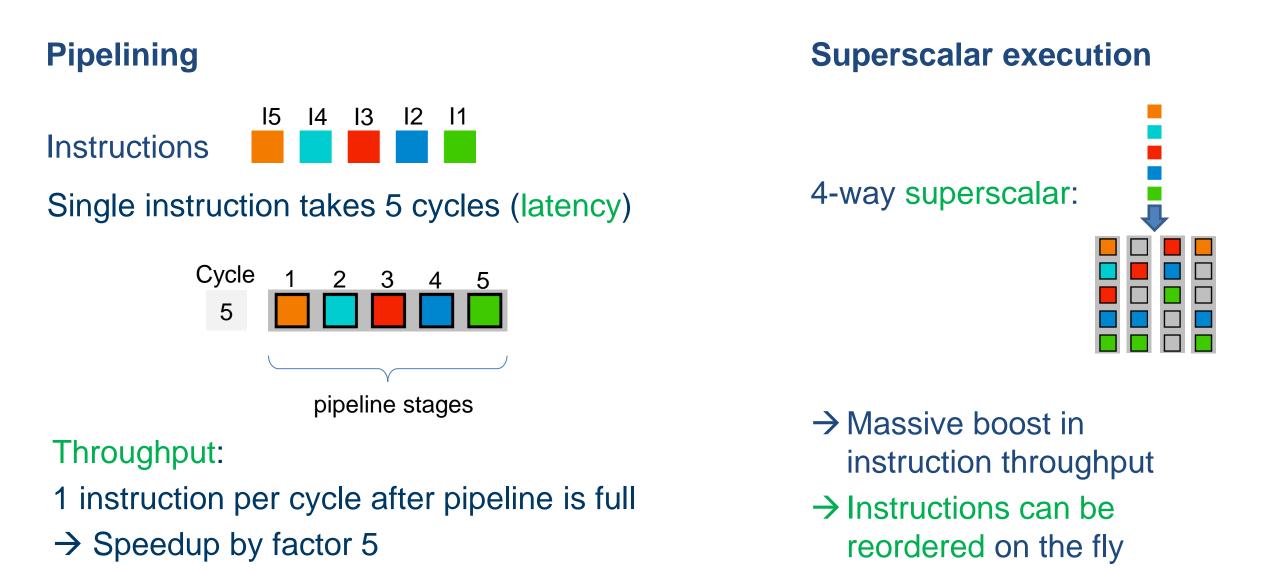

# **In-core features**

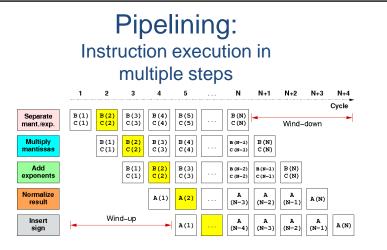

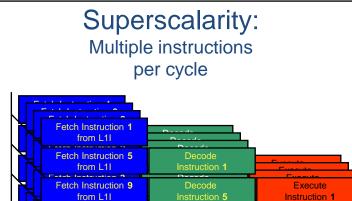

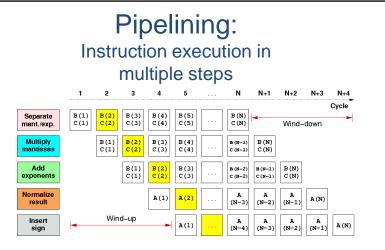

### Pipelining, Superscalarity, SIMD, SMT

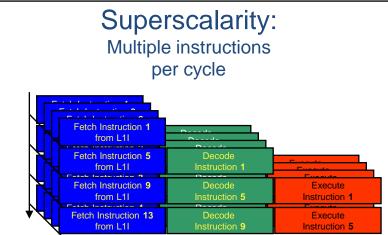

#### Superscalarity: Multiple instructions per cycle

|  | Fetch Instruction 1<br>from L1I  | Decede<br>Decede        |                          |

|--|----------------------------------|-------------------------|--------------------------|

|  | Fetch Instruction 5<br>from L1I  | Decode<br>Instruction 1 | - Free and -             |

|  | Fetch Instruction 9<br>from L1I  | Decode<br>Instruction 5 | Execute<br>Instruction 1 |

|  | Fetch Instruction 13<br>from L1I | Decode<br>Instruction 9 | Execute<br>Instruction 5 |

Instruction 9

Execute

Instruction 5

Fetch Instruction 13

from L11

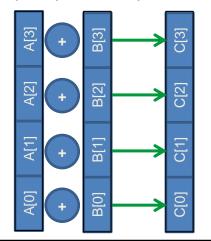

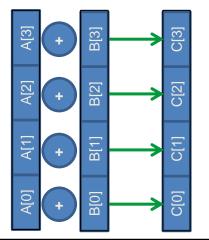

#### Single Instruction Multiple Data:

Multiple operations per instruction

#### Node-Level Performance Engineering

#### Single Instruction Multiple Data:

Multiple operations per instruction

#### Simultaneous Multi-Threading: Multiple instruction sequences in parallel

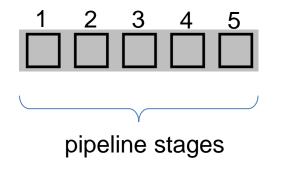

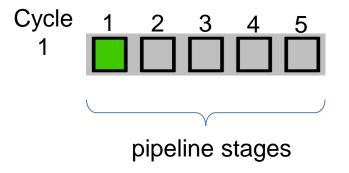

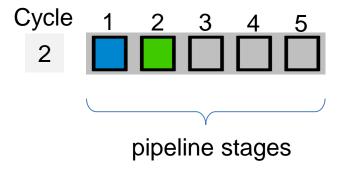

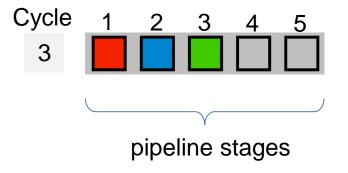

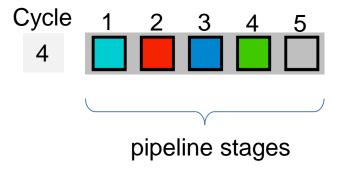

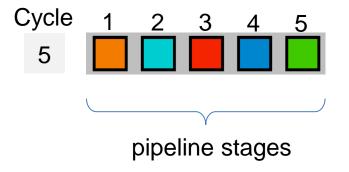

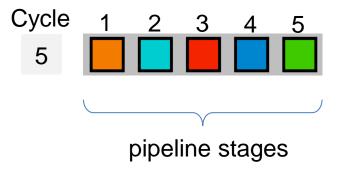

Single instruction takes 5 cycles (latency)

Throughput:

1 instruction per cycle after pipeline is full

→ Speedup by factor 5

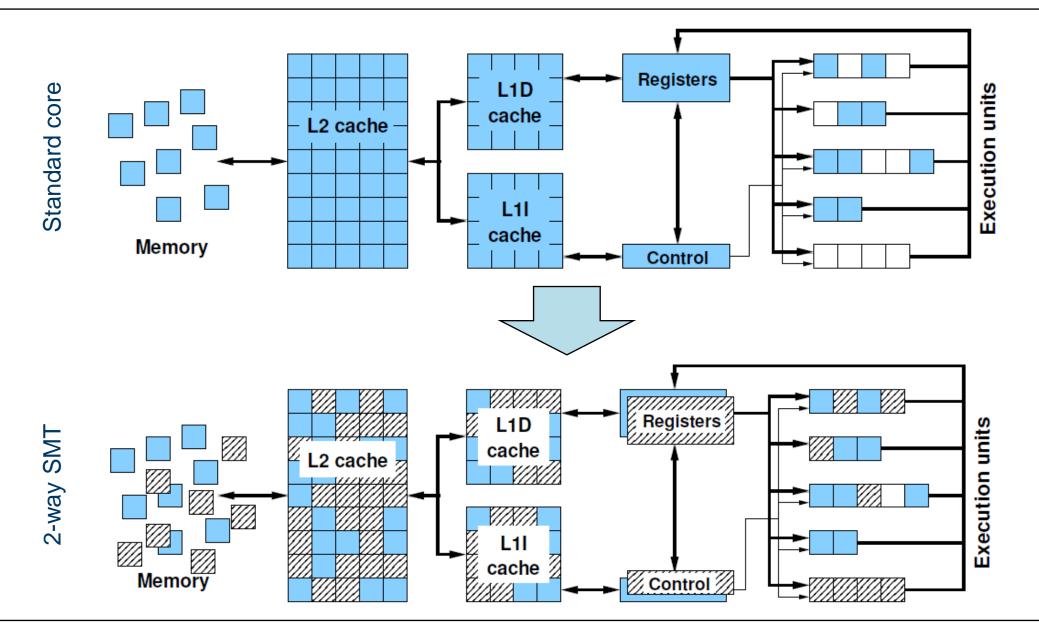

# Simultaneous multi-threading (SMT)

### Simultaneous multi-threading (SMT)

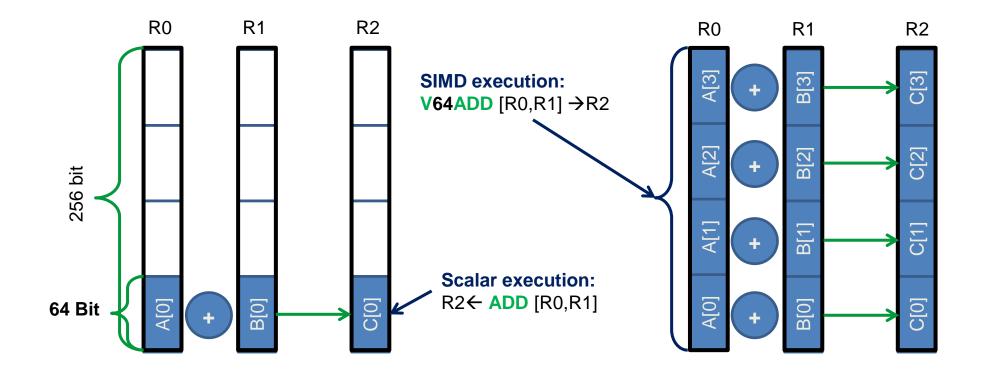

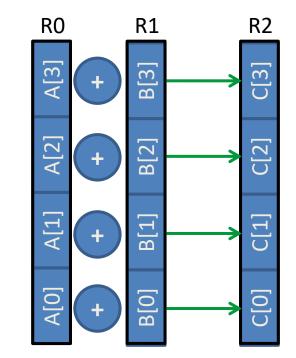

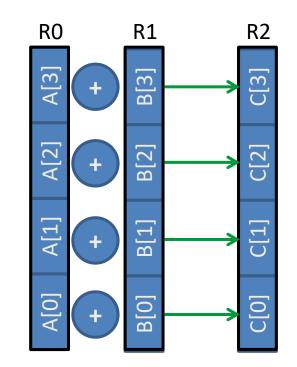

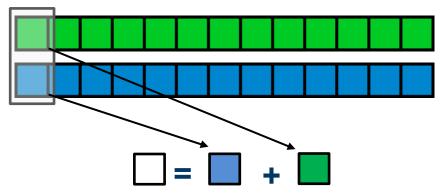

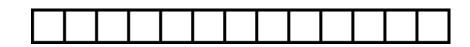

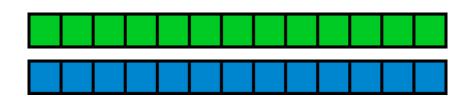

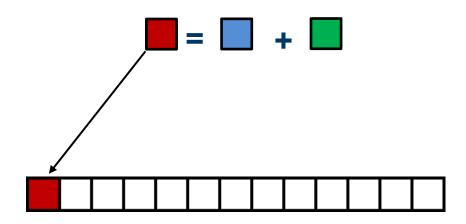

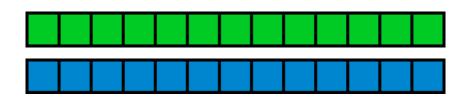

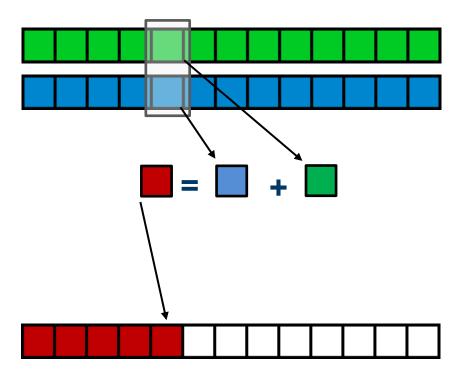

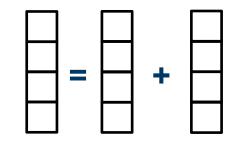

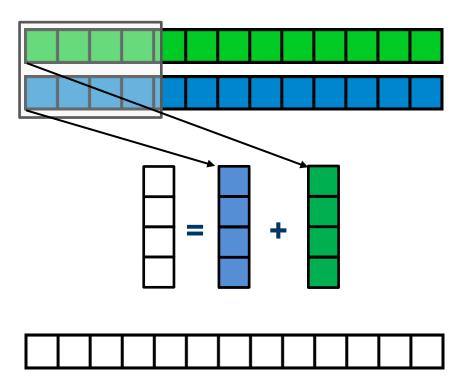

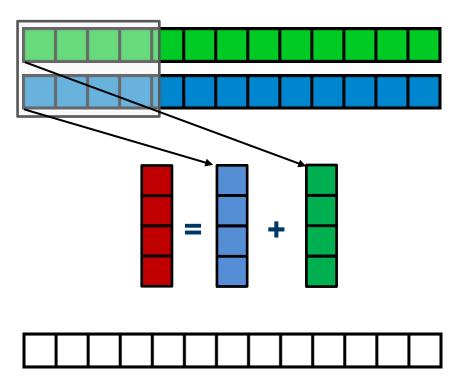

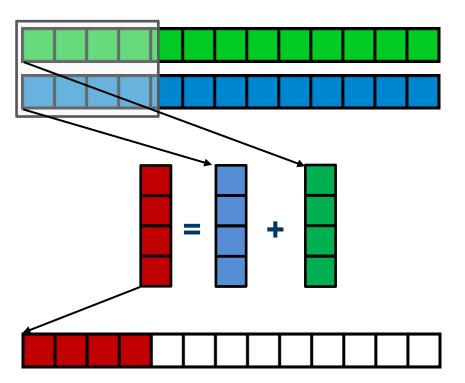

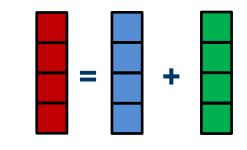

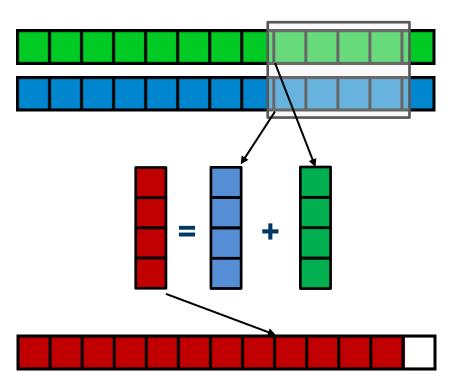

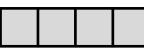

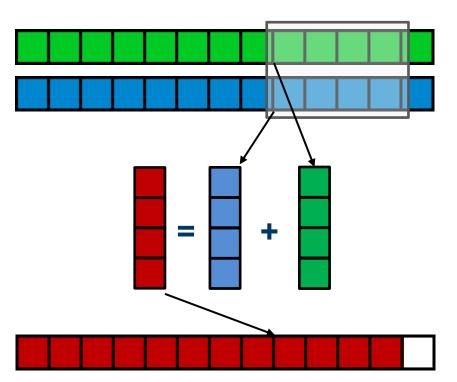

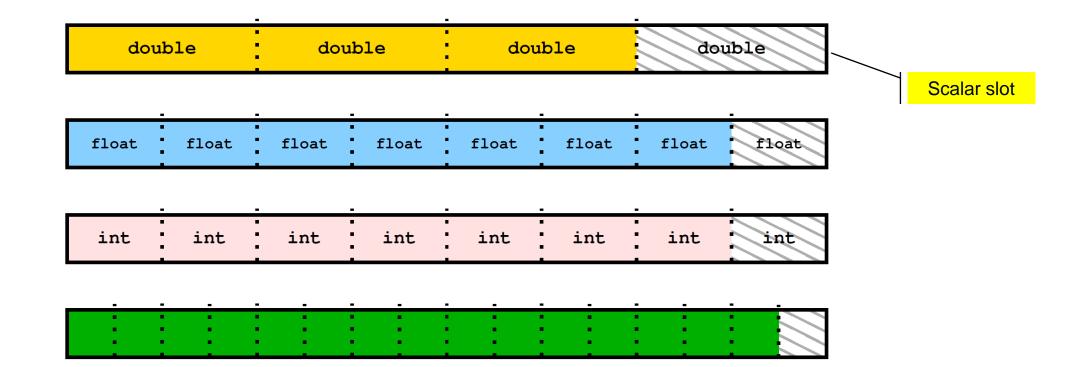

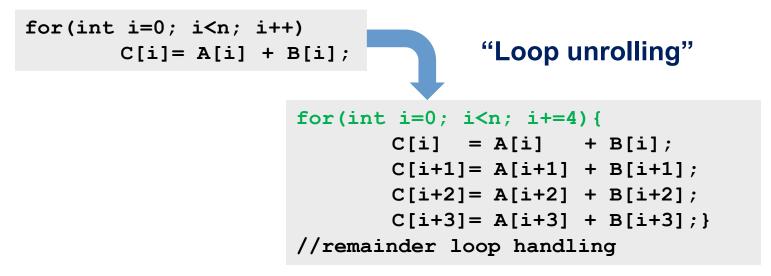

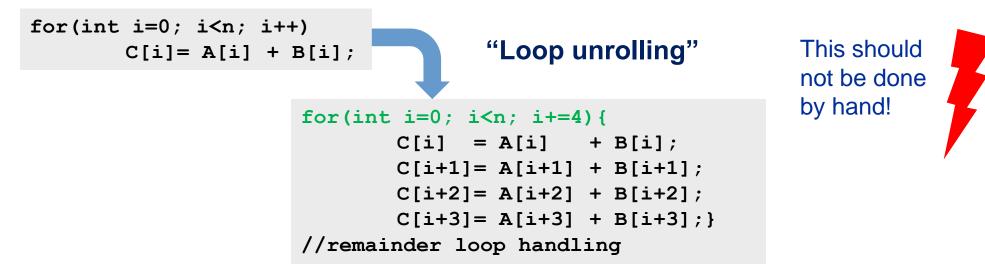

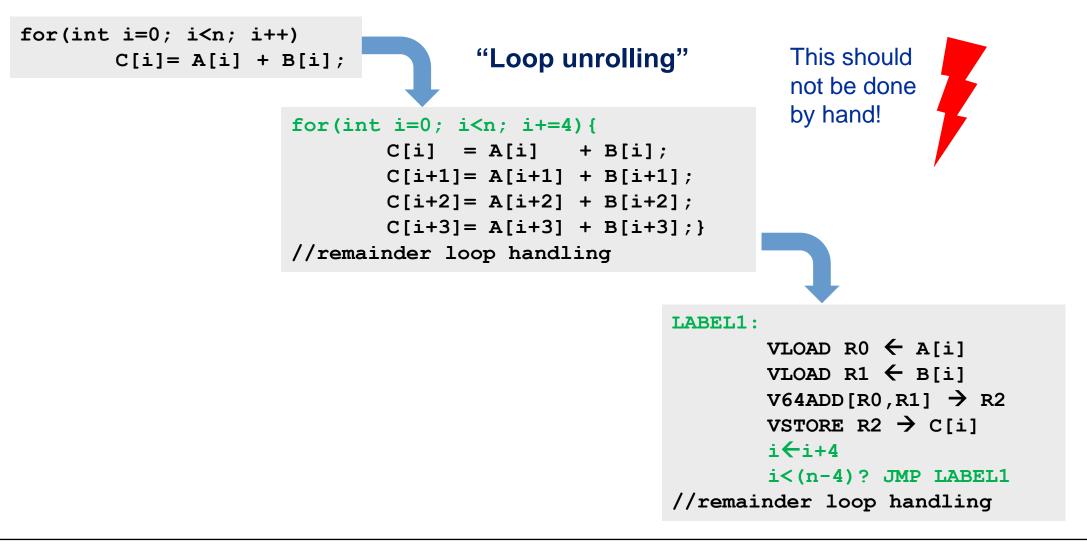

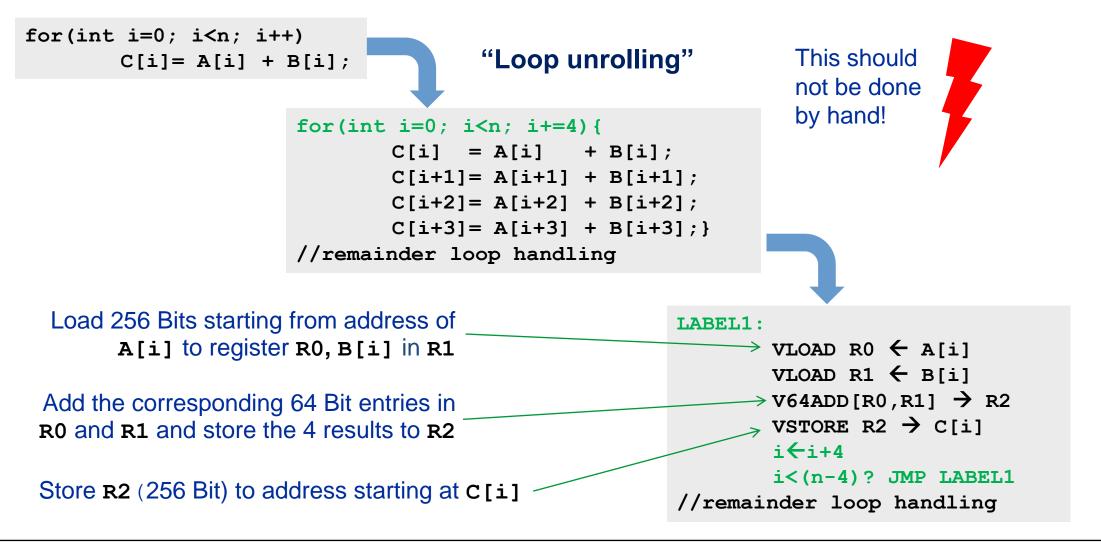

## SIMD processing

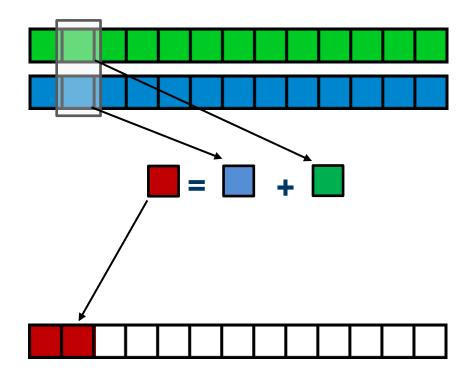

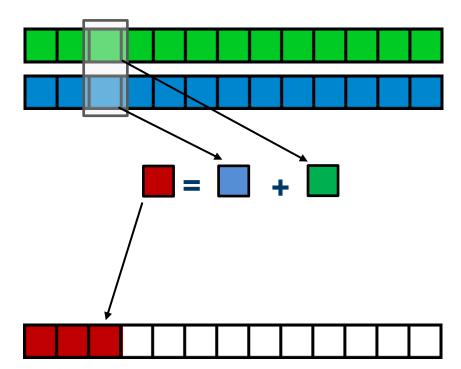

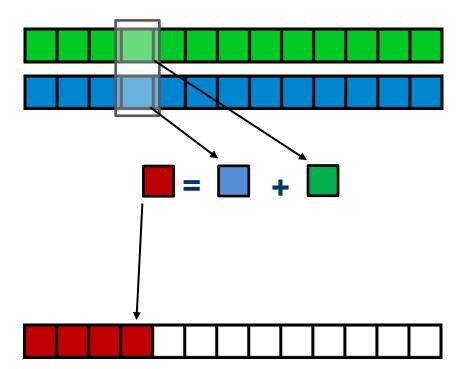

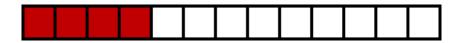

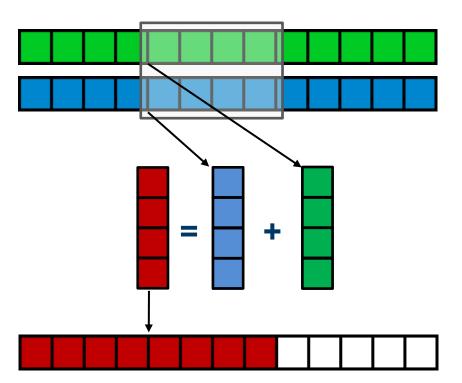

- Single Instruction Multiple Data (SIMD) operations allow the execution of the same operation on "wide" registers from a single instruction

- Adding two registers holding double precision floating point operands:

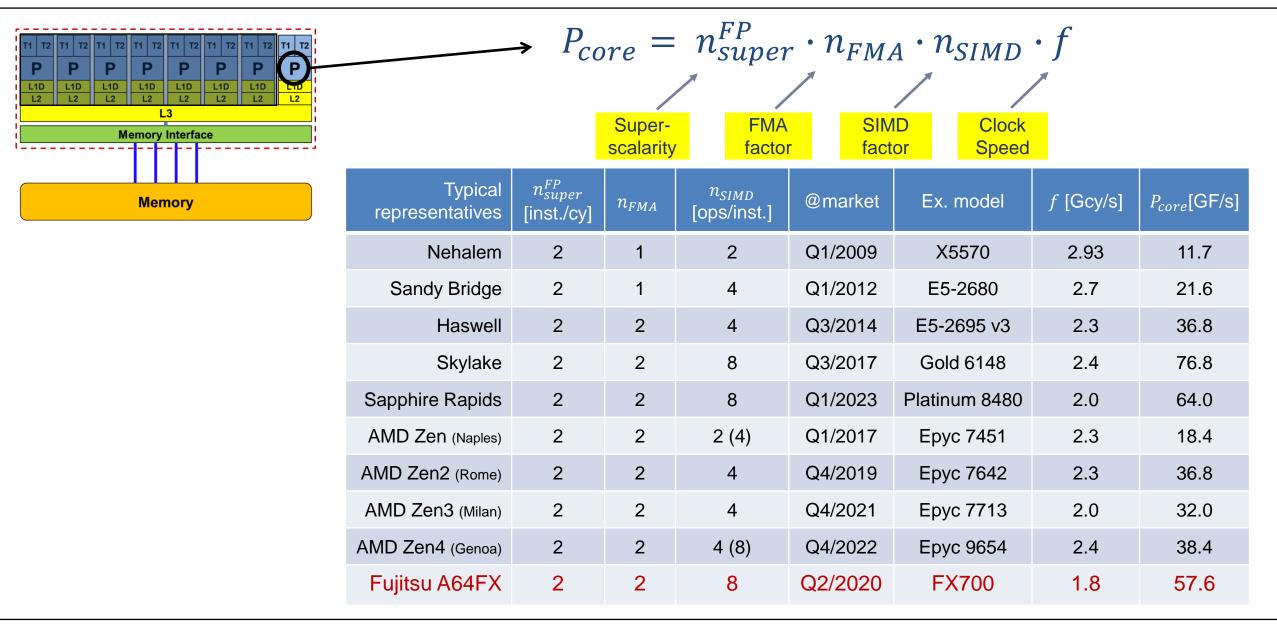

# Single-core DP floating-point performance

Friedrich-Alexander-Universität Erlangen-Nürnberg

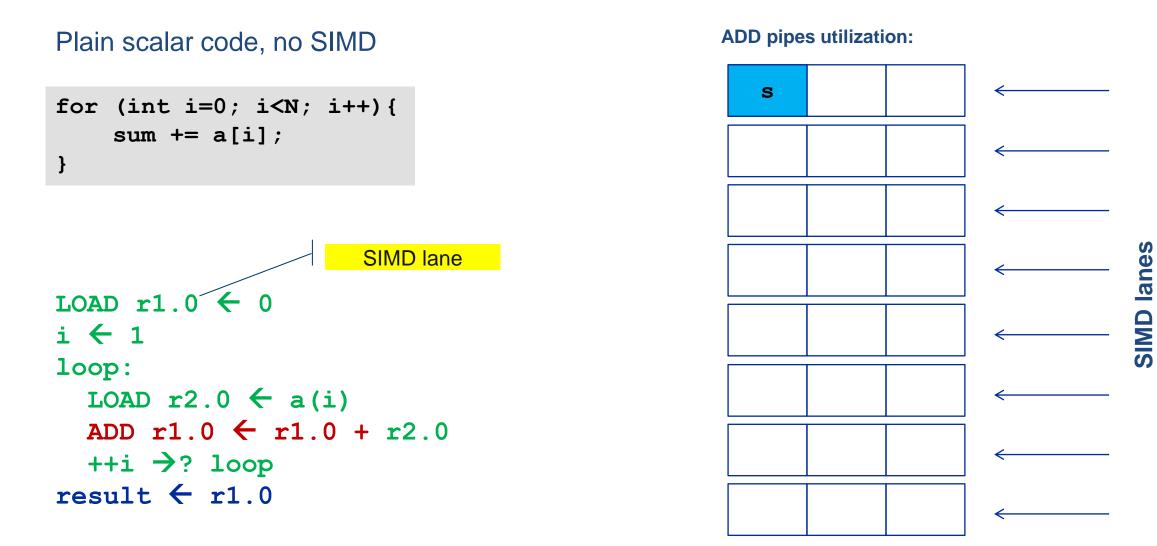

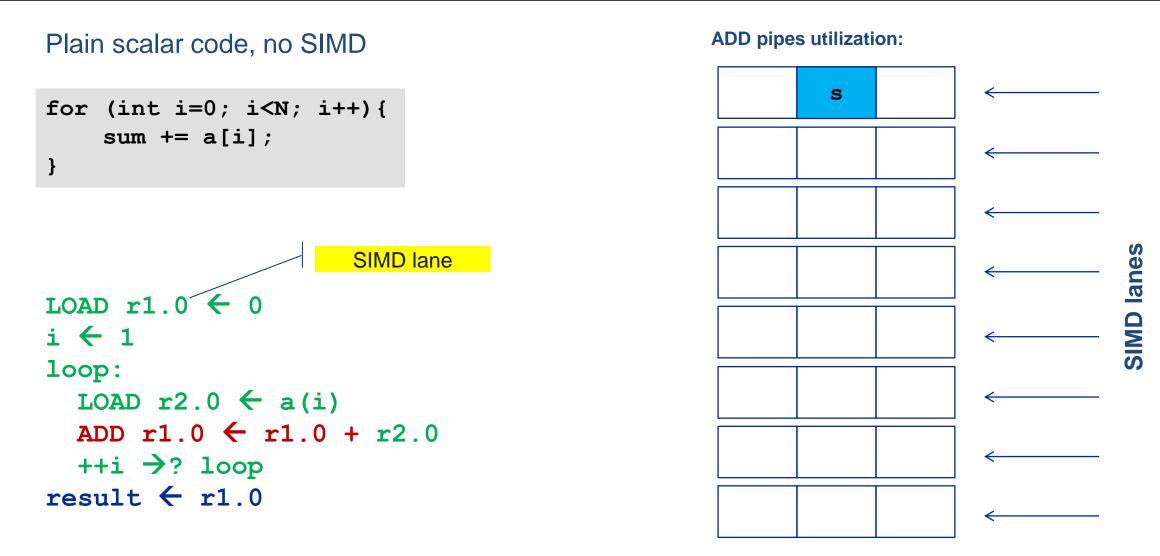

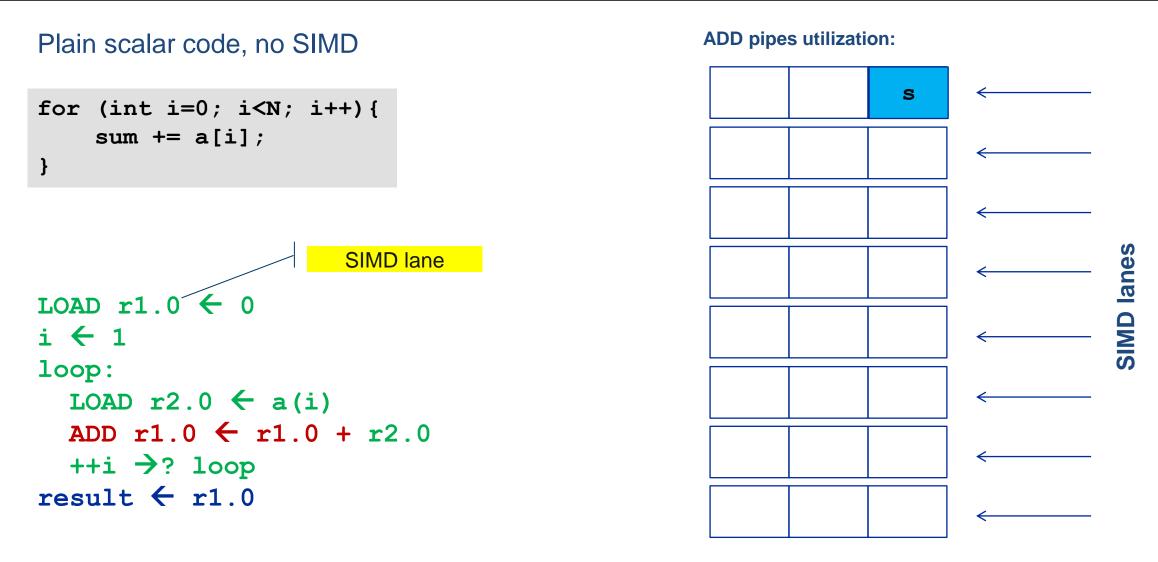

# **Example: The sum reduction**

### A "simple" example: The sum reduction

```

for (int i=0; i<N; i++) {

sum += a[i];

}</pre>

```

...in single precision on an AVXcapable core (ADD latency = 3 cy)

How fast can this loop possibly run with data in the L1 cache?

```

for (int i=0; i<N; i++) {

sum += a[i];

}</pre>

```

...in single precision on an AVXcapable core (ADD latency = 3 cy)

How fast can this loop possibly run with data in the L1 cache?

- Loop-carried dependency on summation variable

- Execution stalls at every ADD until previous ADD is complete

→No pipelining?→No SIMD?

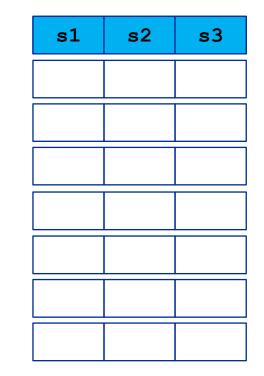

```

for (int i=0; i<N; i+=3) {

s1 += a[i+0];

s2 += a[i+1];

s3 += a[i+2];

}

sum = sum + s1+s2+s3;</pre>

```

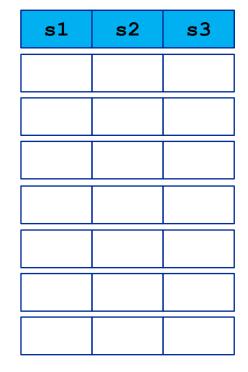

Scalar code, 3-way "modulo variable expansion" LOAD r1.0  $\leftarrow$  0 LOAD  $r2.0 \leftarrow 0$ LOAD r3.0  $\leftarrow$  0 i ← 1 loop: LOAD r4.0  $\leftarrow$  a(i) LOAD r5.0  $\leftarrow$  a(i+1) LOAD r6.0  $\leftarrow$  a(i+2) ADD  $r1.0 \leftarrow r1.0 + r4.0 \# scalar ADD$ ADD r2.0  $\leftarrow$  r2.0 + r5.0 # scalar ADD ADD  $r3.0 \leftarrow r3.0 + r6.0 \# scalar ADD$ i+=3 →? loop result  $\leftarrow$  r1.0+r2.0+r3.0

```

for (int i=0; i<N; i+=3) {

s1 += a[i+0];

s2 += a[i+1];

s3 += a[i+2];

}

sum = sum + s1+s2+s3;</pre>

```

Scalar code, 3-way "modulo variable expansion" LOAD r1.0  $\leftarrow$  0 LOAD  $r2.0 \leftarrow 0$ LOAD r3.0  $\leftarrow$  0 i ← 1 loop: LOAD r4.0  $\leftarrow$  a(i) LOAD r5.0  $\leftarrow$  a(i+1) LOAD r6.0  $\leftarrow$  a(i+2) ADD  $r1.0 \leftarrow r1.0 + r4.0 \# scalar ADD$ ADD r2.0  $\leftarrow$  r2.0 + r5.0 # scalar ADD ADD  $r3.0 \leftarrow r3.0 + r6.0 \# scalar ADD$ i+=3 →? loop result  $\leftarrow$  r1.0+r2.0+r3.0

```

for (int i=0; i<N; i+=3) {

s1 += a[i+0];

s2 += a[i+1];

s3 += a[i+2];

}

sum = sum + s1+s2+s3;</pre>

```

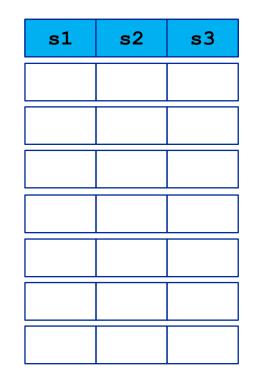

```

SIMD vectorization (8-way MVE) x pipelining (3-way MVE)

```

```

LOAD [r1.0,...,r1.7] \leftarrow [0,...,0]

LOAD [r2.0,...,r2.7] \leftarrow [0,...,0]

LOAD [r3.0,...,r3.7] \leftarrow [0,...,0]

i \leftarrow 1

```

```

for (int i=0; i<N; i+=24) {

s10 += a[i+0]; s20 += a[i+8]; s30 += a[i+16];

s11 += a[i+1]; s21 += a[i+9]; s31 += a[i+17];

s12 += a[i+2]; s22 += a[i+10]; s32 += a[i+18];

s13 += a[i+3]; s23 += a[i+11]; s33 += a[i+19];

s14 += a[i+4]; s24 += a[i+12]; s34 += a[i+20];

s15 += a[i+5]; s25 += a[i+13]; s35 += a[i+21];

s16 += a[i+6]; s26 += a[i+14]; s36 += a[i+22];

s17 += a[i+7]; s27 += a[i+15]; s37 += a[i+23];

}</pre>

```

```

sum = sum + s10+s11+...+s37;

```

| → ADD peak | s10 | s20 | s30 |

|------------|-----|-----|-----|

|            | s11 | s21 | s31 |

|            | s12 | s22 | s32 |

|            | s13 | s23 | s33 |

|            | s14 | s24 | s34 |

|            | s15 | s25 | s35 |

|            | s16 | s26 | s36 |

|            | s17 | s27 | s37 |

| LOAD $[r4.0,,r4.7] \leftarrow [a(i),,a(i+7)]$<br>LOAD $[r5.0,,r5.7] \leftarrow [a(i+8),,a(i+15)]$<br>LOAD $[r6.0,,r6.7] \leftarrow [a(i+16),,a(i+23)]$ | # | SIMD | LOAD |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|------|

| ADD $r1 \leftarrow r1 + r4$ # SIMD ADD<br>ADD $r2 \leftarrow r2 + r5$ # SIMD ADD<br>ADD $r3 \leftarrow r3 + r6$ # SIMD ADD                             |   |      |      |

| i+=24 →? loop<br>result ← r1.0+r1.1++r3.6+r3.7                                                                                                         |   |      |      |

loop:

#### Questions

When can this performance actually be achieved?

- When can this performance actually be achieved?

- No data transfer bottlenecks

- No other in-core bottlenecks

- Need to execute (3 LOADs + 3 ADDs + 1 increment + 1 compare + 1 branch) in 3 cycles

- When can this performance actually be achieved?

- No data transfer bottlenecks

- No other in-core bottlenecks

- Need to execute (3 LOADs + 3 ADDs + 1 increment + 1 compare + 1 branch) in 3 cycles

- What does the compiler do?

- When can this performance actually be achieved?

- No data transfer bottlenecks

- No other in-core bottlenecks

- Need to execute (3 LOADs + 3 ADDs + 1 increment + 1 compare + 1 branch) in 3 cycles

- What does the compiler do?

- If allowed and capable, the compiler will do this automatically

- When can this performance actually be achieved?

- No data transfer bottlenecks

- No other in-core bottlenecks

- Need to execute (3 LOADs + 3 ADDs + 1 increment + 1 compare + 1 branch) in 3 cycles

- What does the compiler do?

- If allowed and capable, the compiler will do this automatically

- Is the compiler allowed to do this at all?

- When can this performance actually be achieved?

- No data transfer bottlenecks

- No other in-core bottlenecks

- Need to execute (3 LOADs + 3 ADDs + 1 increment + 1 compare + 1 branch) in 3 cycles

- What does the compiler do?

- If allowed and capable, the compiler will do this automatically

- Is the compiler allowed to do this at all?

- Not according to language standards

- High optimization levels can violate language standards

- When can this performance actually be achieved?

- No data transfer bottlenecks

- No other in-core bottlenecks

- Need to execute (3 LOADs + 3 ADDs + 1 increment + 1 compare + 1 branch) in 3 cycles

- What does the compiler do?

- If allowed and capable, the compiler will do this automatically

- Is the compiler allowed to do this at all?

- Not according to language standards

- High optimization levels can violate language standards

- What about the "accuracy" of the result?

- When can this performance actually be achieved?

- No data transfer bottlenecks

- No other in-core bottlenecks

- Need to execute (3 LOADs + 3 ADDs + 1 increment + 1 compare + 1 branch) in 3 cycles

- What does the compiler do?

- If allowed and capable, the compiler will do this automatically

- Is the compiler allowed to do this at all?

- Not according to language standards

- High optimization levels can violate language standards

- What about the "accuracy" of the result?

- Good question ;-)

Friedrich-Alexander-Universität Erlangen-Nürnberg

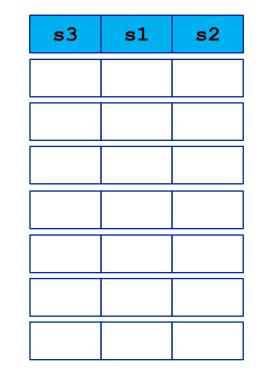

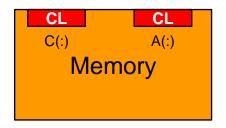

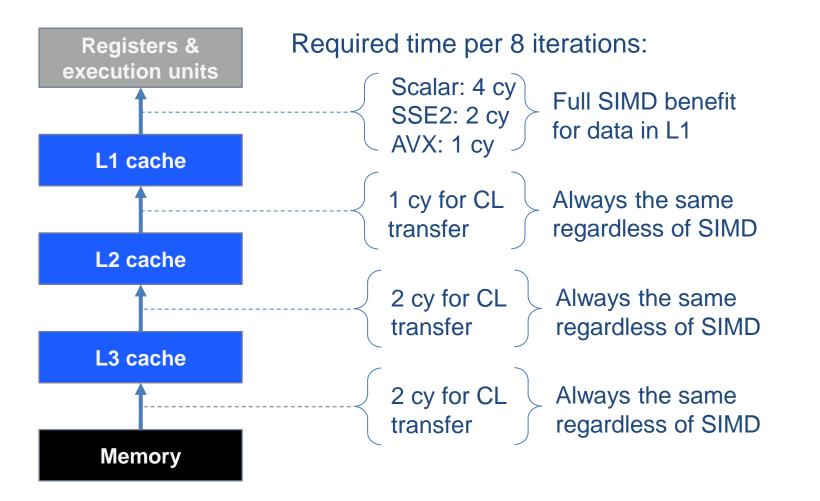

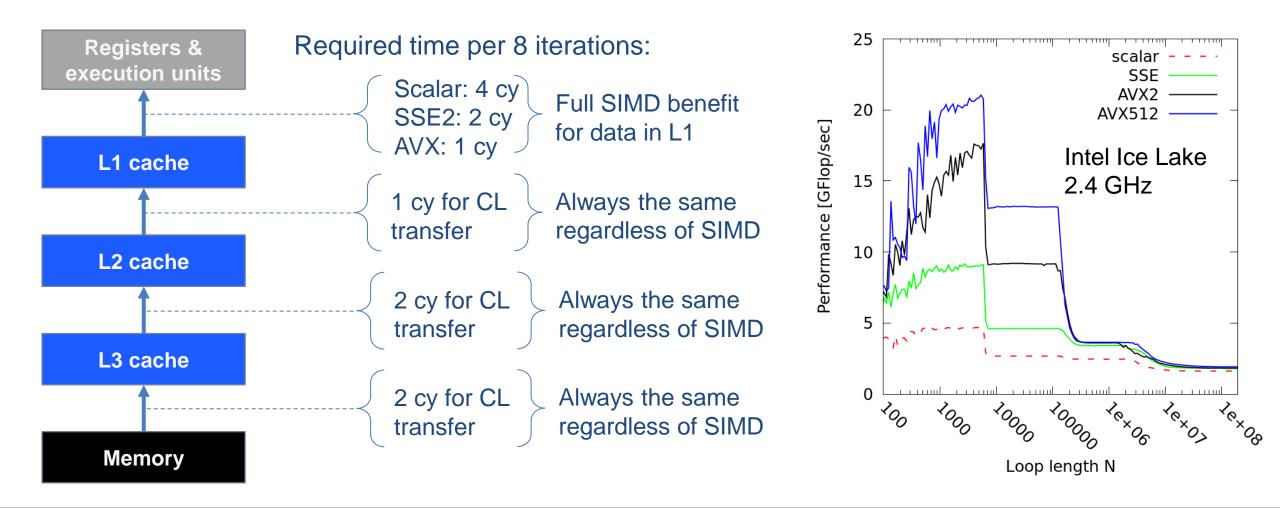

# Memory Hierarchy

### In-cache performance (L2, L3) Main memory performance

You can either build a small and fast memory or a large and slow memory.

### Purpose of many optimizations is to load data from fast memory

Caches help with getting instructions and data to the CPU "fast"

How does data travel from memory to the CPU and back?

CPU registers

Cache

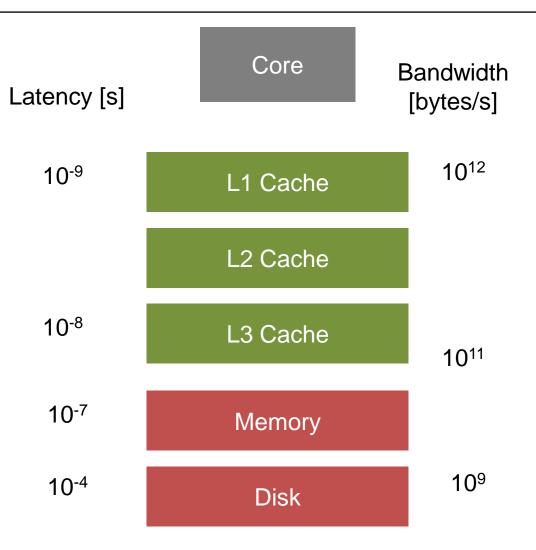

### Data transfers in a memory hierarchy

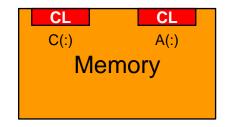

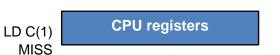

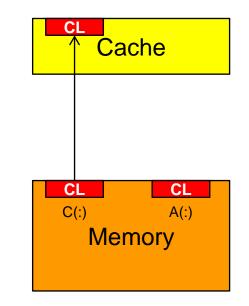

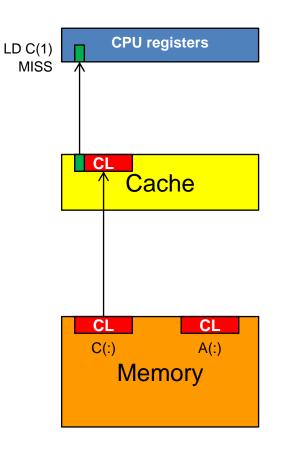

Caches help with getting instructions and data to the CPU "fast" How does data travel from memory to the CPU and back?

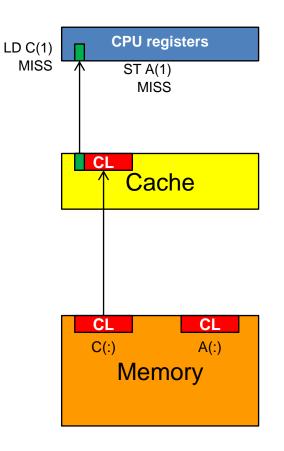

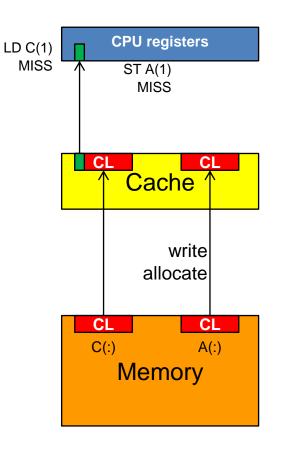

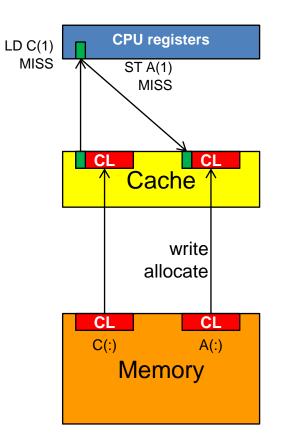

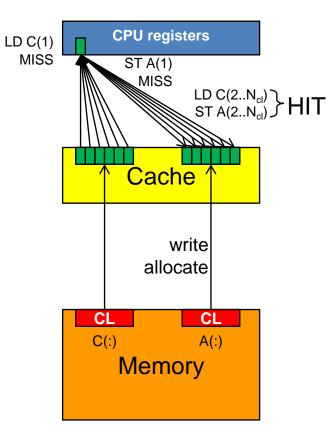

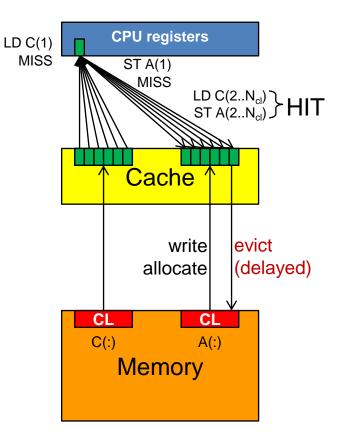

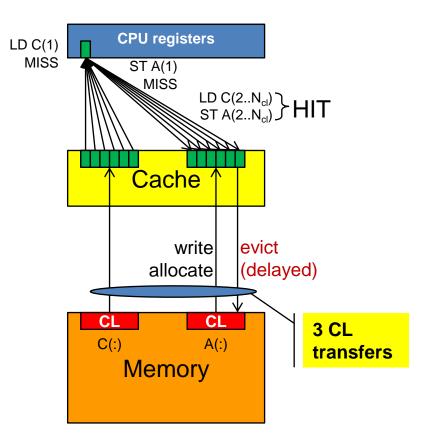

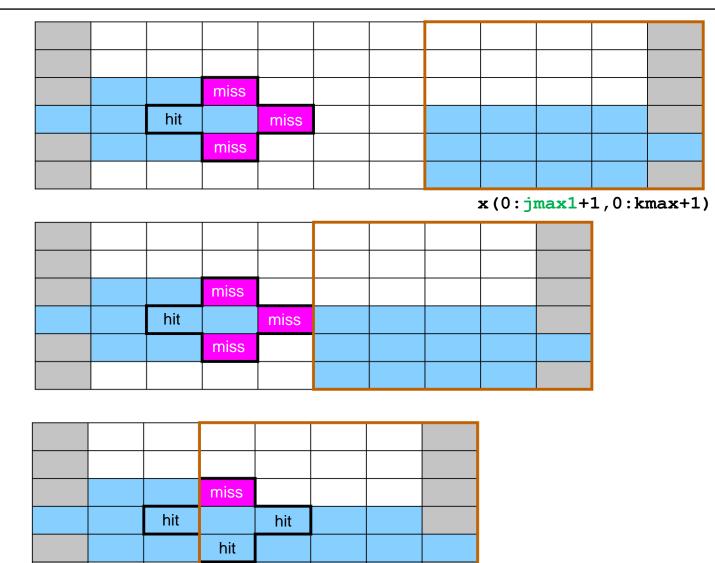

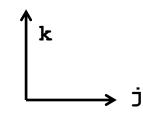

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

Caches help with getting instructions and data to the CPU "fast" How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

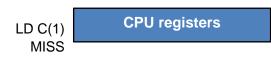

Example: Array copy A(:)=C(:)

**CPU** registers

LD C(1)

## Data transfers in a memory hierarchy

Caches help with getting instructions and data to the CPU "fast" How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

- Example: Array copy A(:)=C(:)

### Data transfers in a memory hierarchy

Caches help with getting instructions and data to the CPU "fast" How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

Example: Array copy A(:)=C(:)

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

**SC23**

Caches help with getting instructions and data to the CPU "fast"

How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

Caches help with getting instructions and data to the CPU "fast"

How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

Caches help with getting instructions and data to the CPU "fast"

How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

Caches help with getting instructions and data to the CPU "fast"

How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

Caches help with getting instructions and data to the CPU "fast" How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

Caches help with getting instructions and data to the CPU "fast" How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

Caches help with getting instructions and data to the CPU "fast" How does data travel from memory to the CPU and back?

- Remember: Caches are organized in cache lines (e.g., 64 bytes)

- Only complete cache lines are transferred between memory hierarchy levels (except registers)

- Registers can only "talk" to the L1 cache

- MISS: Load or store instruction does not find the data in a cache level

- $\rightarrow$  CL transfer required

Friedrich-Alexander-Universität Erlangen-Nürnberg

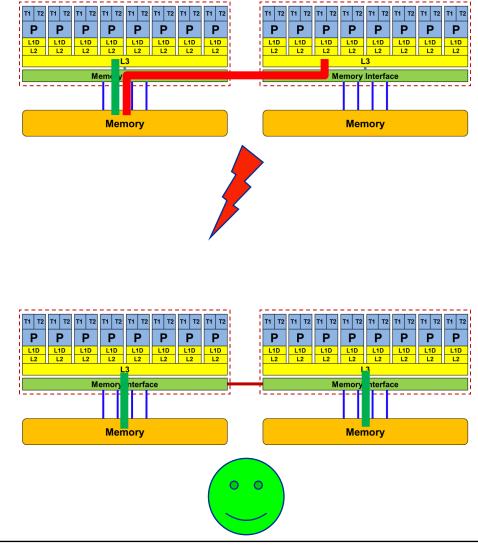

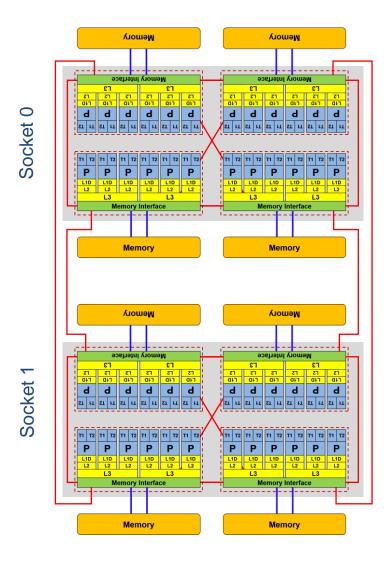

## Multicore

### Node topology and performance

Putting the cores & caches together AMD Epyc 7742 64-Core Processor («Rome»)

- Core features:

- Two-way SMT

- Two 256-bit SIMD FMA units (AVX2)

→16 flops/cycle (actually 24 because 2 ADDs can be done alongside)

- 32 KiB L1 data cache per core

- 512 KiB L2 cache per core

#### Core features:

- Two-way SMT

- Two 256-bit SIMD FMA units (AVX2)

→16 flops/cycle (actually 24 because 2 ADDs can be done alongside)

- 32 KiB L1 data cache per core

- 512 KiB L2 cache per core

- 64 cores per socket hierarchically built up from

- 16 CCX with 4 cores and 16 MiB of L3 cache

- 2 CCX form 1 CCD (silicon die)

- 8 CCDs connected to IO device "Infinity Fabric" (memory controller & PCIe)

#### Core features:

- Two-way SMT

- Two 256-bit SIMD FMA units (AVX2)

→16 flops/cycle (actually 24 because 2 ADDs can be done alongside)

- 32 KiB L1 data cache per core

- 512 KiB L2 cache per core

- 64 cores per socket hierarchically built up from

- 16 CCX with 4 cores and 16 MiB of L3 cache

- 2 CCX form 1 CCD (silicon die)

- 8 CCDs connected to IO device "Infinity Fabric" (memory controller & PCIe)

- 8 channels of DDR4-3200 per IO device

- MemBW: 8 ch x 8 byte x 3.2 GHz = 204.8 GB/s

- ccNUMA-feature (Boot time option):

- Node Per Socket (NPS)=1, 2 or 4

#### Core features:

- Two-way SMT

- Two 256-bit SIMD FMA units (AVX2)

→16 flops/cycle (actually 24 because 2 ADDs can be done alongside)

- 32 KiB L1 data cache per core

- 512 KiB L2 cache per core

- 64 cores per socket hierarchically built up from

- 16 CCX with 4 cores and 16 MiB of L3 cache

- 2 CCX form 1 CCD (silicon die)

- 8 CCDs connected to IO device "Infinity Fabric" (memory controller & PCIe)

- 8 channels of DDR4-3200 per IO device

- MemBW: 8 ch x 8 byte x 3.2 GHz = 204.8 GB/s

- ccNUMA-feature (Boot time option):

- Node Per Socket (NPS)=1, 2 or 4

- NPS=4  $\rightarrow$  4 ccNUMA domains

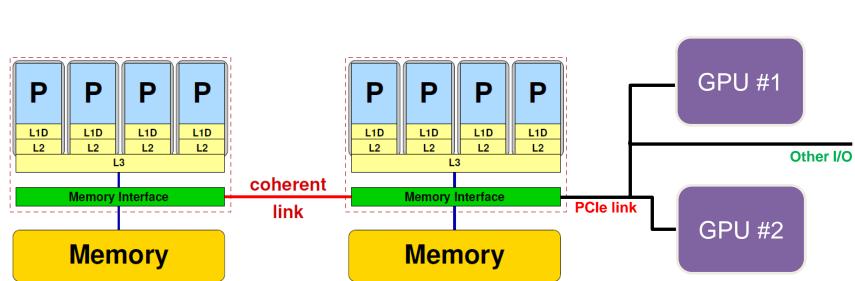

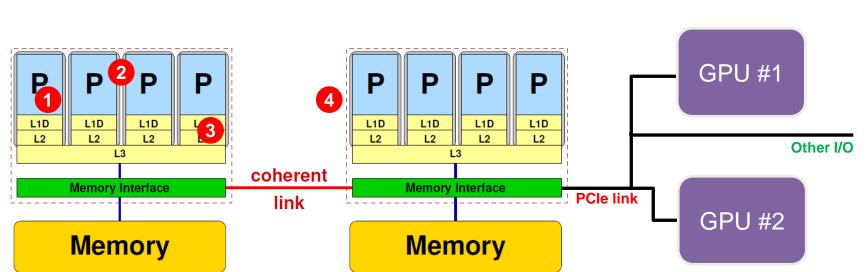

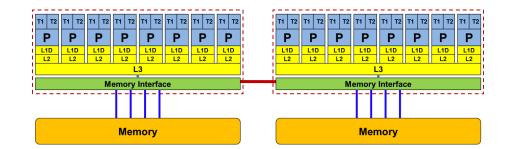

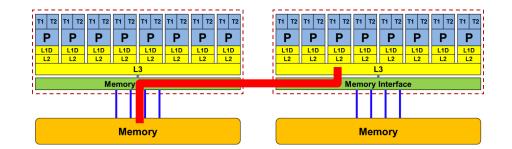

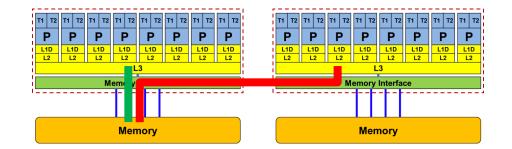

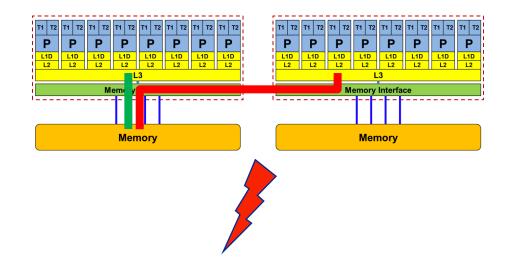

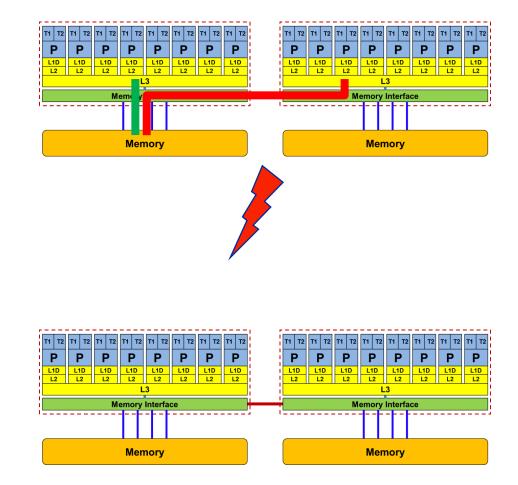

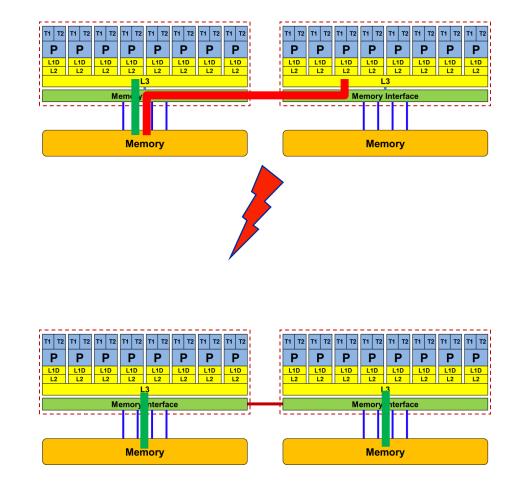

Parallel and shared resources within a shared-memory node

### **Parallel resources:**

- -

### **Shared resources:**

- .

Parallel and shared resources within a shared-memory node

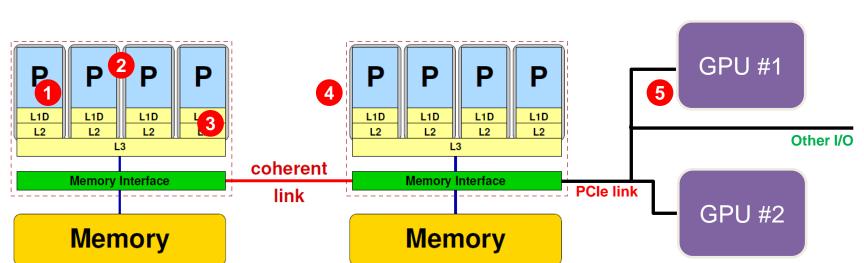

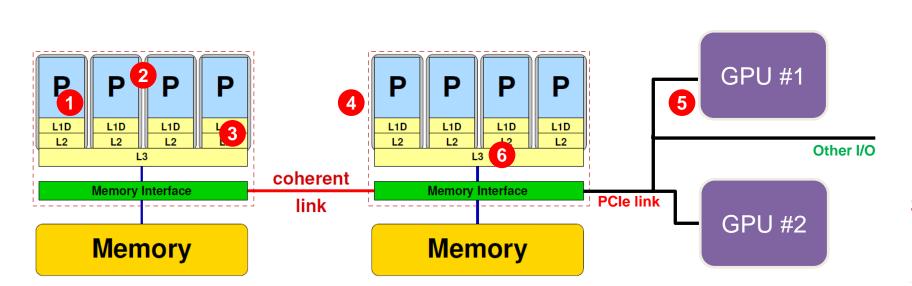

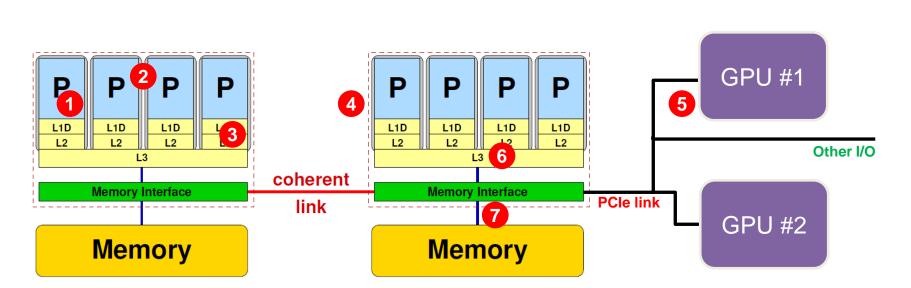

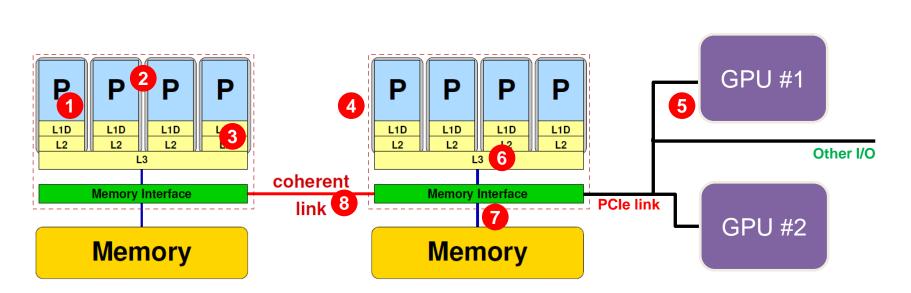

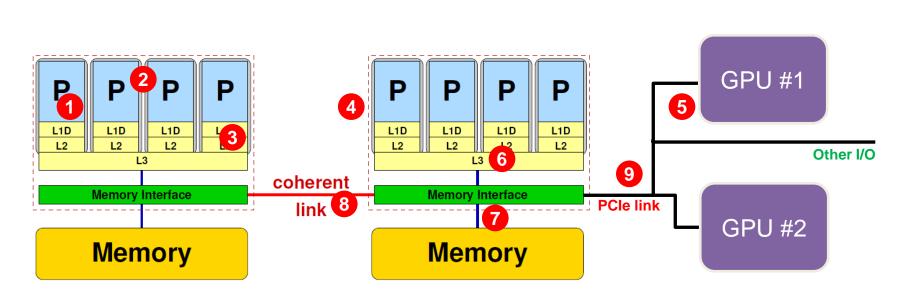

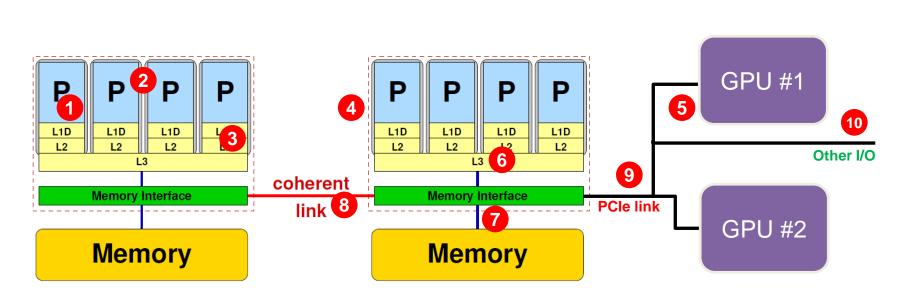

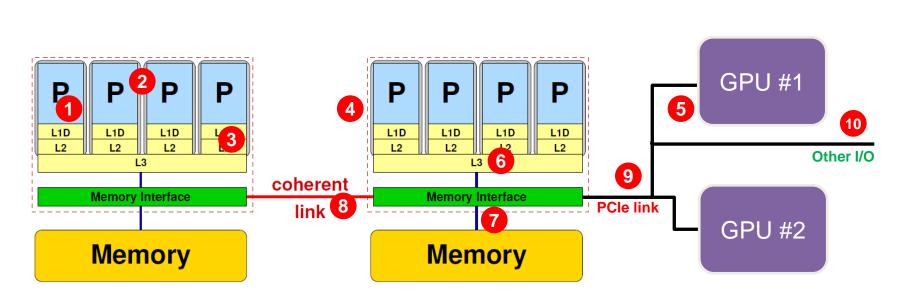

GPU #1 Ρ Ρ Ρ P Ρ Ρ Ρ Ρ L1D L1D L1D L1D L1D L1D L1D L1D L2 L2 L2 L2 L2 L2 L2 L2 Other I/O L3 L3 coherent Memory Interface **Memory Interface PCIe link** link GPU #2 Memory Memory

### **Parallel resources:**

- Execution/SIMD units 1

### **Shared resources:**

Parallel and shared resources within a shared-memory node

### **Parallel resources:**

- Execution/SIMD units 1

- Cores

- .

### **Shared resources:**

Parallel and shared resources within a shared-memory node

#### **Parallel resources:**

Execution/SIMD units 1

- Cores 2

- Inner cache levels

- **Shared resources:**

Parallel and shared resources within a shared-memory node

#### **Parallel resources:**

- Execution/SIMD units 1

- Cores

- Inner cache levels 3

- Sockets / ccNUMA domains

### **Shared resources:**

Parallel and shared resources within a shared-memory node

#### **Parallel resources:**

- Execution/SIMD units 1

- Cores

- Inner cache levels 3

- Sockets / ccNUMA domains

- Multiple accelerators 5

### **Shared resources:**

Parallel and shared resources within a shared-memory node

#### **Parallel resources:**

- Execution/SIMD units 1

- Cores

- Inner cache levels 3

- Sockets / ccNUMA domains

- Multiple accelerators 5

### **Shared resources:**

Outer cache level per socket

Parallel and shared resources within a shared-memory node

#### **Parallel resources:**

- Execution/SIMD units 1

- Cores

- Inner cache levels 3

- Sockets / ccNUMA domains

- Multiple accelerators 5

#### **Shared resources:**

- Outer cache level per socket

- Memory bus per socket 7

Parallel and shared resources within a shared-memory node

#### **Parallel resources:**

- Execution/SIMD units 1

- Cores

- Inner cache levels 3

- Sockets / ccNUMA domains

- Multiple accelerators 5

#### **Shared resources:**

- Outer cache level per socket

- Memory bus per socket 7

- Intersocket link 8

Parallel and shared resources within a shared-memory node

#### **Parallel resources:**

- Execution/SIMD units 1

- Cores

- Inner cache levels 3

- Sockets / ccNUMA domains

- Multiple accelerators 5

#### **Shared resources:**

- Outer cache level per socket

- Memory bus per socket 7

- Intersocket link 8

- PCIe bus(es) 9

Parallel and shared resources within a shared-memory node

#### **Parallel resources:**

- Execution/SIMD units 1

- Cores

- Inner cache levels 3

- Sockets / ccNUMA domains

- Multiple accelerators 5

### **Shared resources:**

- Outer cache level per socket

- Memory bus per socket 7

- Intersocket link 8

- PCIe bus(es) 9

- Other I/O resources 10

Parallel and shared resources within a shared-memory node

### **Parallel resources:**

- Execution/SIMD units 1

- Cores

- Inner cache levels 3

- Sockets / ccNUMA domains

- Multiple accelerators 5

### **Shared resources:**

- Outer cache level per socket

- Memory bus per socket 7

- Intersocket link 8

- PCIe bus(es) 9

- Other I/O resources 10

## How does your application react to all of those details?

Friedrich-Alexander-Universität Erlangen-Nürnberg

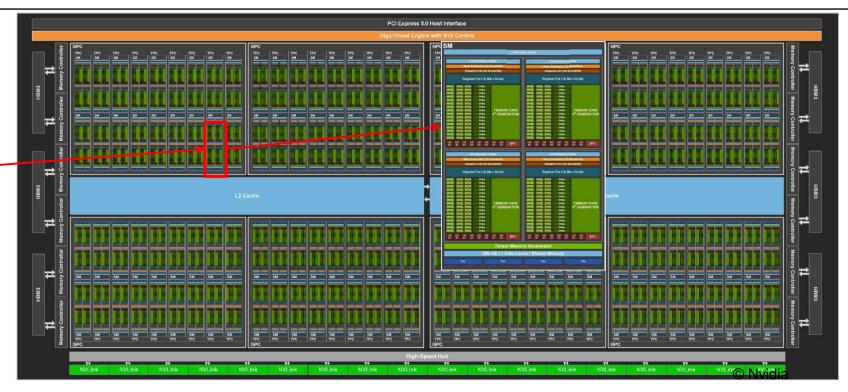

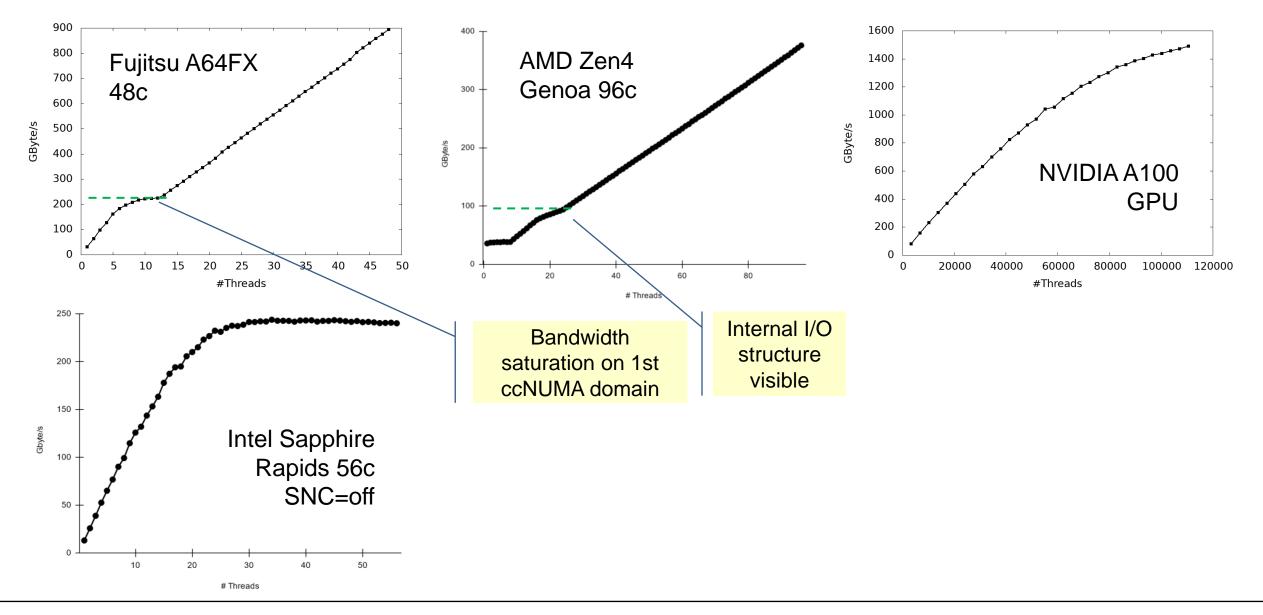

# **GPGPU** accelerators

NVIDIA "Hopper" H100 vs. AMD Zen4 "Genoa"

- 80 B Transistors

- ~ 1.8 GHz clock speed

- ~ 144 "SM" units

- 128 SP "cores" each (FMA)

- 64 DP "cores" each (FMA)

- 4 "Tensor Cores" each

- 2:1 SP:DP performance

- ~ 34 TFlop/s DP peak (FP64)

- 50 MiB L2 Cache

- 80 GB HBM3

- MemBW ~ 3300 GB/s (theoretical)

- MemBW ~ 3000 GB/s (measured)

- 80 B Transistors

- ~ 1.8 GHz clock speed

- ~ 144 "SM" units

- 128 SP "cores" each (FMA)

- 64 DP "cores" each (FMA)

- 4 "Tensor Cores" each

- 2:1 SP:DP performance

- ~ 34 TFlop/s DP peak (FP64)

- 50 MiB L2 Cache

- 80 GB HBM3

- MemBW ~ 3300 GB/s (theoretical)

- MemBW ~ 3000 GB/s (measured)

- 80 B Transistors

- ~ 1.8 GHz clock speed

- ~ 144 "SM" units

- 128 SP "cores" each (FMA)

- 64 DP "cores" each (FMA)

- 4 "Tensor Cores" each

- 2:1 SP:DP performance

- ~ 34 TFlop/s DP peak (FP64)

- 50 MiB L2 Cache

- 80 GB HBM3

- MemBW ~ 3300 GB/s (theoretical)

- MemBW ~ 3000 GB/s (measured)

$$P_{peak}^{DP} = n_{SM} \cdot n_{core} \cdot n_{FP} \cdot f$$

# SMs

# CUDA

# FP

ops/cy

- 80 B Transistors

- ~ 1.8 GHz clock speed

- ~ 144 "SM" units

- 128 SP "cores" each (FMA)

- 64 DP "cores" each (FMA)

- 4 "Tensor Cores" each

- 2:1 SP:DP performance

- ~ 34 TFlop/s DP peak (FP64)

- 50 MiB L2 Cache

- 80 GB HBM3

- MemBW ~ 3300 GB/s (theoretical)

- MemBW ~ 3000 GB/s (measured)

$$P_{peak}^{DP} = n_{SM} \cdot n_{core} \cdot n_{FP} \cdot f$$

$$n_{SM} = 144$$

$$n_{core} = 64$$

$$n_{FP} = 2 \frac{\text{flops}}{\text{cy}}$$

$$f = 1.8 \frac{\text{Gcy}}{\text{S}}$$

# Trading single thread performance for parallelism: *GPGPUs vs. CPUs*

| GPU vs. CPU<br>light speed estimate<br>(per processor chip) | Control            | ALU<br>ALU | ALU ALU |                                |

|-------------------------------------------------------------|--------------------|------------|---------|--------------------------------|

|                                                             | DRAM               |            |         | DRAM                           |

|                                                             | CI                 | PU         |         | GPU                            |

|                                                             | 2 x AMD EPYC S     | 9654 "G    | enoa"   | NVidia Tesla H100 SXM "Hopper" |

| Cores@Clock                                                 | 2 x 96 @ 2         | 2.4 GHz    |         | 144 SMs @ ~1.8 GHz             |

| FP32 Performance/core                                       | 76.8 GF            | lop/s      |         | ~ 230 GFlop/s                  |

| Threads@STREAM                                              | ~ 24               | 4          |         | ~ 100000                       |

| FP32 peak                                                   | 14.7 TF            | lop/s      |         | ~ 67 TFlop/s                   |

| Stream BW (meas.)                                           | 2 x 360            | GB/s       |         | ~ 3000 GB/s                    |

| Transistors / TDP                                           | ~ 2x 80 (?) Billic | on / 2x 3  | 60 W    | 80 Billion/700 W               |

## **Conclusions about architecture**

- Performance is a result of

- How many instructions you require to implement an algorithm

- How efficiently those instructions are executed on a processor

- Runtime contribution of the triggered data transfers

- Modern computer architecture has a rich "topology"

- Node-level hardware parallelism takes many forms

- Sockets/devices CPU: 1-4 or more, GPGPU: 1-8

- Cores moderate (CPU: 20-128, GPGPU: 10-100)

- SIMD moderate (CPU: 2-16) to massive (GPGPU: 10's-100's)

- Superscalarity (CPU: 2-6)

- Exploiting performance: parallelism + bottleneck awareness

- "High Performance Computing" == computing at a bottleneck

- Performance of programs is sensitive to architecture

Friedrich-Alexander-Universität Erlangen-Nürnberg

# **Multicore Performance and Tools**

## Part 1: Topology, affinity control, clock speed

# **Tools for Node-level Performance Engineering**

## Node Information

/proc/cpuinfo, numactl, hwloc, likwid-topology, likwid-powermeter

- Affinity control and data placement OpenMP and MPI runtime environments, hwloc, numactl, likwid-pin

- Runtime Profiling Compilers, gprof, perf, HPCToolkit, Intel Amplifier, gprof-ng, ...

- Performance Analysis Intel VTune, likwid-perfctr, PAPI-based tools, HPCToolkit, perf

- Microbenchmarking

STREAM, likwid-bench, lmbench, uarch-bench

Friedrich-Alexander-Universität Erlangen-Nürnberg

DEMO

# **Reporting topology**

## likwid-topology

Node-Level Performance Engineering

# Output of likwid-topology

| CPU name: In                  | tel(R) Xeon(R)        | Platinum 83 | 60Y CPU @ 2 | .40GHz       |                |                            |

|-------------------------------|-----------------------|-------------|-------------|--------------|----------------|----------------------------|

| CPU type: In                  | tel Icelake SP        | processor   |             |              |                |                            |

| CPU stepping                  | r: 6                  |             |             |              |                |                            |

| *******                       | *****                 | *********   | ********    | ***********  | *****          | * * *                      |

| Hardware Thr                  | ead Topology          |             |             |              |                |                            |

|                               | *****                 | *********   | ********    | ************ | ****           | * * *                      |

| Sockets:                      | 2                     |             |             |              |                |                            |

| Cores per so                  | ocket: 36             |             |             |              |                |                            |

| Threads per                   | core: 1               |             |             |              |                |                            |

| micado per                    | 0010. 1               |             |             |              |                |                            |

|                               | Thread                | Core        | Die         | Socket       | Available      |                            |

| HWThread                      |                       | Core<br>0   | Die<br>0    | Socket<br>0  | Available<br>* |                            |

| HWThread                      | Thread                |             |             |              |                | All physical               |

| HWThread<br>0<br>2            | Thread<br>0           | 0           | 0           | 0            | *              | All physical processor IDs |

| HWThread<br>0<br>1<br>2<br>[] | Thread<br>0<br>0      | 0<br>1<br>2 | 0<br>0      | 0<br>0       | *              |                            |

| HWThread<br>0<br>1<br>2       | Thread<br>0<br>0      | 0<br>1      | 0<br>0      | 0<br>0       | *              |                            |

| HWThread<br>0<br>1<br>2<br>[] | Thread<br>0<br>0<br>0 | 0<br>1<br>2 | 0<br>0<br>0 | 0<br>0<br>0  | *<br>*<br>*    |                            |

optional

| Output o                             | t likwid-topology                                                                                                                                                     |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ****                                 | **************************************                                                                                                                                |

| Cache Topology<br>****************** | ****                                                                                                                                                                  |

| Level:                               | 1                                                                                                                                                                     |

| Size:                                | 48 kB                                                                                                                                                                 |

| Cache groups:                        | (0)(1)(2)(3)(4)(5)(64)(65)(66)(67)(68)(69)(70)(71)                                                                                                                    |

| Level:                               | 2                                                                                                                                                                     |

| Size:                                | 1.25 MB                                                                                                                                                               |

| Cache groups:                        | (0)(1)(2)(3)(4)(5)(64)(65)(66)(67)(68)(69)(70)(71)                                                                                                                    |

| Level:                               | 3                                                                                                                                                                     |

| Size:                                | 54 MB                                                                                                                                                                 |

| Туре:                                | Unified cache                                                                                                                                                         |

| Associativity:                       | 12                                                                                                                                                                    |

| Number of sets:                      | 73728 Additional cache info                                                                                                                                           |

| Cache line size:                     | 64 with -c option                                                                                                                                                     |

| Cache type:                          | Non Inclusive                                                                                                                                                         |

| Shared by threads:                   | 36                                                                                                                                                                    |

| Cache groups:                        | ( 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 23 24 25 26 27 28 29 30 31 32 33 34 35 )<br>( 36 37 38 39 40 41 42 43 44 45 46 47 48 59 60 61 62 63 64 65 66 67 68 69 70 71 ) |

# Output of likwid-topology

| Output of likwid-topology              |                                                           |                                                     |  |  |  |

|----------------------------------------|-----------------------------------------------------------|-----------------------------------------------------|--|--|--|

| ************************************** | *********************                                     |                                                     |  |  |  |

|                                        | *****                                                     |                                                     |  |  |  |

| NUMA domains:                          | 4 4                                                       | Output similar to                                   |  |  |  |

| Domain:                                | 0                                                         |                                                     |  |  |  |

| Processors:                            | (01234567891011121314151617)                              |                                                     |  |  |  |

| Distances:                             | 10 11 20 20                                               | Sockets: 2                                          |  |  |  |

| Free memory:                           | 119059 MB                                                 | Threads per core:1                                  |  |  |  |

| Total memory:                          | 128553 МВ                                                 |                                                     |  |  |  |

| <br>Domain:<br>-                       | 1                                                         | Sub-NUMA clustering (SNC)<br>enabled, SMT disabled! |  |  |  |

|                                        | ( 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 ) |                                                     |  |  |  |

|                                        | 11 10 20 20<br>100106 ND                                  |                                                     |  |  |  |

| Free memory:                           |                                                           |                                                     |  |  |  |

| Total memory:                          | 129020 МВ                                                 |                                                     |  |  |  |

| Domain:                                | 2                                                         |                                                     |  |  |  |

| Processors:                            | ( 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 ) |                                                     |  |  |  |

| Distances:                             | 20 20 10 11                                               |                                                     |  |  |  |

| Free memory:                           | 128033 MB                                                 |                                                     |  |  |  |

| Total memory:                          | 128978 MB                                                 |                                                     |  |  |  |

| Domain:                                | 3                                                         |                                                     |  |  |  |

| Processors:                            | ( 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 ) |                                                     |  |  |  |

| Distances:                             | 20 20 11 10                                               |                                                     |  |  |  |

| Free memory:                           | 128719 MB                                                 |                                                     |  |  |  |

| —                                      | 129017 MB                                                 |                                                     |  |  |  |

Friedrich-Alexander-Universität Erlangen-Nürnberg

DEMO

# Enforcing thread/process affinity under Linux OS

## likwid-pin

https://youtu.be/PSJKNQaqwB0

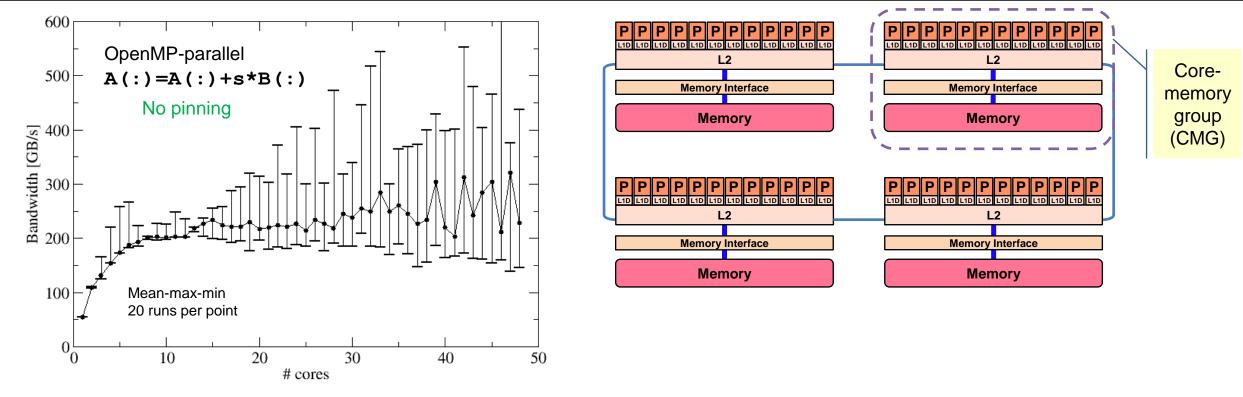

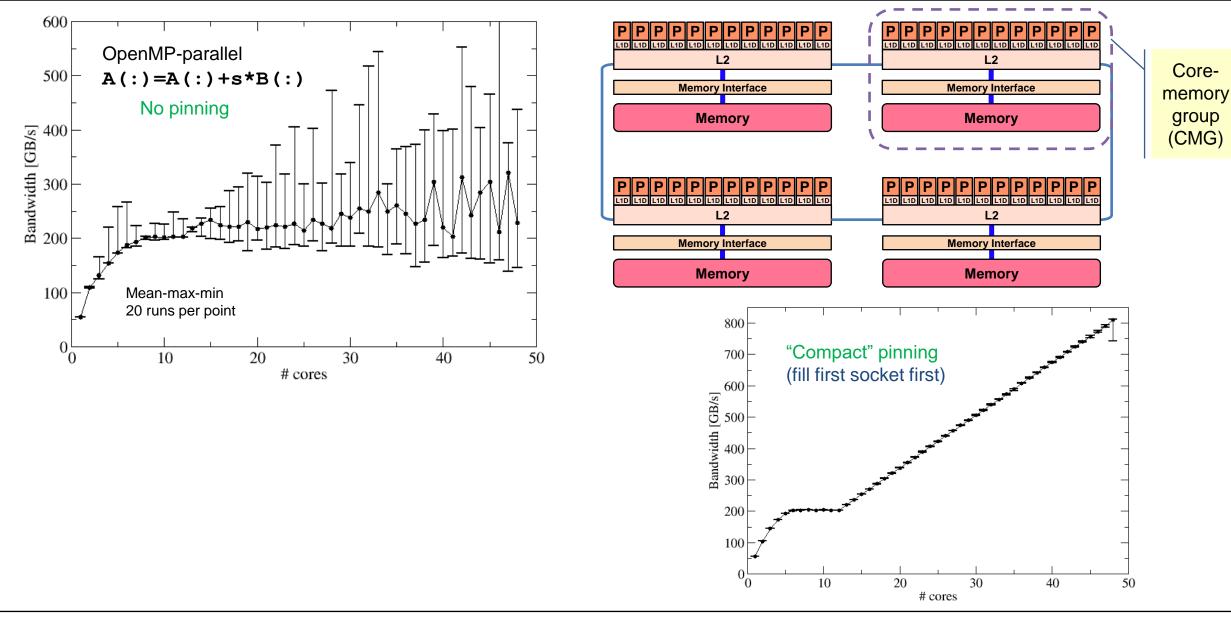

## DAXPY test on A64FX

### Anarchy vs. thread pinning

## DAXPY test on A64FX

### Anarchy vs. thread pinning

## DAXPY test on A64FX

### Anarchy vs. thread pinning

- Eliminating performance variation

- Making use of architectural features

- Avoiding resource contention

# More thread/process affinity ("pinning") options

- Highly OS-dependent system calls but available on all systems

- Linux: sched\_setaffinity()

- Windows: SetThreadAffinityMask()

- Hwloc project (<u>http://www.open-mpi.de/projects/hwloc/</u>)

- Support for "semi-automatic" pinning

- All modern compilers with OpenMP support OpenMP 4.0 (OMP\_PLACES, OMP\_PROC\_BIND)

- CPUset reduction utils: taskset or numactl

- Job scheduler like SLURM

- Affinity awareness in MPI libraries (OpenMPI, Intel MPI, ...)

- Or likwid-pin and likwid-mpirun

https://youtu.be/IKW0kRLnhyc

# Overview likwid-pin

- Pins processes and threads to specific cores without touching code

- Directly supports pthreads, gcc OpenMP, Intel OpenMP

- Based on combination of wrapper tool together with overloaded pthread library

→ binary must be dynamically linked!

- Supports logical core numbering within topological entities (thread domains)

- Simple usage with physical (kernel) core IDs:

- \$ likwid-pin -c 0-3,4,6 ./myApp parameters

- \$ OMP\_NUM\_THREADS=4 likwid-pin -c 0-9 ./myApp params

- Simple usage with logical IDs ("thread groups expressions"):

- \$ likwid-pin -c S0:0-7 ./myApp params

- \$ likwid-pin -c C1:0-2 ./myApp params

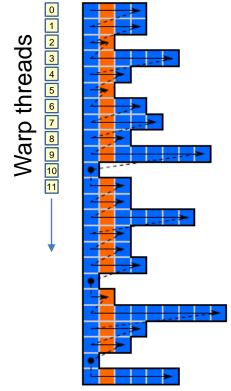

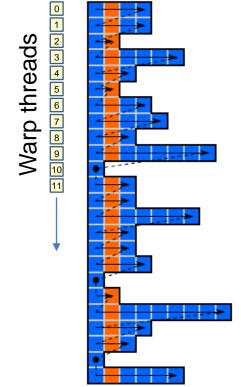

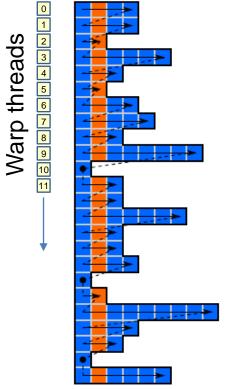

# LIKWID terminology: Thread group syntax

- The OS numbers all processors (hardware threads) on a node

- The numbering is enforced at boot time by the BIOS

- LIKWID introduces thread domains consisting of hardware threads sharing a topological entity (e.g. socket or shared cache)

- A thread domain is defined by a single character + index

----+ +----+ +----+ +----+ Example for likwid-pin: likwid-pin -c S0:0-3 ./a.out Thread group expressions may be chained with @: likwid-pin -c S0:0-2@S1:0-2 ./a.out

-----+ +-----+ +-----+ +-----+ || +-----+ +-----+ +-----+

-----+ +-----+ +-----+ +-----+ || +-----+ +-----+ +-----+

| 1 9 | | 2 10 | | 3 11 | || | 4 12 | | 5 13 | | 6 14 | | 7 15 |

48

Physical cores first!

4 | 1 5 | 2 6 | 3 7 | +----+ +----+ +----+ +----+

## Available thread domains/unit prefixes (LIKWID 5.2)

## Available thread domains/unit prefixes (LIKWID 5.2)

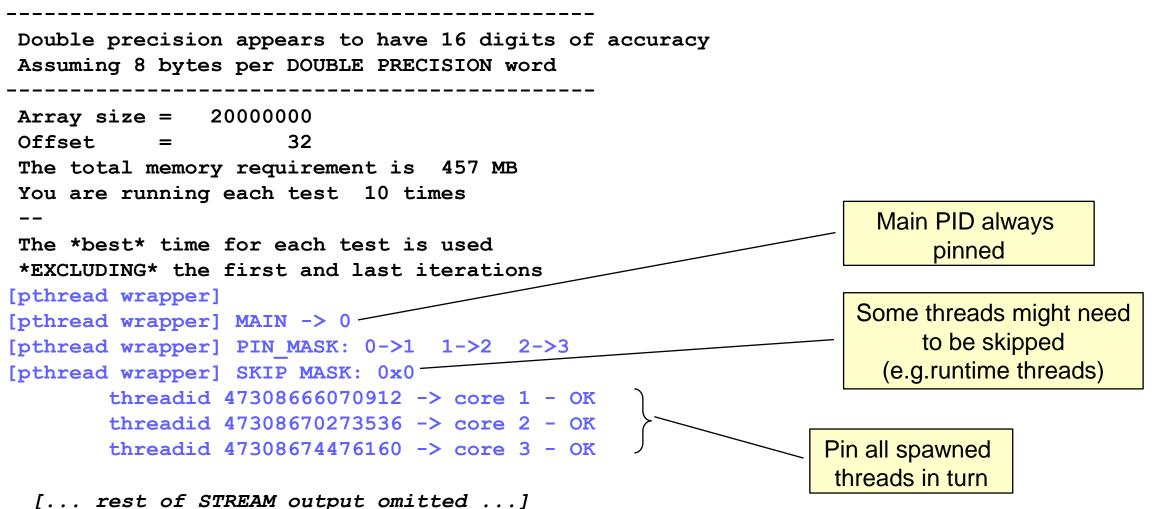

## Example: likwid-pin with Intel OpenMP

#### Running the STREAM benchmark with likwid-pin:

\$ likwid-pin -c S0:0-3 ./stream

Processor: smallest entity able to run a thread or task (hardware thread) Place: one or more processors  $\rightarrow$  thread pinning is done place by place Free migration of the threads on a place between the processors of that place.

Or use explicit numbering, e.g. 8 places, each consisting of 4 processors:

- OMP\_PLACES="{0,1,2,3}, {4,5,6,7}, {8,9,10,11}, ... {28,29,30,31}"

- OMP\_PLACES="{0:4}, {4:4}, {8:4}, ... {28:4}"

- OMP\_PLACES="{0:4}:8:4"

Processor: smallest entity able to run a thread or task (hardware thread) Place: one or more processors  $\rightarrow$  thread pinning is done place by place Free migration of the threads on a place between the processors of that place.

| OMP_PLACES                | Place ==                        |

|---------------------------|---------------------------------|

| threads                   | Hardware thread (hyper-thread)  |

| cores                     | All HW threads of a single core |

| sockets                   | All HW threads of a socket      |

| abstract_name(num_places) | Restrict # of places available  |

Or use explicit numbering, e.g. 8 places, each consisting of 4 processors:

- OMP\_PLACES="{0,1,2,3},{4,5,6,7},{8,9,10,11}, ... {28,29,30,31}"

- OMP\_PLACES="{0:4}, {4:4}, {8:4}, ... {28:4}"

- OMP\_PLACES="{0:4}:8:4"

Processor: smallest entity able to run a thread or task (hardware thread) Place: one or more processors  $\rightarrow$  thread pinning is done place by place Free migration of the threads on a place between the processors of that place.

| abstract name  | OMP_PLACES                           | Place ==                        |

|----------------|--------------------------------------|---------------------------------|

| aboliactinanie | threads                              | Hardware thread (hyper-thread)  |

|                | cores                                | All HW threads of a single core |

|                | sockets                              | All HW threads of a socket      |

|                | <pre>abstract_name(num_places)</pre> | Restrict # of places available  |

Or use explicit numbering, e.g. 8 places, each consisting of 4 processors:

- OMP\_PLACES="{0,1,2,3}, {4,5,6,7}, {8,9,10,11}, ... {28,29,30,31}"

- OMP\_PLACES="{0:4}, {4:4}, {8:4}, ... {28:4}" >

- OMP\_PLACES=" { 0 : 4 } : 8 : 4 "

<lower-bound>:<number of entries>[:<stride>]

Processor: smallest entity able to run a thread or task (hardware thread) Place: one or more processors  $\rightarrow$  thread pinning is done place by place Free migration of the threads on a place between the processors of that place.

| abstract name  | OMP_PLACES                           | Place ==                        |

|----------------|--------------------------------------|---------------------------------|

| aboliactitatio | threads                              | Hardware thread (hyper-thread)  |

|                | cores                                | All HW threads of a single core |

|                | sockets                              | All HW threads of a socket      |

|                | <pre>abstract_name(num_places)</pre> | Restrict # of places available  |

Or use explicit numbering, e.g. 8 places, each consisting of 4 processors:

- OMP\_PLACES="{0,1,2,3},{4,5,6,7},{8,9,10,11}, ... {28,29,30,31}"

- OMP\_PLACES="{0:4}, {4:4}, {8:4}, ... {28:4}" >

- OMP\_PLACES="{0:4}:8:4"

Caveat: Actual behavior is implementation defined!

<lower-bound>:<number of entries>[:<stride>]

## OMP\_PROC\_BIND variable / proc\_bind() clause

#### Determines how places are used for pinning:

| OMP_PROC_BIND | Meaning                                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------------------|

| FALSE         | Affinity disabled                                                                                           |

| TRUE          | Affinity enabled, implementation defined strategy                                                           |

| CLOSE         | Threads bind to consecutive places                                                                          |

| SPREAD        | Threads are evenly scattered among places                                                                   |

| MASTER        | Threads bind to the same place as the master thread that was running before the parallel region was entered |

If there are more threads than places, consecutive threads are put into individual places ("balanced")

## Some simple OMP\_PLACES examples

Intel Xeon w/ SMT, 2x10 cores, 1 thread per physical core, fill 1 socket OMP\_NUM\_THREADS=10 OMP\_PLACES=cores OMP\_PROC\_BIND=close Always prefer abstract places instead of HW thread IDs!

Intel Xeon, 2 sockets, 4 threads per socket (no binding within socket!) OMP\_NUM\_THREADS=8 OMP\_PLACES=sockets OMP\_PROC\_BIND=close # spread will also do

Intel Xeon, 2 sockets, 4 threads per socket, binding to cores OMP\_NUM\_THREADS=8 OMP\_PLACES=cores OMP\_PROC\_BIND=spread

# MPI startup and hybrid pinning: likwid-mpirun

- How do you manage affinity with MPI or hybrid MPI/threading?

- In the long run a unified standard is needed

- Till then, likwid-mpirun provides a portable/flexible solution

- The examples here are for Intel MPI/OpenMP programs, but are also applicable to other threading models

Pure MPI:

\$ likwid-mpirun -np 16 -nperdomain S:2 ./a.out

Hybrid:

\$ likwid-mpirun -np 16 -pin S0:0,1\_S1:0,1 ./a.out

## likwid-mpirun 1 MPI process per socket

\$ likwid-mpirun -np 4 -pin S0:0-5\_S1:0-5 ./a.out

\$ likwid-mpirun -np 4 -nperdomain S:1 6 ./a.out

| 32kB     32kB     32kB     32kB     32kB       256kB     256kB     256kB     256kB     256kB | 32kB       32kB       32kB       32kB       32kB       32kB         256kB       256kB       256kB       256kB       256kB       256kB |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 12 MB                                                                                        | 12 MB                                                                                                                                 |

|                                                                                              |                                                                                                                                       |

|                                                                                              |                                                                                                                                       |

|                                                                                              |                                                                                                                                       |

|                                                                                              |                                                                                                                                       |

| 32kB         32kB         32kB         32kB         32kB                                     | 32kB         32kB         32kB         32kB         32kB         32kB                                                                 |

|                                                                                              |                                                                                                                                       |

Intel MPI + compiler:

OMP\_NUM\_THREADS=6 mpirun -ppn 2 -np 4 -env I\_MPI\_PIN\_DOMAIN socket -env KMP\_AFFINITY scatter ./a.out

Friedrich-Alexander-Universität Erlangen-Nürnberg

## Microbenchmarking for architectural exploration

Probing of the memory hierarchy

Saturation effects

OpenMP barrier overhead

## Motivation for Microbenchmarking as a tool

- Isolate small kernels to:

- Separate influences

- Determine specific machine capabilities (light speed)

- Gain experience about software/hardware interaction

- Determine programming model overhead

- • •

- Possibilities:

- Readymade benchmark collections (epcc OpenMP, IMB)

- STREAM benchmark for memory bandwidth

- Implement own benchmarks (difficult and error prone)

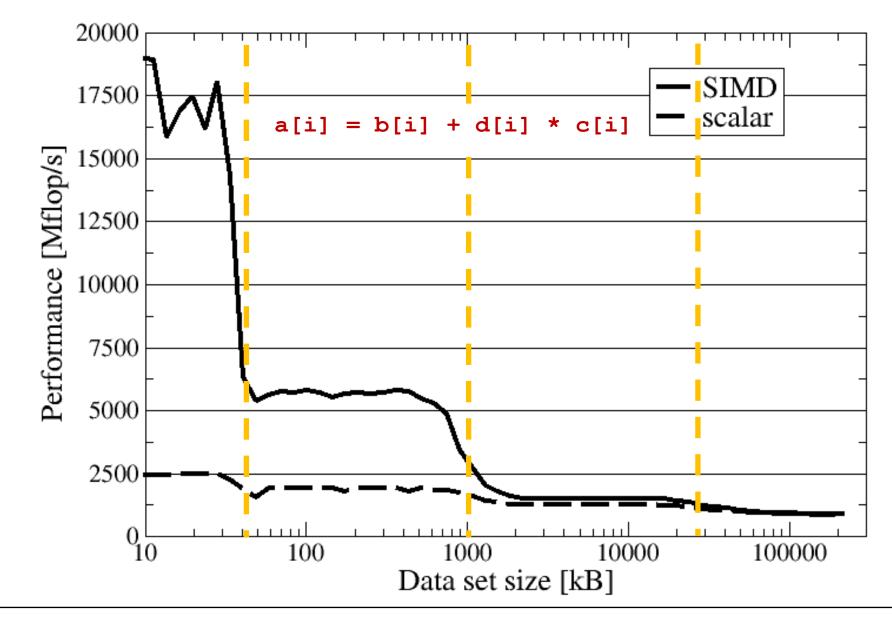

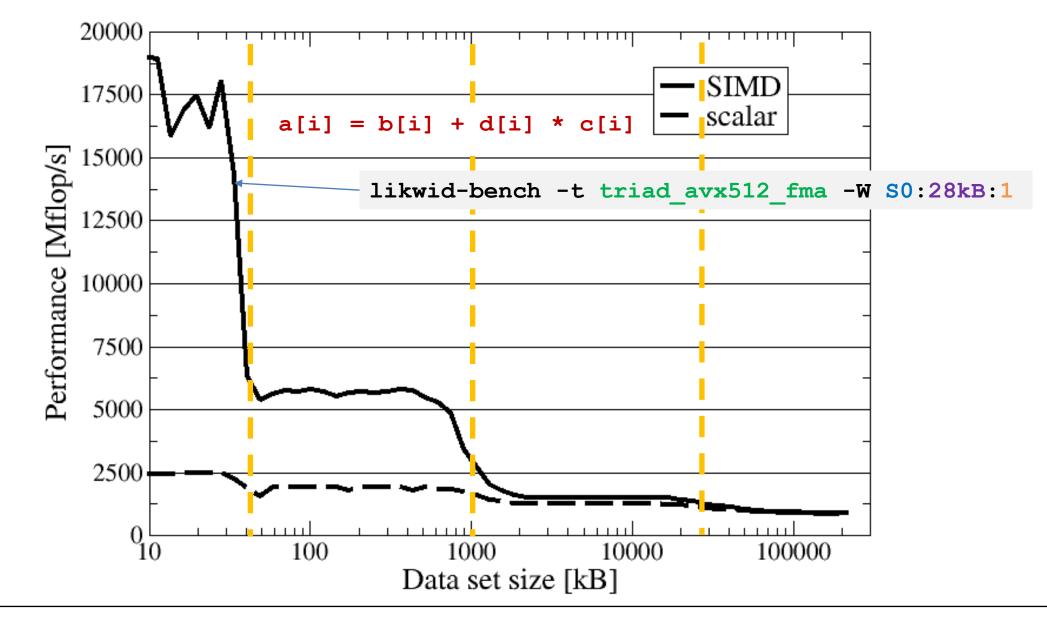

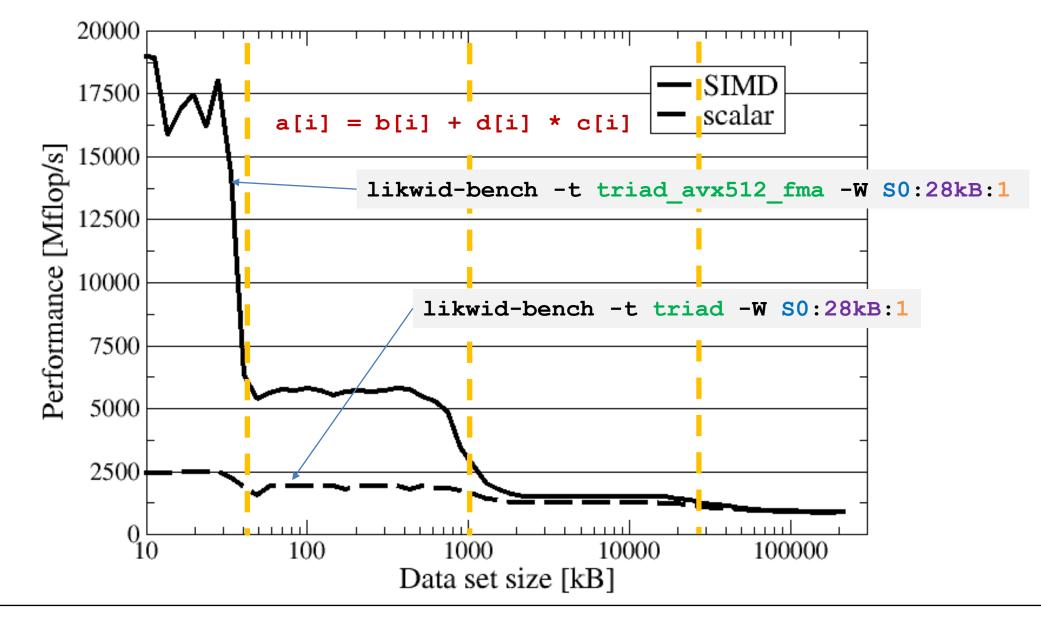

- likwid-bench tool: Offers collection of benchmarks and framework for rapid development of assembly code kernels

#### likwid-bench

- Microbenchmarking in high-level language is often difficult

- Solution: assembly-based microbenchmarking framework

- e.g., likwid-bench

- \$ likwid-bench -t triad\_avx512\_fma -W S0:28kB:1

benchmark type topological entity (see likwid-pin) working set

# of threads

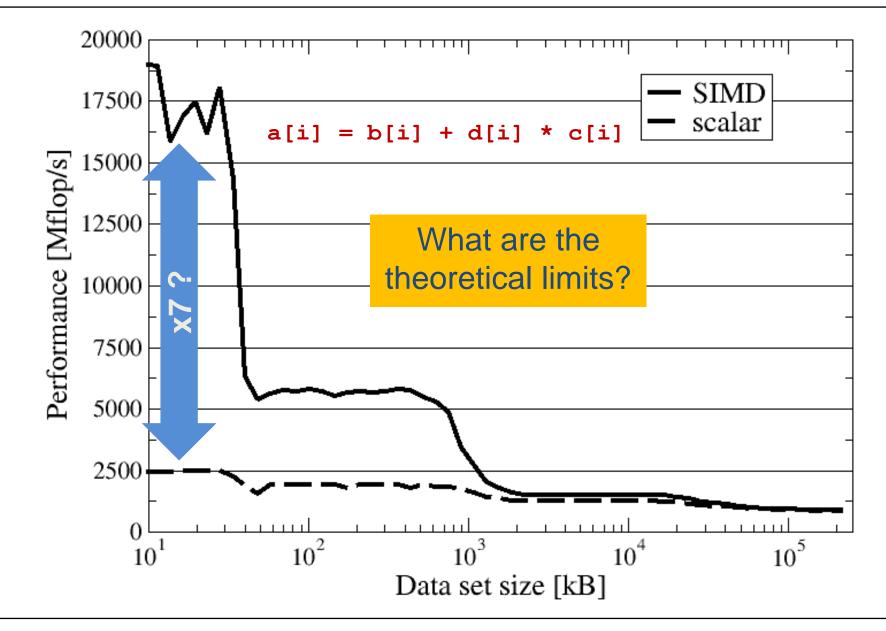

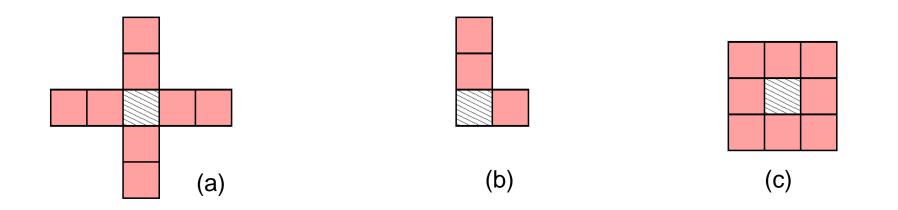

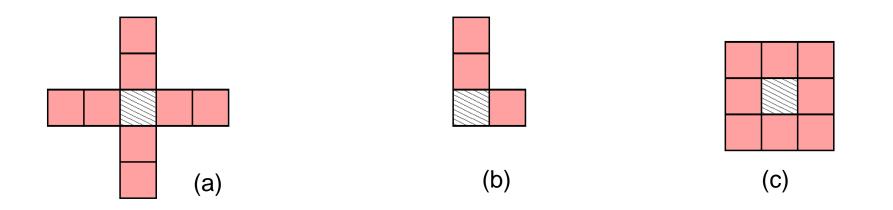

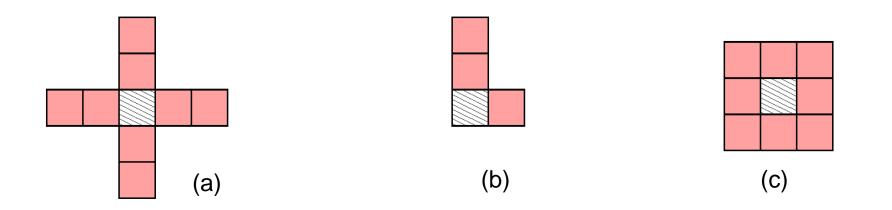

Classic benchmark: Schönauer Triad a[i] = b[i] + d[i] \* c[i]

This kernel is limited by data transfer performance for all memory levels on all architectures, ever!

Node-Level Performance Engineering

Node-Level Performance Engineering

Node-Level Performance Engineering

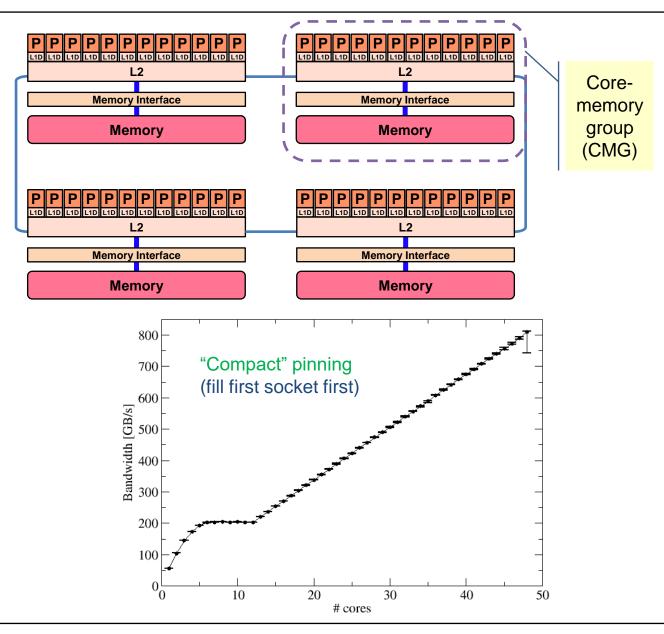

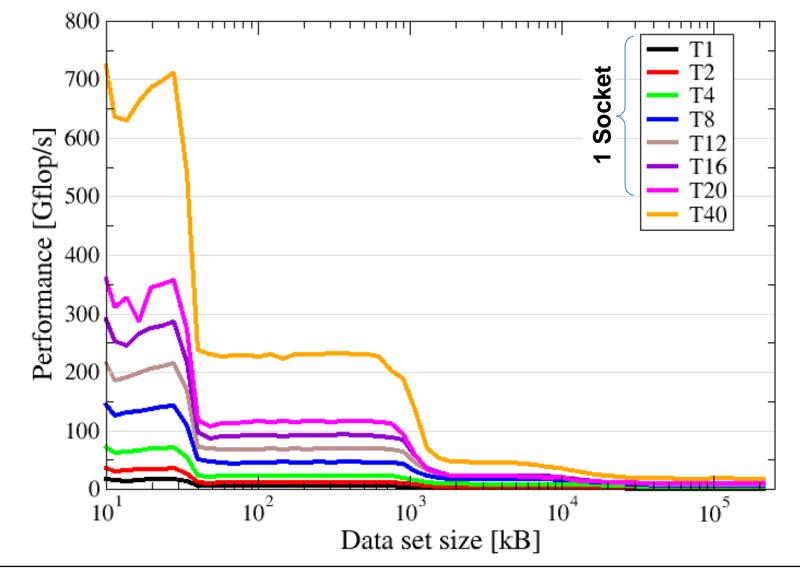

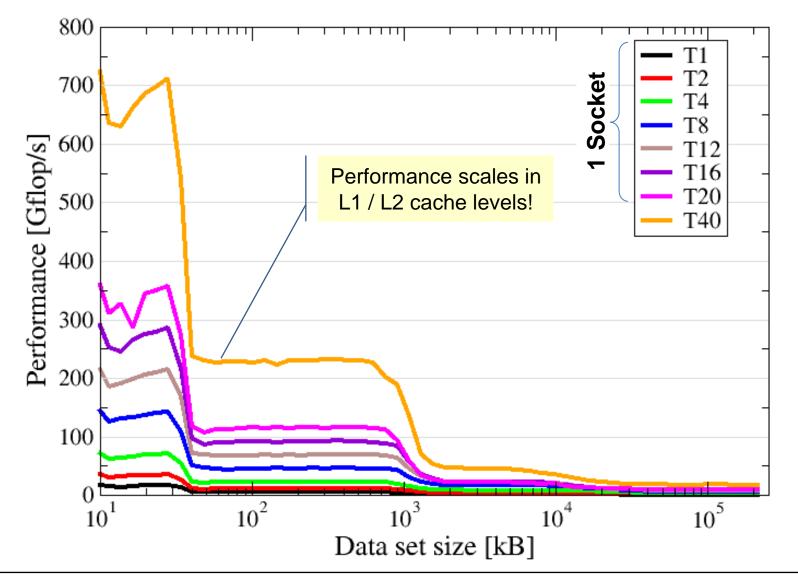

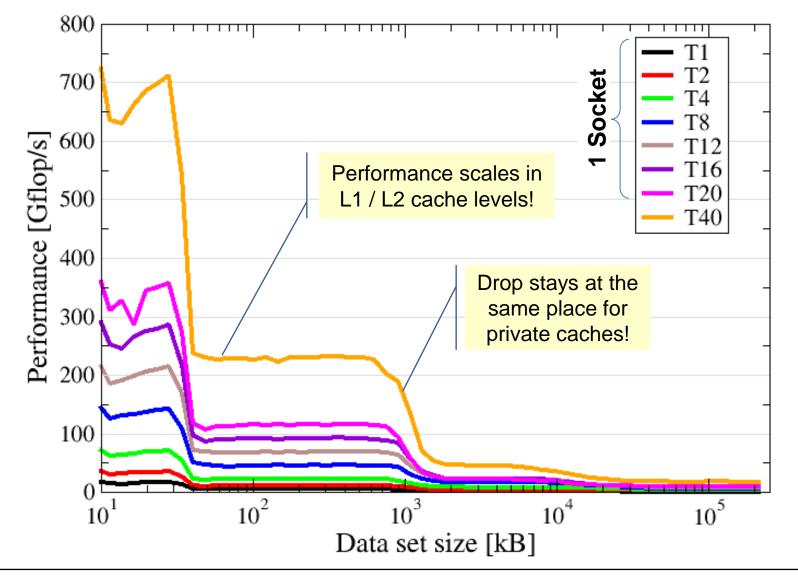

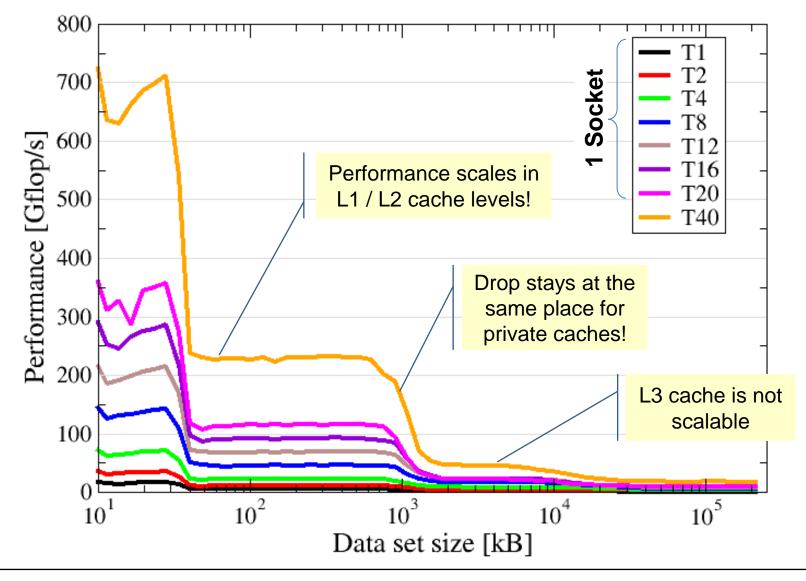

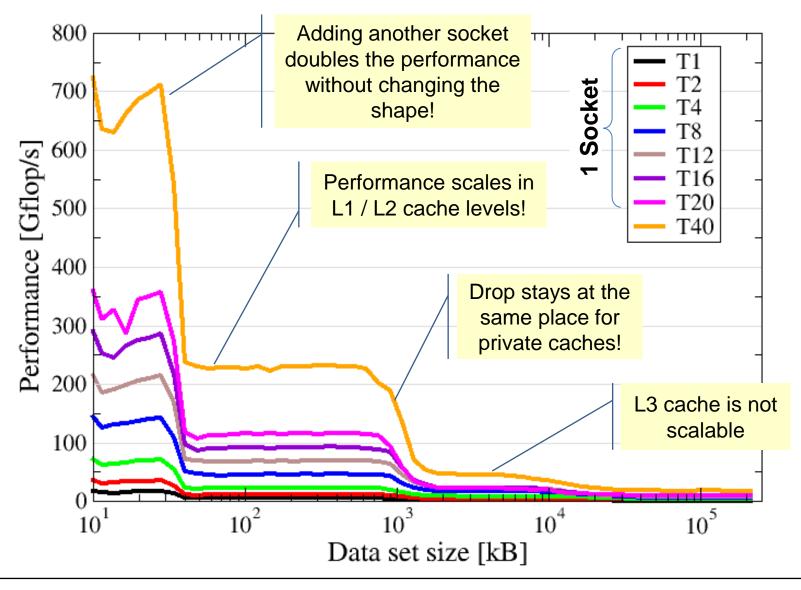

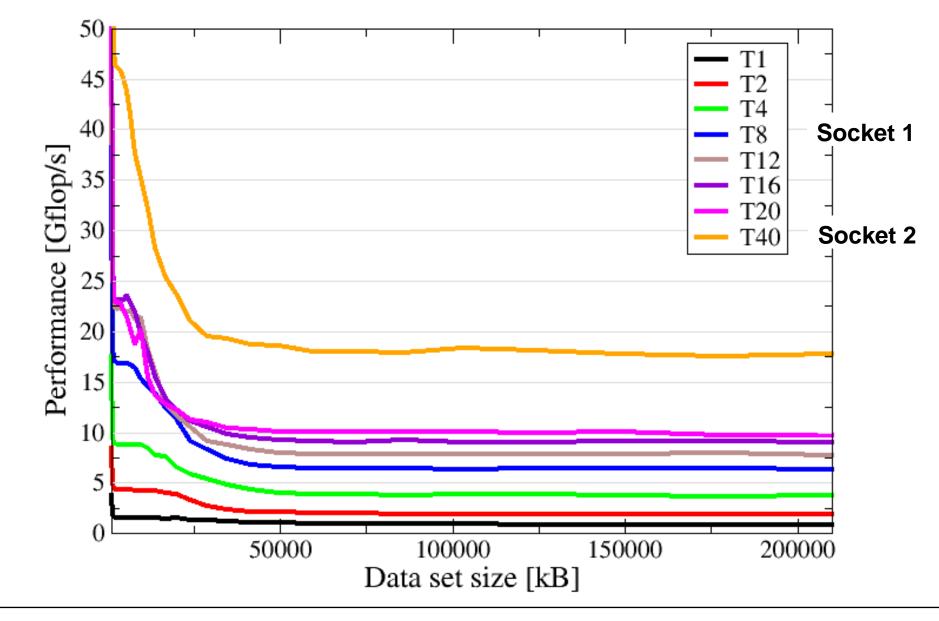

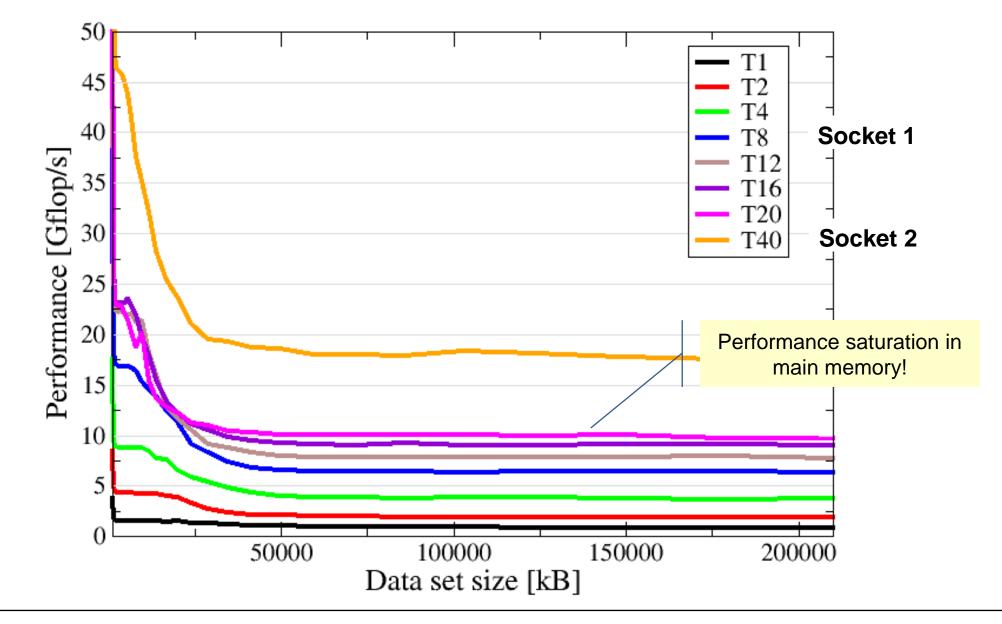

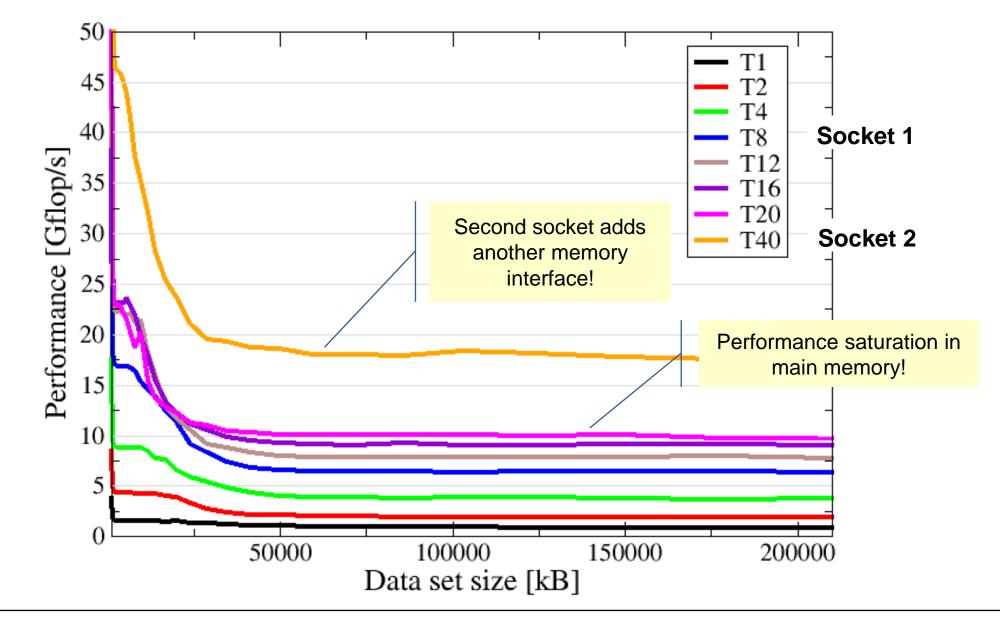

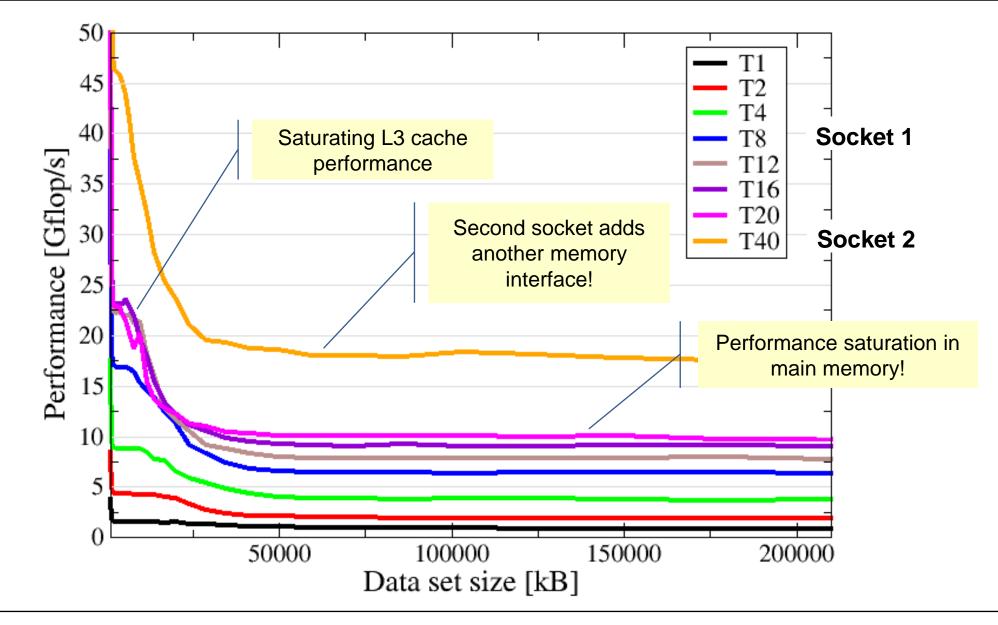

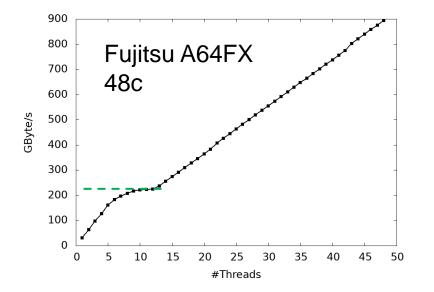

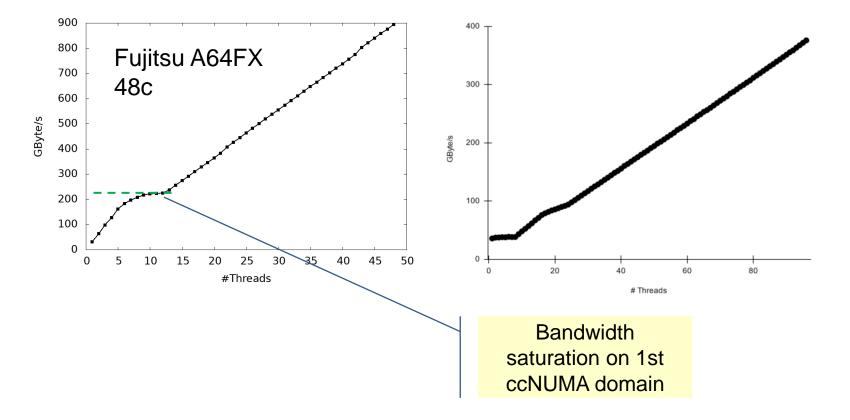

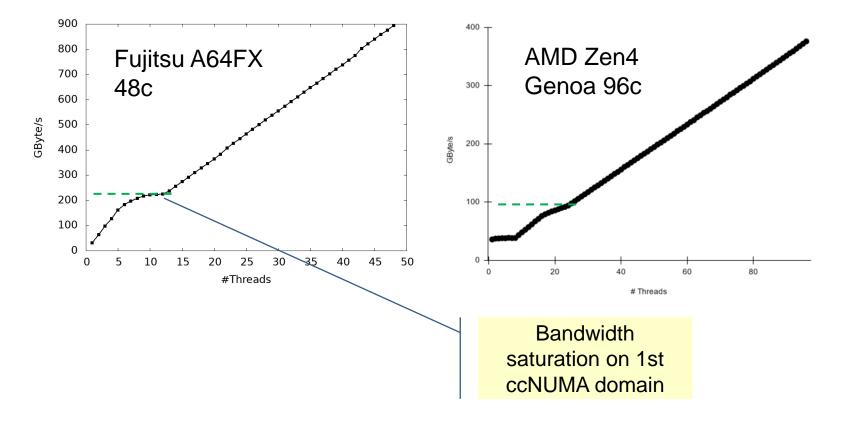

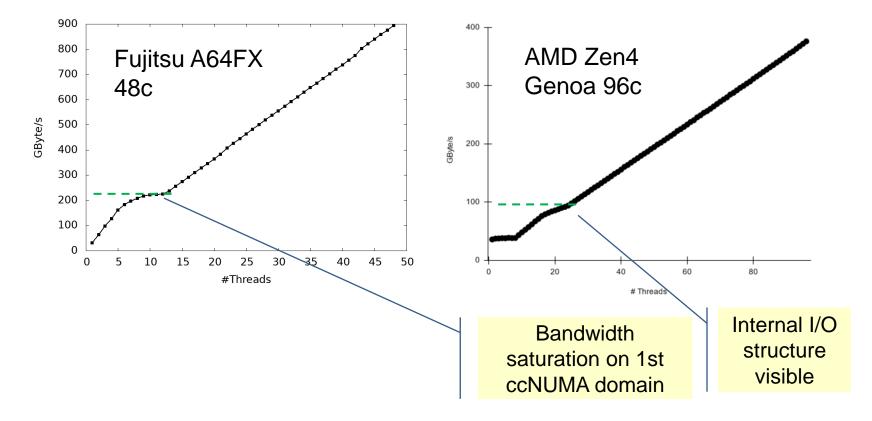

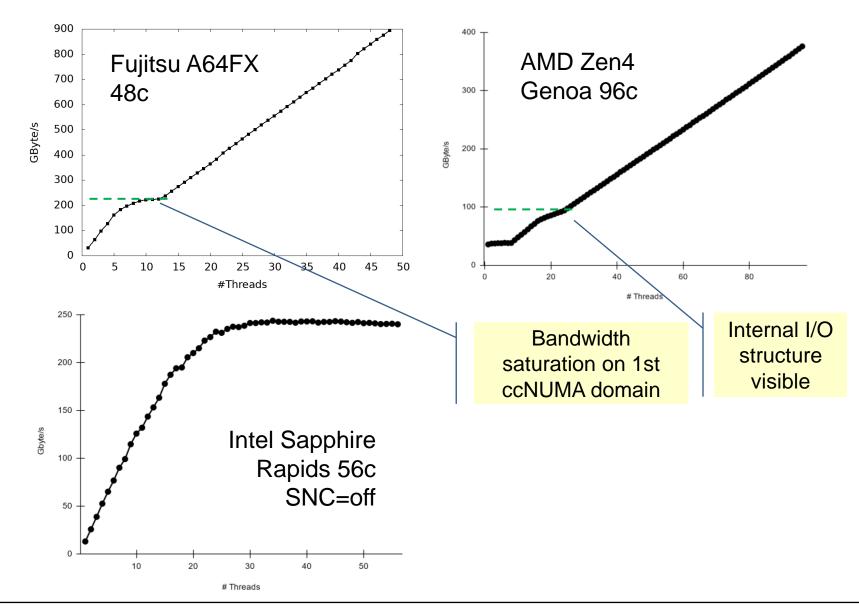

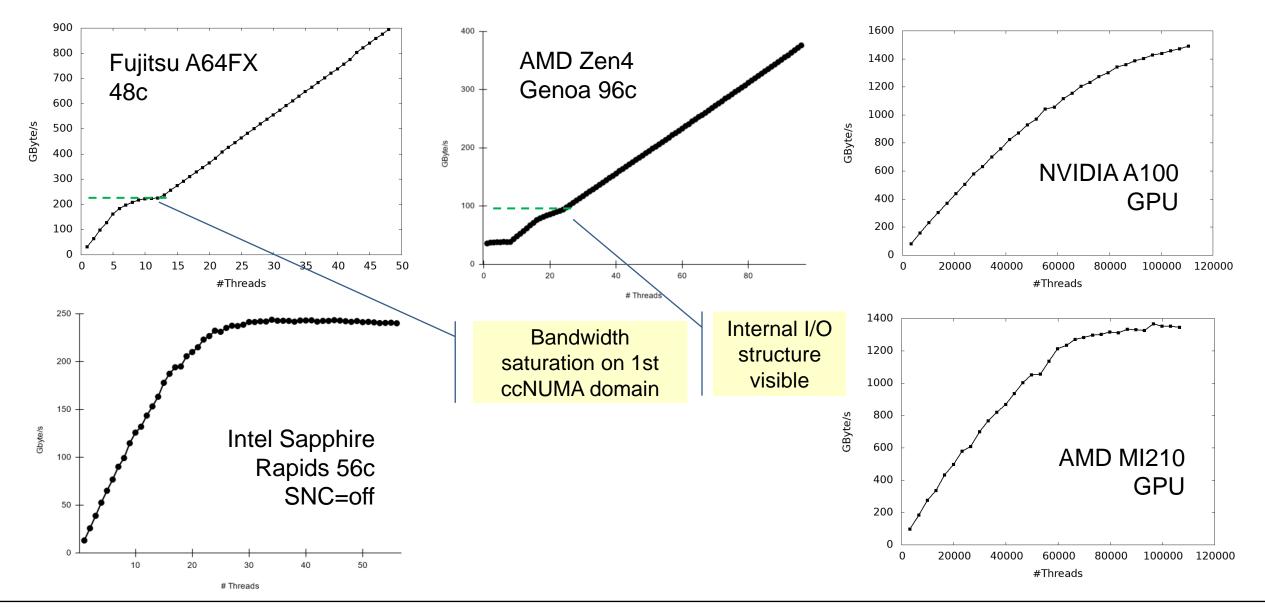

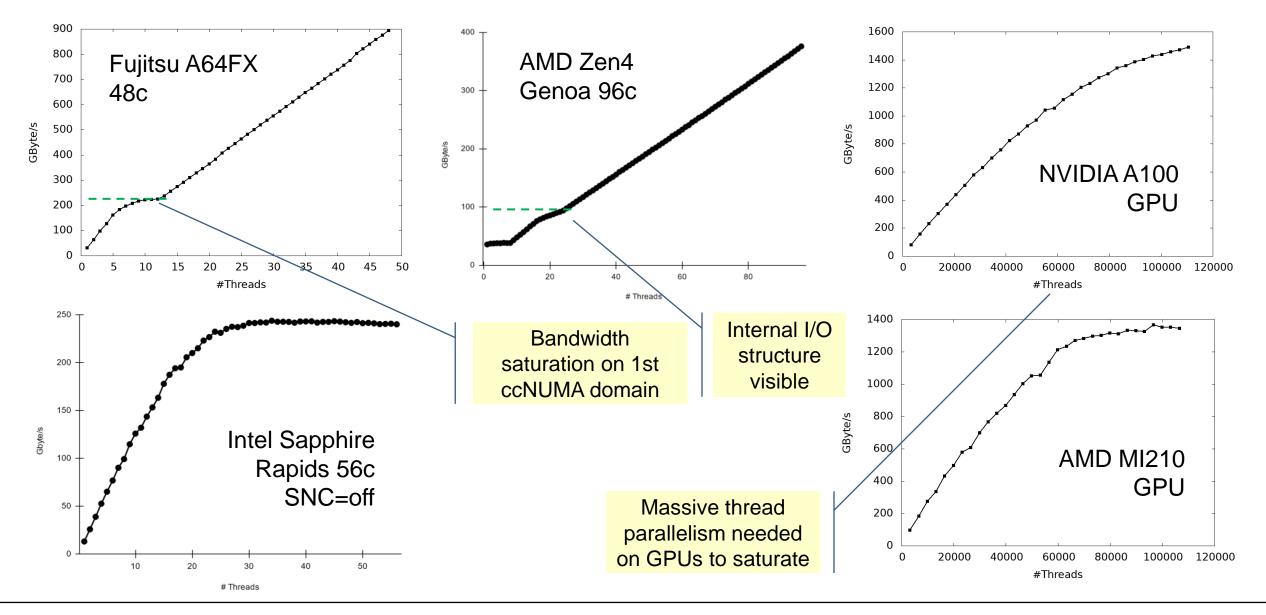

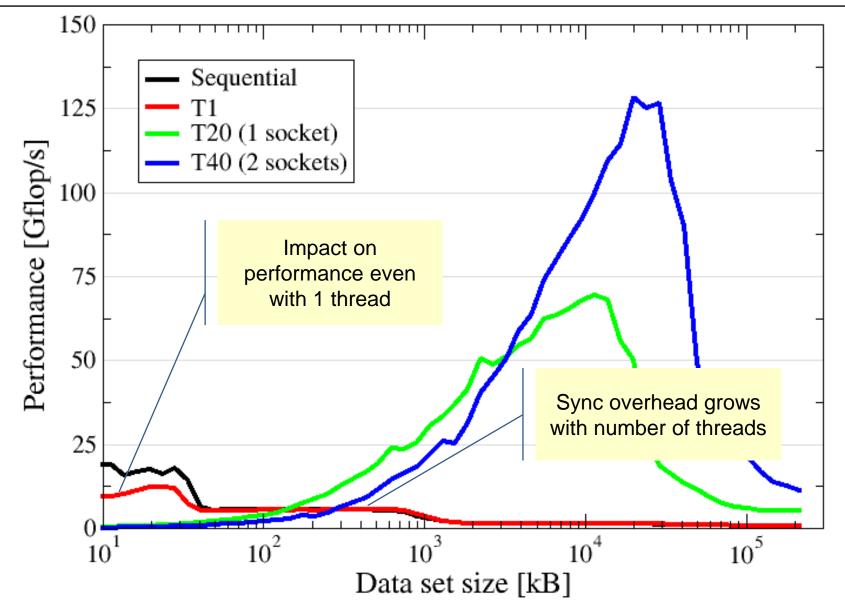

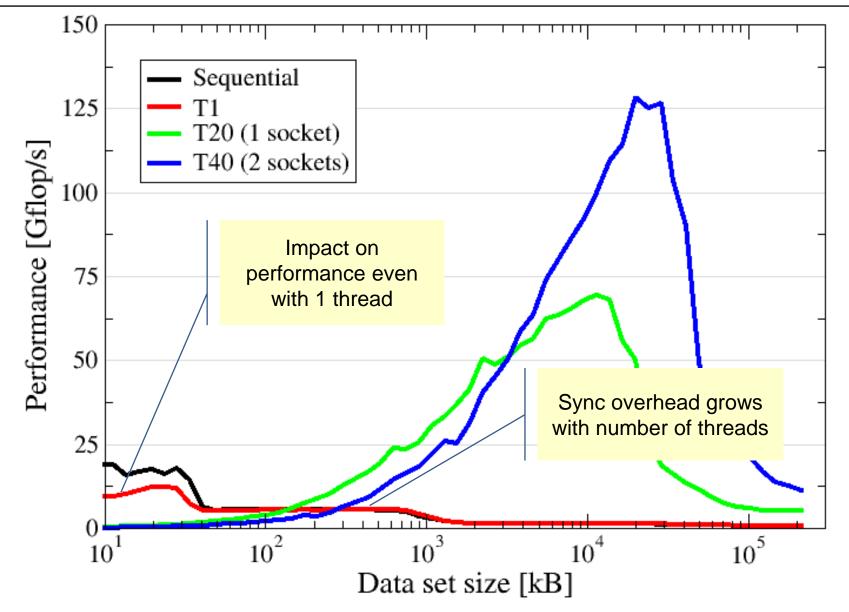

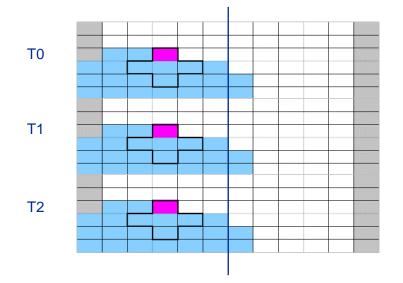

- How does the bandwidth scale across cores?

- Are there any bottlenecks?

- How large are the caches?

```

likwid-bench \

-t triad_avx512_fma

-W S0:$size:$threads:1:2

```

- Scan \$size and \$threads

- Pin threads in chunks of 1 with distance of 2 (skip SMT threads)

- How does the bandwidth scale across cores?

- Are there any bottlenecks?

- How large are the caches?

- Scan \$size and \$threads

- Pin threads in chunks of 1 with distance of 2 (skip SMT threads)

- How does the bandwidth scale across cores?

- Are there any bottlenecks?

- How large are the caches?

- Scan \$size and \$threads

- Pin threads in chunks of 1 with distance of 2 (skip SMT threads)

- How does the bandwidth scale across cores?

- Are there any bottlenecks?

- How large are the caches?

- Scan \$size and \$threads

- Pin threads in chunks of 1 with distance of 2 (skip SMT threads)

- How does the bandwidth scale across cores?

- Are there any bottlenecks?

- How large are the caches?

- Scan \$size and \$threads

- Pin threads in chunks of 1 with distance of 2 (skip SMT threads)

- How does the bandwidth scale across cores?

- Are there any bottlenecks?

- How large are the caches?

- Scan \$size and \$threads

- Pin threads in chunks of 1 with distance of 2 (skip SMT threads)

Node-Level Performance Engineering

Node-Level Performance Engineering

### Memory bandwidth saturation (read-only)

Node-Level Performance Engineering

### Memory bandwidth saturation (read-only)

Node-Level Performance Engineering

69

# The OpenMP-parallel vector triad benchmark

#### OpenMP worksharing in the benchmark loop

```

S = getTimeStamp();

#pragma omp parallel

ł

for(int j = 0; j < iter; j++) {</pre>

#pragma omp for

for (int i=0; i<N; i++) {</pre>

a[i] = b[i] + d[i] * c[i];

Implicit barrier

E = getTimeStamp();

```

Typical barrier cost

- ~ 10000 cy full node

- Scales with log(#cores)

- Depends on positions of threads (topology)

# Conclusions from the microbenchmarks

- Microbenchmarks can yield surprisingly deep insights

- Affinity matters!

- Almost all performance properties depend on the position of

- Data

- Threads/processes

- Consequences

- Know where your threads are running

- Know where your data is (see later for that)

- Bandwidth bottlenecks are ubiquitous

- Synchronization overhead may be an issue

- ... and depends on the system topology!

- Many-core poses new challenges in terms of synchronization

Friedrich-Alexander-Universität Erlangen-Nürnberg

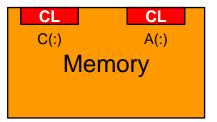

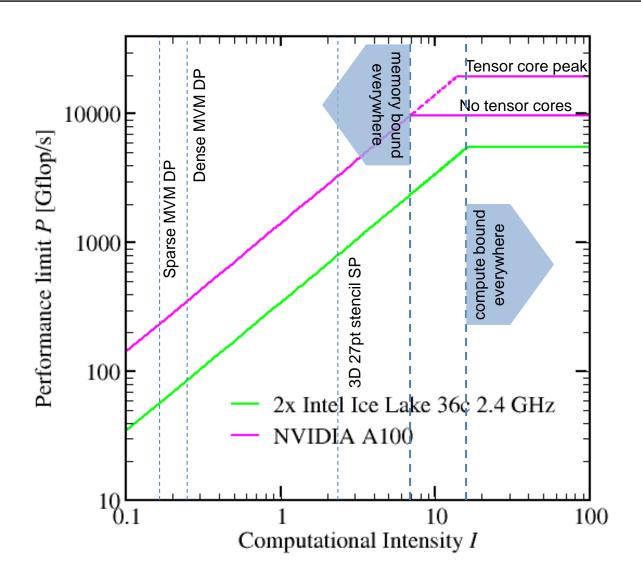

## "Simple" performance modeling: The Roofline Model

#### Loop-based performance modeling: Execution vs. data transfer

R.W. Hockney and I.J. Curington:  $f_{1/2}$ : A parameter to characterize memory and communication bottlenecks. Parallel Computing 10, 277-286 (1989). DOI: 10.1016/0167-8191(89)90100-2

W. Schönauer: <u>Scientific Supercomputing: Architecture and Use of Shared and Distributed Memory Parallel Computers</u>. Self-edition (2000)

S. Williams: <u>Auto-tuning Performance on Multicore Computers</u>. UCB Technical Report No. UCB/EECS-2008-164. PhD thesis (2008)

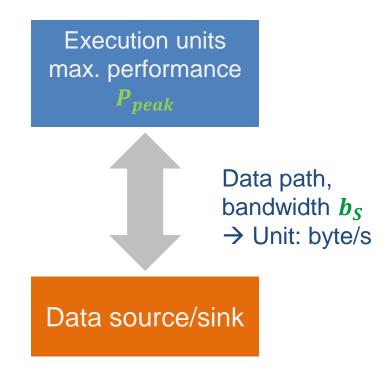

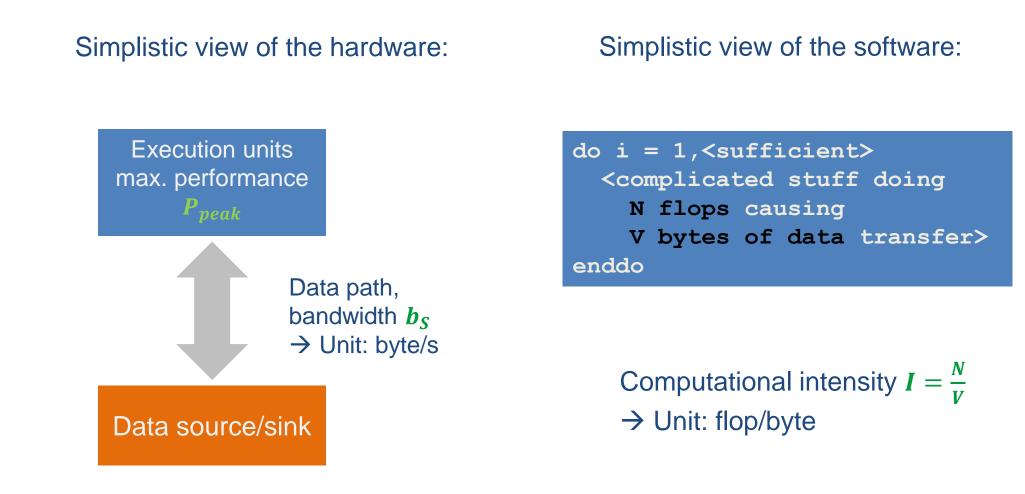

#### A simple performance model for loops

Simplistic view of the hardware:

#### A simple performance model for loops

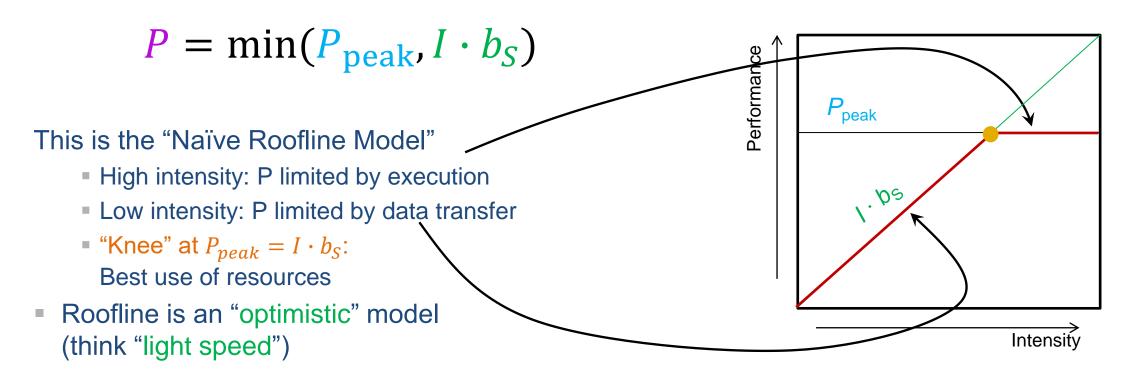

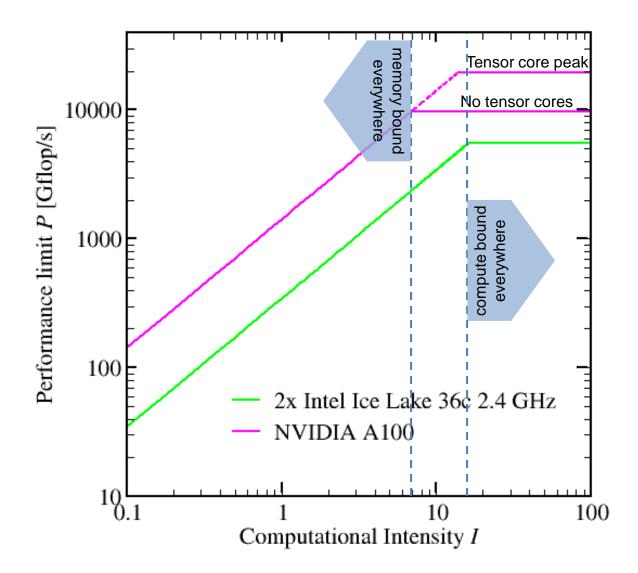

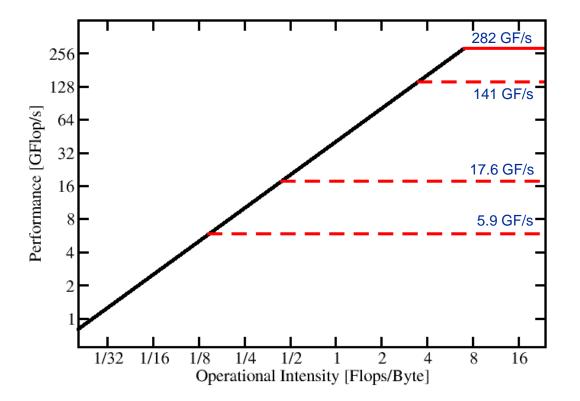

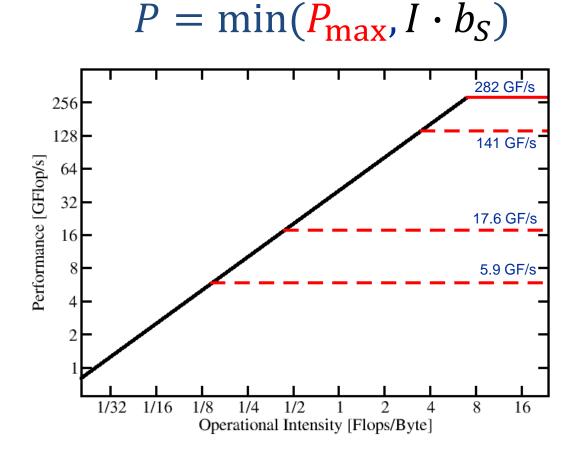

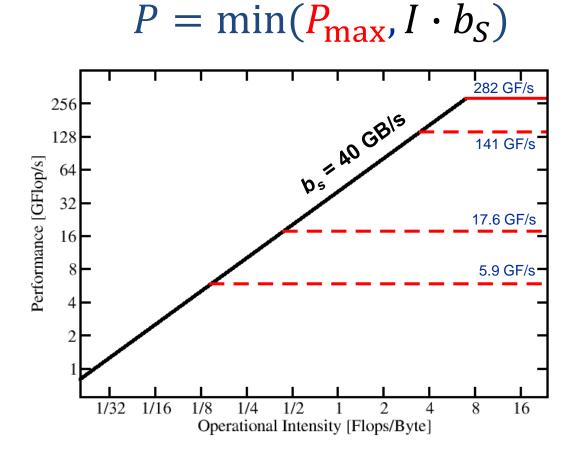

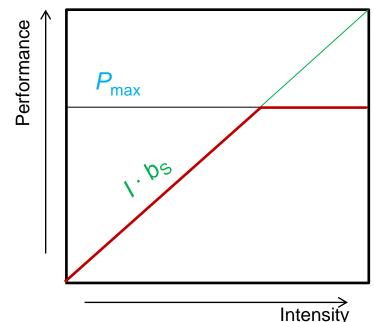

# Naïve Roofline Model

How fast can tasks be processed at most? P [flop/s]

#### The bottleneck is either

- The execution of work:

- The data path:

$P_{\text{peak}}$  [flop/s]  $I \cdot b_S$  [flop/byte x byte/s]

#### This is the "Naïve Roofline Model"

- High intensity: P limited by execution

- Low intensity: P limited by data transfer

- "Knee" at P<sub>peak</sub> = I · b<sub>S</sub>: Best use of resources

- Roofline is an "optimistic" model (think "light speed")

# Naïve Roofline Model

How fast can tasks be processed at most? P [flop/s]

#### The bottleneck is either

- The execution of work:

- The data path:

$P_{\text{peak}}$  [flop/s]  $I \cdot b_S$  [flop/byte x byte/s]

$P = \min(P_{\text{peak}}, I \cdot b_S)$

This is the "Naïve Roofline Model"

- High intensity: P limited by execution

- Low intensity: P limited by data transfer

- "Knee" at P<sub>peak</sub> = I · b<sub>S</sub>:

Best use of resources

- Roofline is an "optimistic" model (think "light speed")

# Naïve Roofline Model

How fast can tasks be processed at most? P [flop/s]

The bottleneck is either

- The execution of work:

- The data path:

$P_{\text{peak}}$  [flop/s]  $I \cdot b_S$  [flop/byte x byte/s]

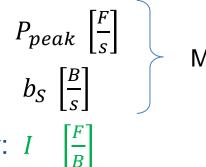

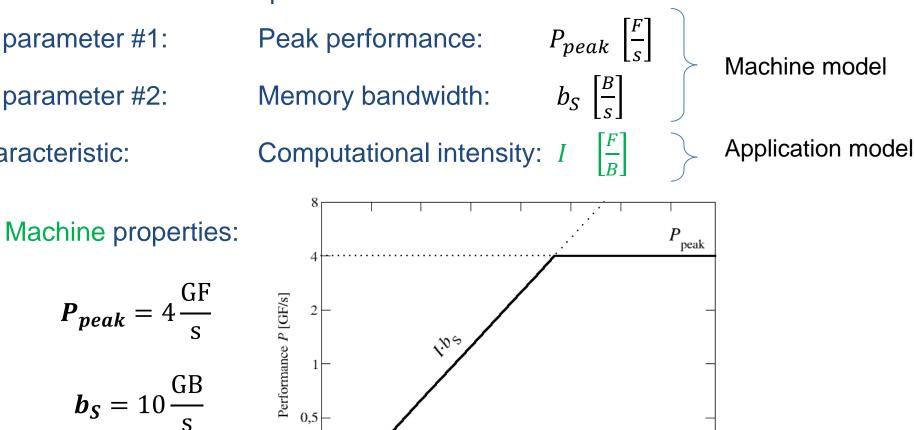

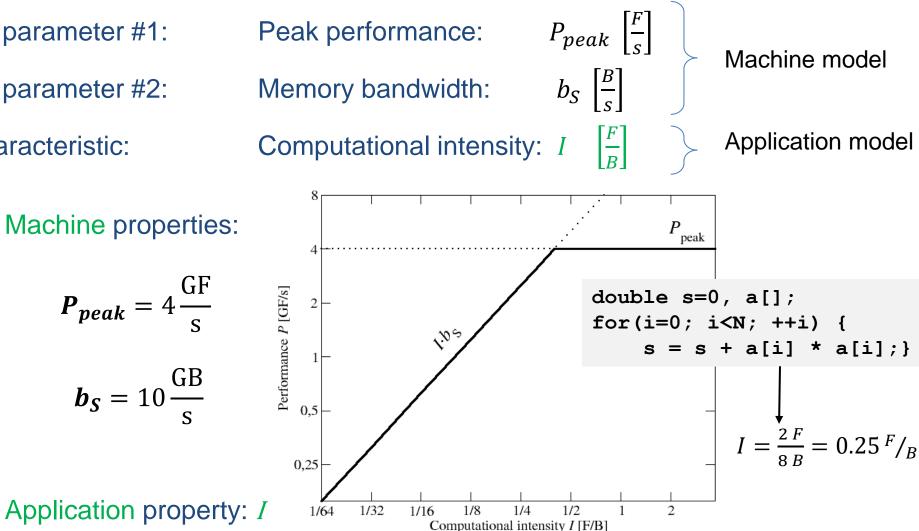

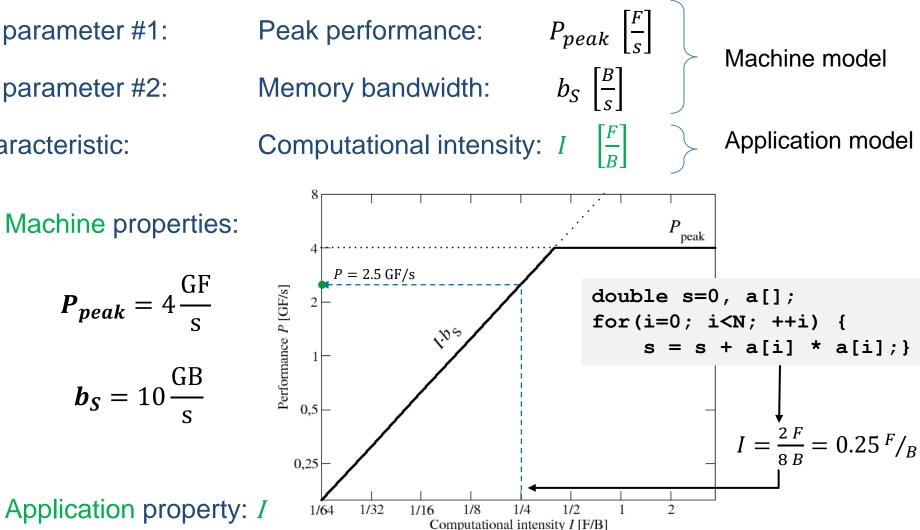

#### Apply the naive Roofline model in practice

- Machine parameter #1:

- Machine parameter #2:

- Code characteristic:

Peak performance: $P_{peak} \left[ \frac{F}{s} \right]$ Memory bandwidth: $b_S \left[ \frac{B}{s} \right]$

Computational intensity:  $I = \frac{F}{B}$

**SC23**

#### Apply the naive Roofline model in practice

- Machine parameter #1:

- Machine parameter #2:

- Code characteristic:

Peak performance: Memory bandwidth:

Computational intensity: I

Machine model

#### Apply the naive Roofline model in practice

- Machine parameter #1:

- Machine parameter #2:

- Code characteristic:

Peak performance: $P_{peak} \begin{bmatrix} F \\ s \end{bmatrix}$ MachMemory bandwidth: $b_S \begin{bmatrix} B \\ s \end{bmatrix}$ MachComputational intensity: $I \begin{bmatrix} F \\ B \end{bmatrix}$ Applie

Machine model

Application model

#### Apply the naive Roofline model in practice

- Machine parameter #1:

- Machine parameter #2:

- Code characteristic:

0,25

1/64

1/32

1/16

#### Apply the naive Roofline model in practice

- Machine parameter #1:

- Machine parameter #2:

- Code characteristic:

1/2

2

1/4

Computational intensity I [F/B]

1/8

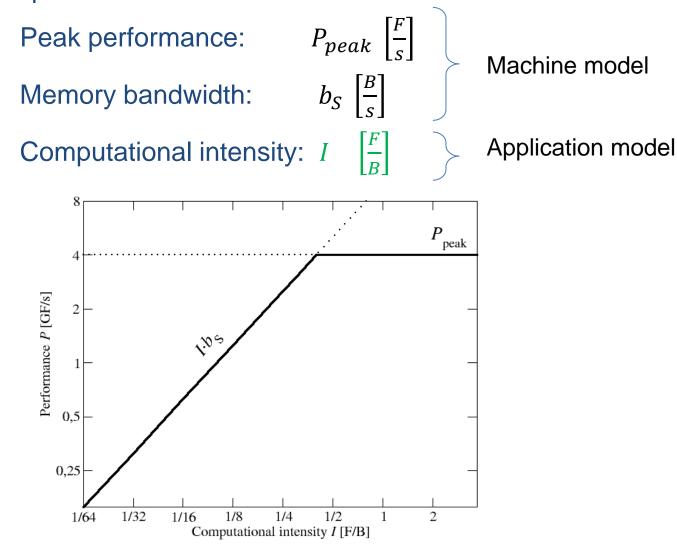

#### Apply the naive Roofline model in practice

- Machine parameter #1:

- Machine parameter #2:

- Code characteristic:

Peak performance: $P_{peak} \begin{bmatrix} F\\ s \end{bmatrix}$ Machine modelMemory bandwidth: $b_S \begin{bmatrix} B\\ s \end{bmatrix}$ Application modelComputational intensity: $I \begin{bmatrix} F\\ B \end{bmatrix}$ Application modelties: $a_{4}$  $P_{peak}$

Machine properties:  $P_{peak} = 4 \frac{\text{GF}}{\text{S}}$ Performance P [GF/s] 1<sup>30 55</sup>  $\boldsymbol{b}_{\boldsymbol{S}} = 10 \frac{\text{GB}}{\text{GB}}$ 0,5 0,25 Application property: I 1/8 1/21/64 1/32 1/16 1/42 Computational intensity I [F/B]

#### Apply the naive Roofline model in practice

- Machine parameter #1:

- Machine parameter #2:

- Code characteristic:

#### Apply the naive Roofline model in practice

- Machine parameter #1:

- Machine parameter #2:

- Code characteristic:

# Prerequisites for the Roofline Model

- Data transfer and core execution overlap perfectly!

- Either the limit is core execution or it is data transfer

- Slowest limiting factor "wins"; all others are assumed to have no impact

- If two bottlenecks are "close," no interaction is assumed

- Data access latency is ignored, i.e. perfect streaming mode

Achievable bandwidth is the limit

- Chip must be able to saturate the bandwidth bottleneck(s)

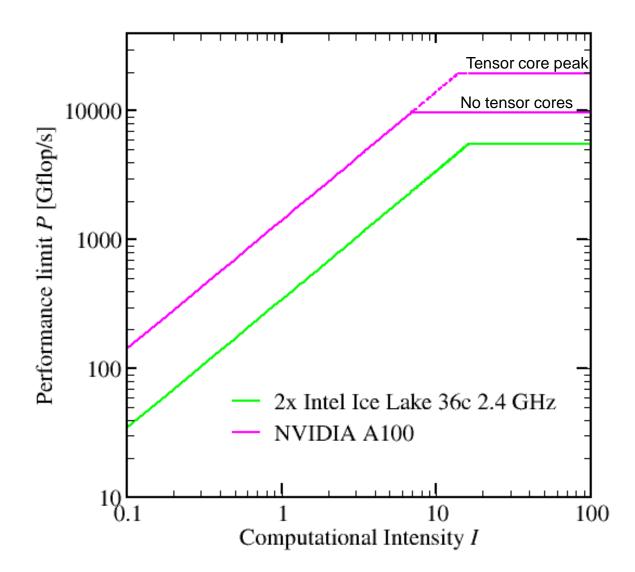

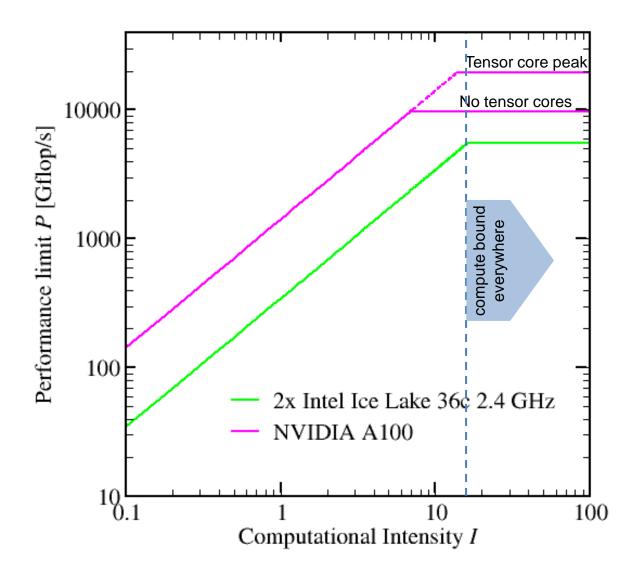

Always model the full chip

- Compare capabilities of different machines

- Compare performance expectations for different loops

- Compare capabilities of different machines

- Compare performance expectations for different loops

- Compare capabilities of different machines

- Compare performance expectations for different loops

- Compare capabilities of different machines

- Compare performance expectations for different loops

- Compare capabilities of different machines

- Compare performance expectations for different loops

- Compare capabilities of different machines

- Compare performance expectations for different loops

- Compare capabilities of different machines

- Compare performance expectations for different loops

- Roofline always provides upper bound but is it realistic?

- Simple case: Loop kernel has loop-carried dependecncies → cannot achieve peak

- Other bandwidth bottlenecks may apply

P<sub>max</sub> = Applicable peak performance of a loop, assuming that data comes from the level 1 cache (this is not necessarily P<sub>peak</sub>)

→ e.g., P<sub>max</sub> = 176 GFlop/s

- P<sub>max</sub> = Applicable peak performance of a loop, assuming that data comes from the level 1 cache (this is not necessarily P<sub>peak</sub>)

→ e.g., P<sub>max</sub> = 176 GFlop/s

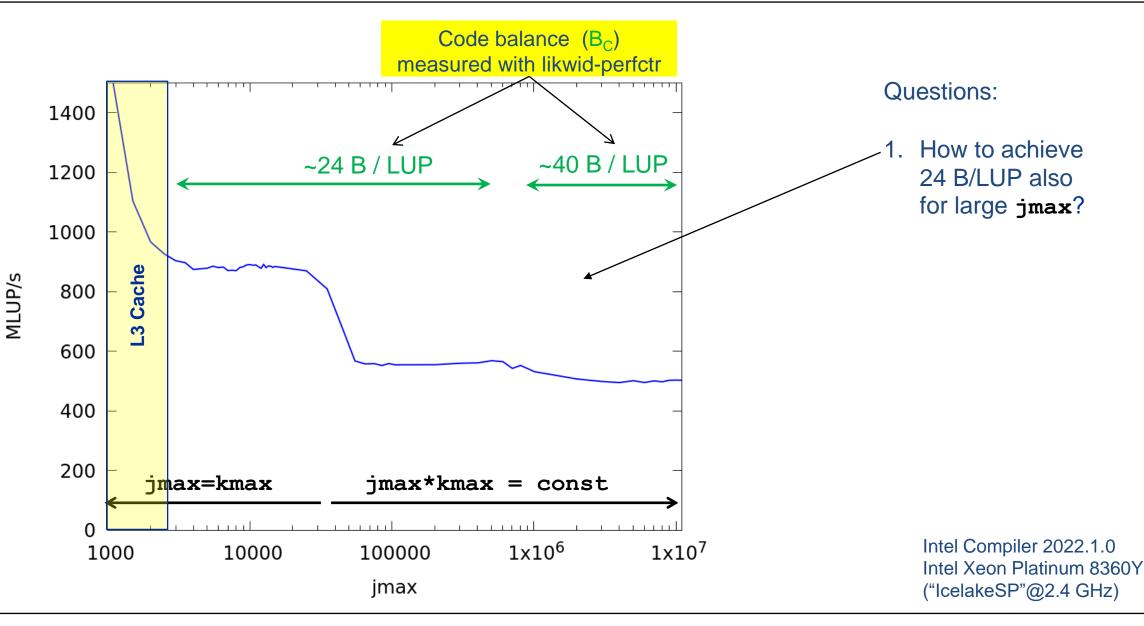

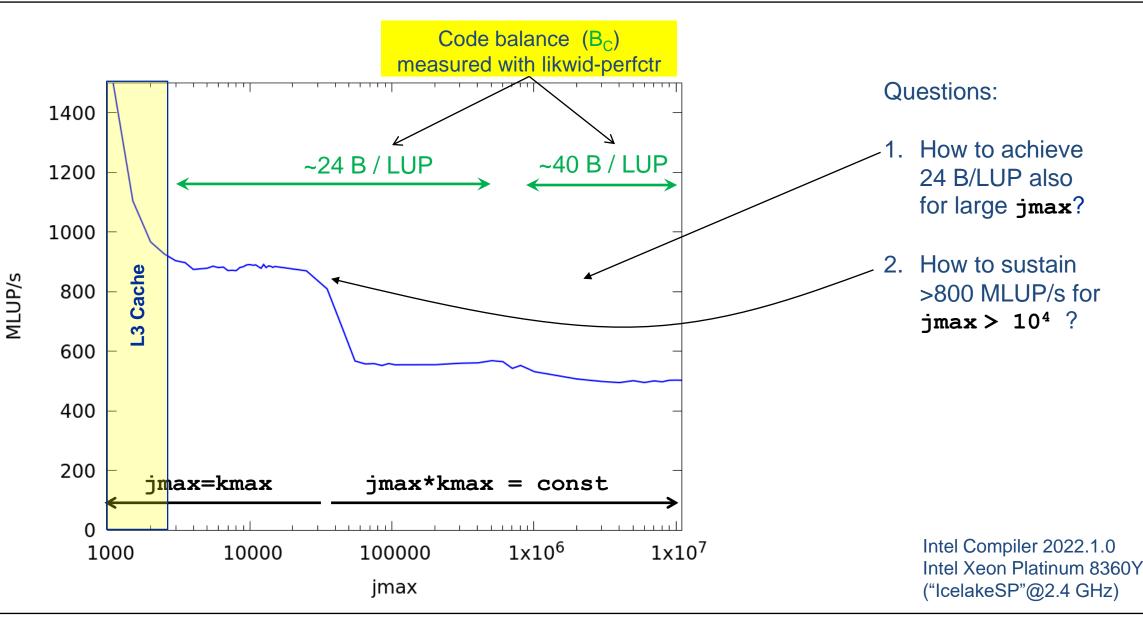

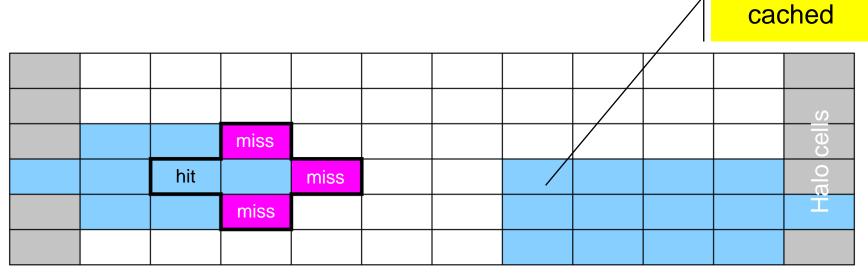

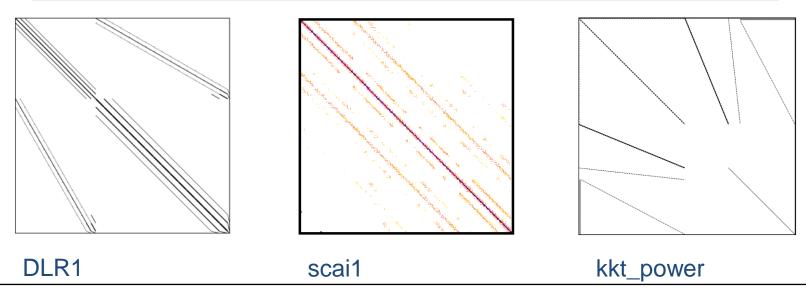

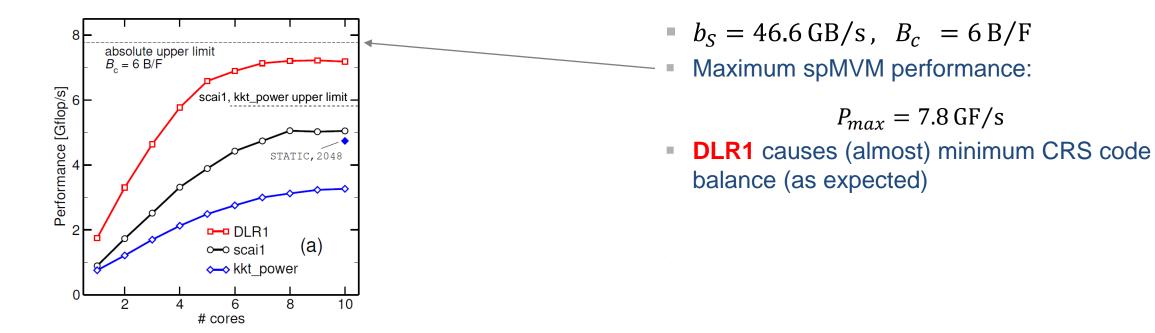

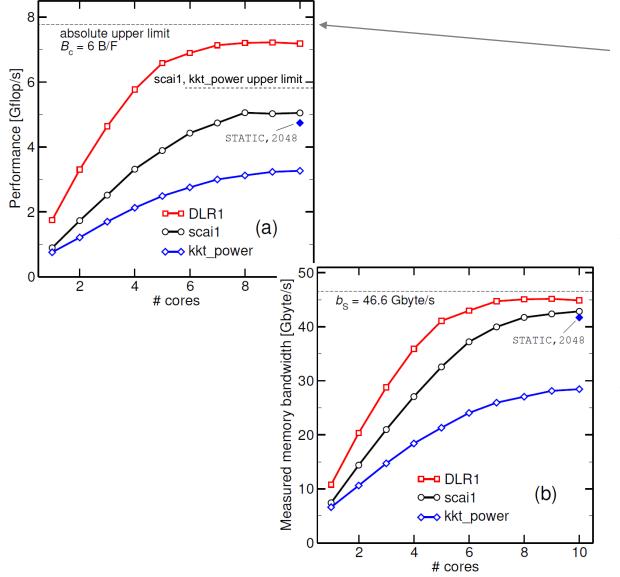

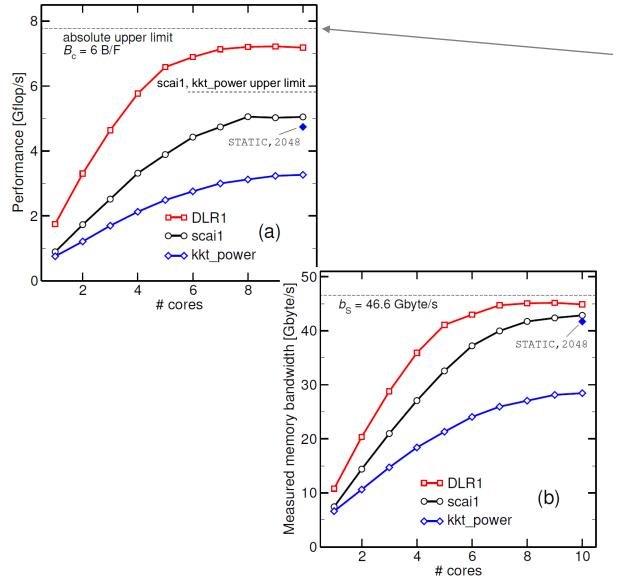

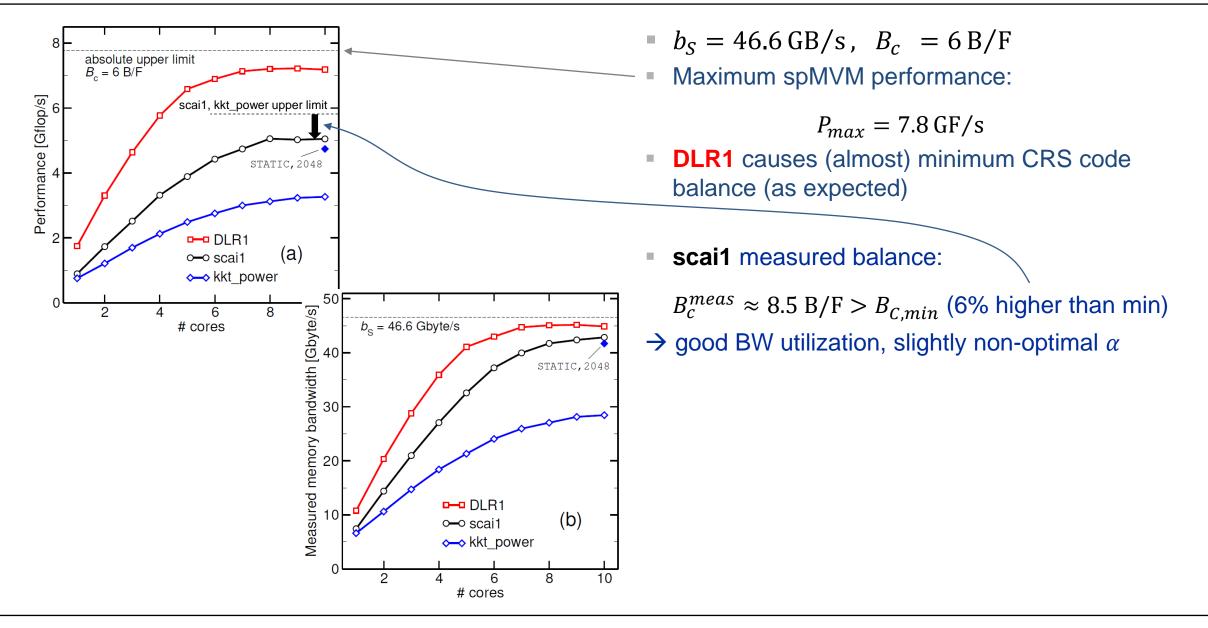

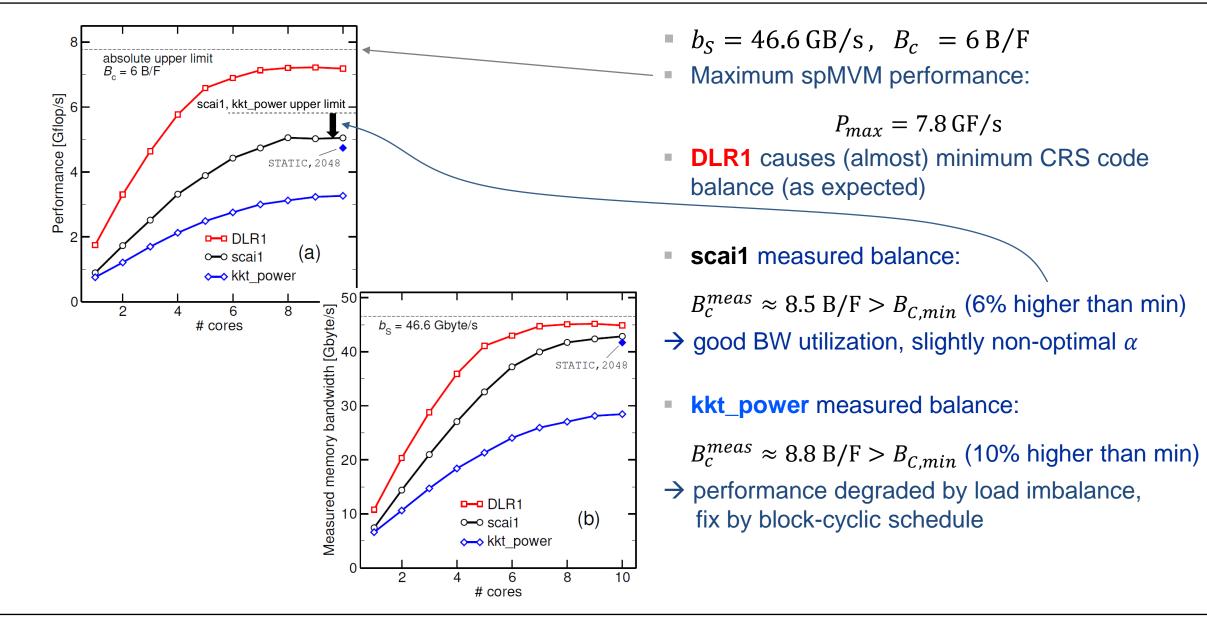

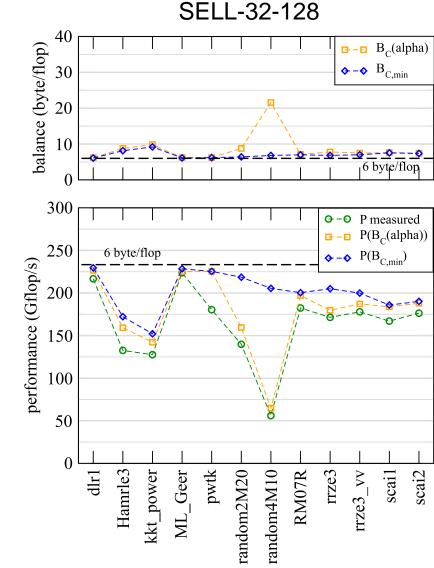

- 2. *I* = Computational intensity ("work" per byte transferred) over the slowest data path utilized (code balance  $B_C = I^{-1}$ ) → e.g., *I* = 0.167 Flop/Byte →  $B_C = 6$  Byte/Flop

- P<sub>max</sub> = Applicable peak performance of a loop, assuming that data comes from the level 1 cache (this is not necessarily P<sub>peak</sub>)

→ e.g., P<sub>max</sub> = 176 GFlop/s

- 2. *I* = Computational intensity ("work" per byte transferred) over the slowest data path utilized (code balance  $B_C = I^{-1}$ ) → e.g., *I* = 0.167 Flop/Byte →  $B_C = 6$  Byte/Flop

- 1.  $P_{\text{max}}$  = Applicable peak performance of a loop, assuming that data comes from the level 1 cache (this is not necessarily  $P_{\text{peak}}$ )  $\rightarrow$  e.g.,  $P_{\text{max}}$  = 176 GFlop/s

- 2. *I* = Computational intensity ("work" per byte transferred) over the slowest data path utilized (code balance  $B_C = I^{-1}$ ) → e.g., *I* = 0.167 Flop/Byte →  $B_C = 6$  Byte/Flop

- 3.  $b_{\rm S}$  = Applicable (saturated) peak bandwidth of the slowest data path utilized  $\rightarrow$  e.g.,  $b_{\rm S}$  = 56 GByte/s

- 1.  $P_{\text{max}}$  = Applicable peak performance of a loop, assuming that data comes from the level 1 cache (this is not necessarily  $P_{\text{peak}}$ )  $\rightarrow$  e.g.,  $P_{\text{max}}$  = 176 GFlop/s

- 2. *I* = Computational intensity ("work" per byte transferred) over the slowest data path utilized (code balance  $B_C = I^{-1}$ ) → e.g., *I* = 0.167 Flop/Byte →  $B_C = 6$  Byte/Flop

- 3.  $b_s$  = Applicable (saturated) peak bandwidth of the slowest data path utilized  $\rightarrow$  e.g.,  $b_s$  = 56 GByte/s

Performance limit:

$$P = \min(P_{\max}, I \cdot b_S) = \min\left(P_{\max}, \frac{b_S}{B_C}\right)$$

[Byte/Flop]

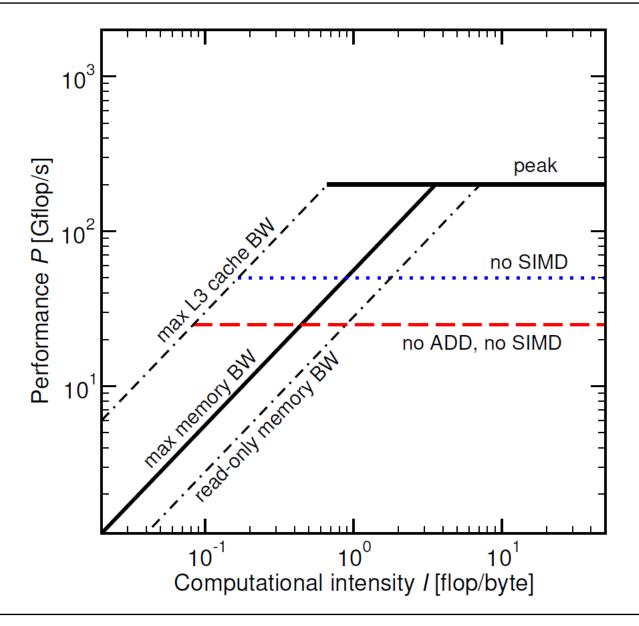

## A refined Roofline Model

- 1.  $P_{\text{max}}$  = Applicable peak performance of a loop, assuming that data comes from the level 1 cache (this is not necessarily  $P_{\text{peak}}$ )  $\rightarrow$  e.g.,  $P_{\text{max}}$  = 176 GFlop/s

- 2. *I* = Computational intensity ("work" per byte transferred) over the slowest data path utilized (code balance  $B_C = I^{-1}$ ) → e.g., *I* = 0.167 Flop/Byte →  $B_C = 6$  Byte/Flop

- 3.  $b_{\rm S}$  = Applicable (saturated) peak bandwidth of the slowest data path utilized  $\rightarrow$  e.g.,  $b_{\rm S}$  = 56 GByte/s

Performance limit:

$$P = \min(P_{\max}, I \cdot b_S) = \min\left(P_{\max}, \frac{b_S}{B_C}\right)$$

[Byte/Flop]

R.W. Hockney and I.J. Curington:  $f_{1/2}$ : A parameter to characterize memory and communication bottlenecks.

Parallel Computing 10, 277-286 (1989). DOI: 10.1016/0167-8191(89)90100-2

W. Schönauer: Scientific Supercomputing: Architecture and Use of Shared and Distributed Memory Parallel Computers. Self-edition (2000)

S. Williams: Auto-tuning Performance on Multicore Computers. UCB Technical Report No. UCB/EECS-2008-164. PhD thesis (2008)

Node-Level Performance Engineering

Flop" is not the only

useful unit of work!

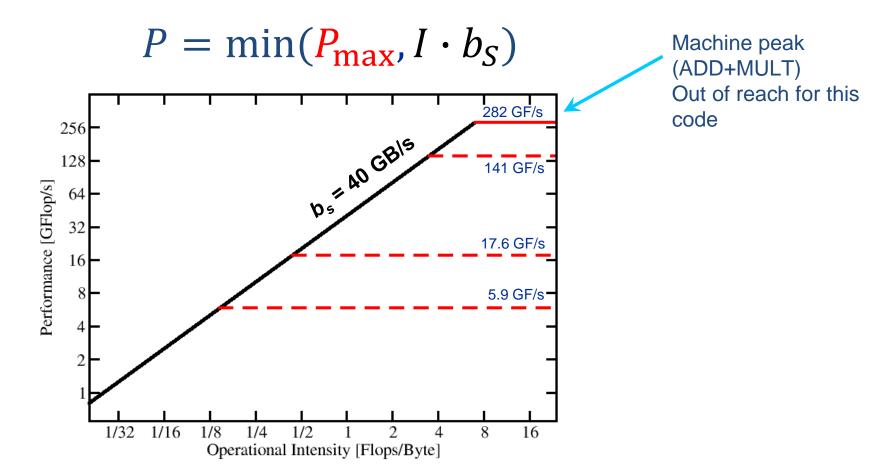

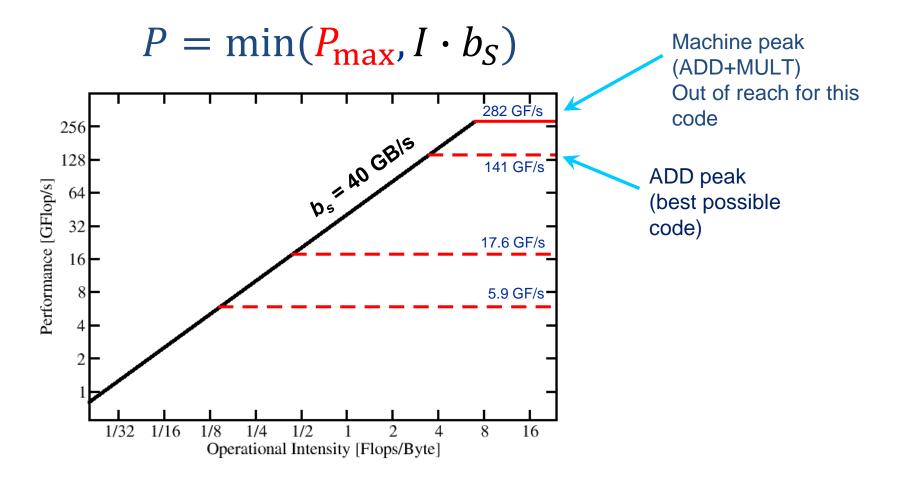

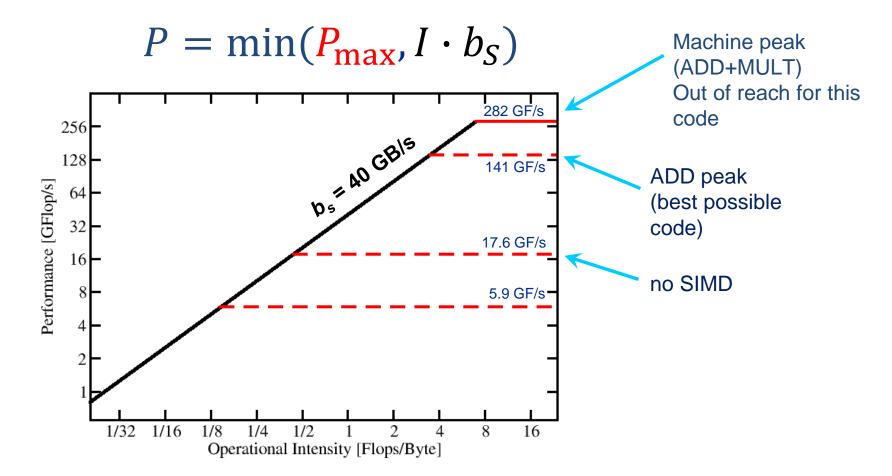

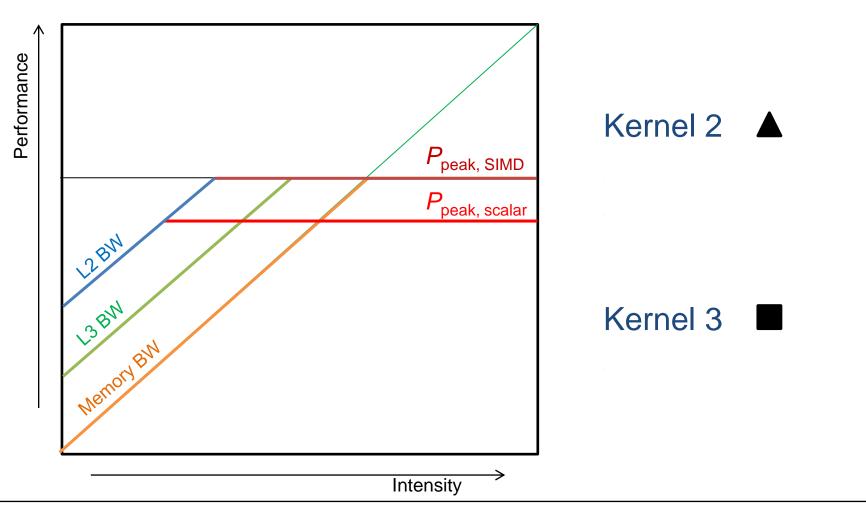

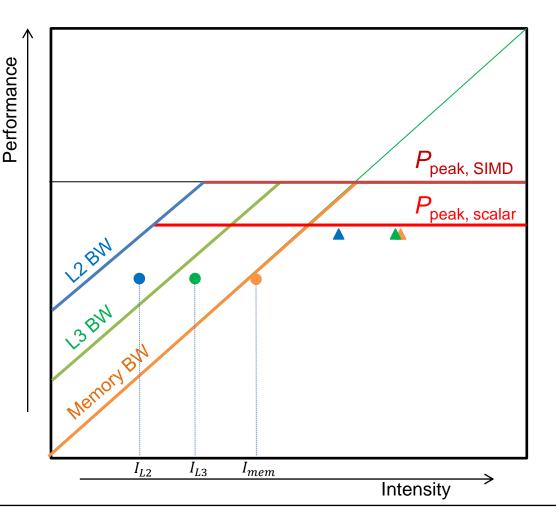

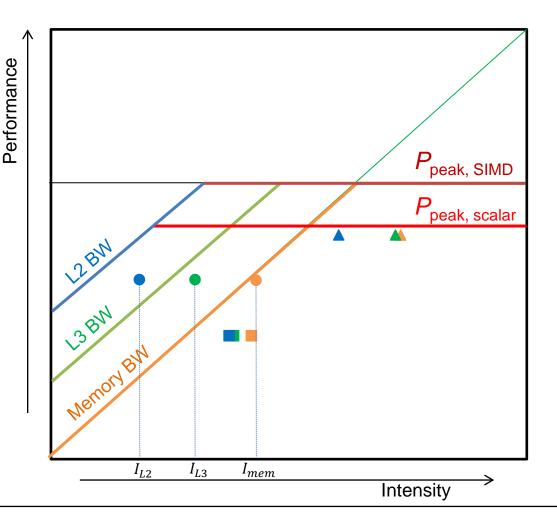

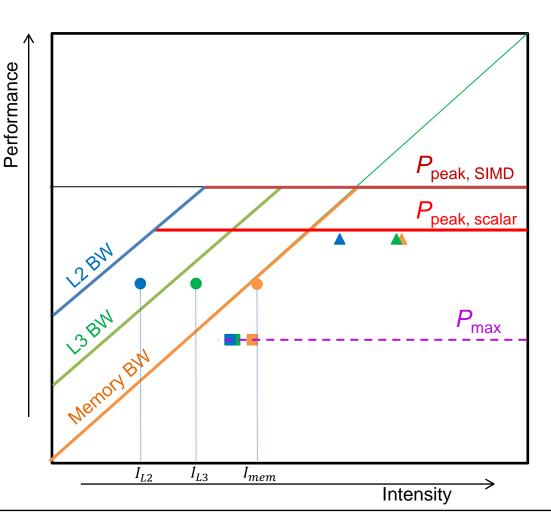

## Refined Roofline models: graphical representation

### Multiple ceilings may apply

- Different bandwidths / data paths

→ different inclined ceilings

- Different P<sub>max</sub>

→ different flat ceilings

In fact,  $P_{max}$  should always come from code analysis; generic ceilings are usually impossible to attain

## Hardware features of (some) Intel Xeon processors

| Microarchitecture       | Ivy Bridge EP             | Broadwell EP              | Cascade Lake SP                    | Ice Lake SP                      |

|-------------------------|---------------------------|---------------------------|------------------------------------|----------------------------------|

| Introduced              | 09/2013                   | 03/2016                   | 04/2019                            | 06/2021                          |

| Cores                   | ≤ 12                      | ≤ 22                      | ≤ 28                               | ≤ 40                             |

| LD/ST throughput per cy | /:                        |                           |                                    |                                  |

| AVX(2), AVX512          | 1 LD + ½ ST               | 2 LD + 1 ST               | 2 LD + 1 ST                        | 2 LD + 1 ST                      |

| SSE/scalar              | 2 LD    1 LD & 1 ST       | 2 LD + 1 31               | 2 LD + 1 31                        | 2 LD + 1 31                      |

| ADD throughput          | 1 / cy                    | 1 / cy                    | 2 / cy                             | 2 / cy                           |

| MUL throughput          | 1 / cy                    | 2 / cy                    | 2 / cy                             | 2 / cy                           |

| FMA throughput          | N/A                       | 2 / cy                    | 2 / cy                             | 2 / cy                           |

| L1-L2 data bus          | 32 B/cy                   | 64 B/cy                   | 64 B/cy                            | 64 B/cy                          |

| L2-L3 data bus          | 32 B/cy                   | 32 B/cy                   | 16+16 B/cy                         | 16+16 B/cy                       |

| L1/L2 per core          | 32 KiB / 256 KiB          | 32 KiB / 256 KiB          | 32 KiB / 1 MiB                     | 48 KiB / 1.25 MiB                |

| LLC                     | 2.5 MiB/core<br>inclusive | 2.5 MiB/core<br>inclusive | 1.375 MiB/core<br>exclusive/victim | 1.5 MiB/core<br>exclusive/victim |

| Memory                  | 4ch DDR3                  | 4ch DDR3                  | 6ch DDR4                           | 8ch DDR4                         |

| Memory BW (meas.)       | ~ 48 GB/s                 | ~ 62 GB/s                 | ~ 115 GB/s                         | ~ 160 GB/s                       |

<u>manual.html</u>

ntel-64-and-ia-32-architectures-optimization-reference-

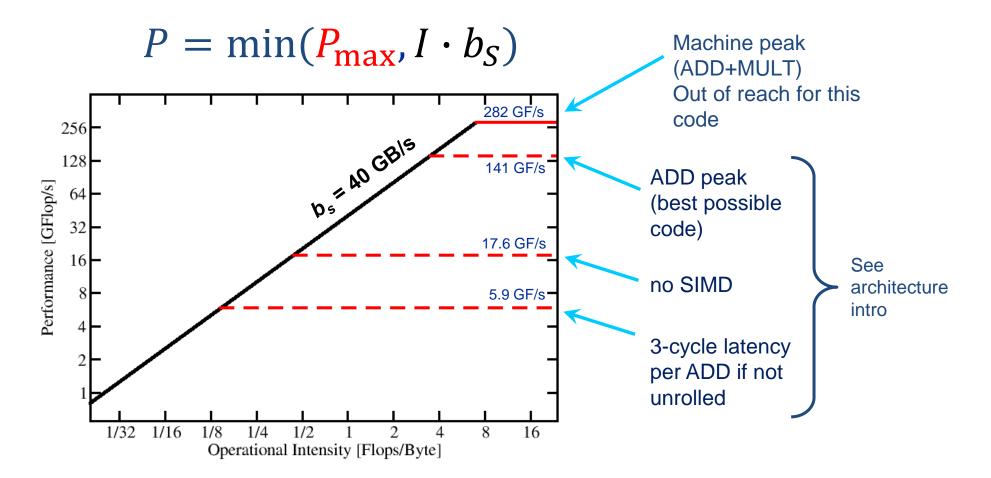

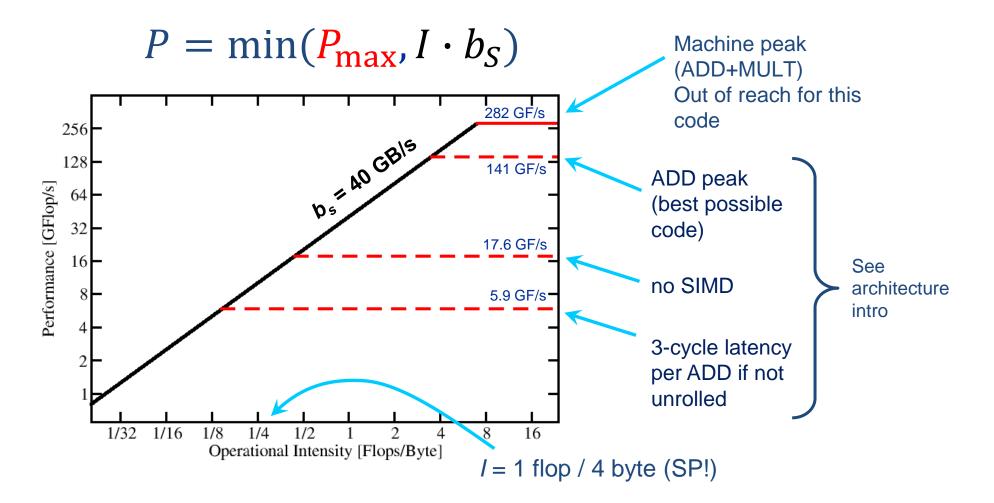

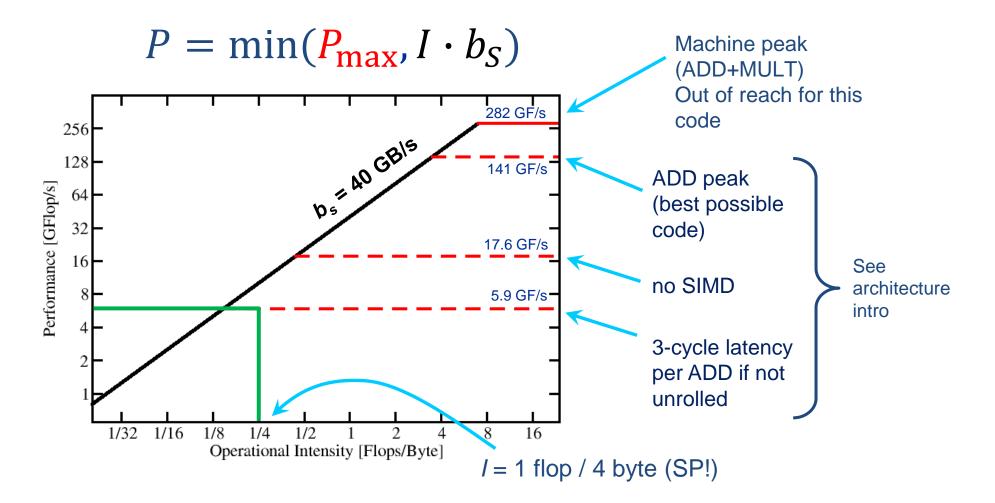

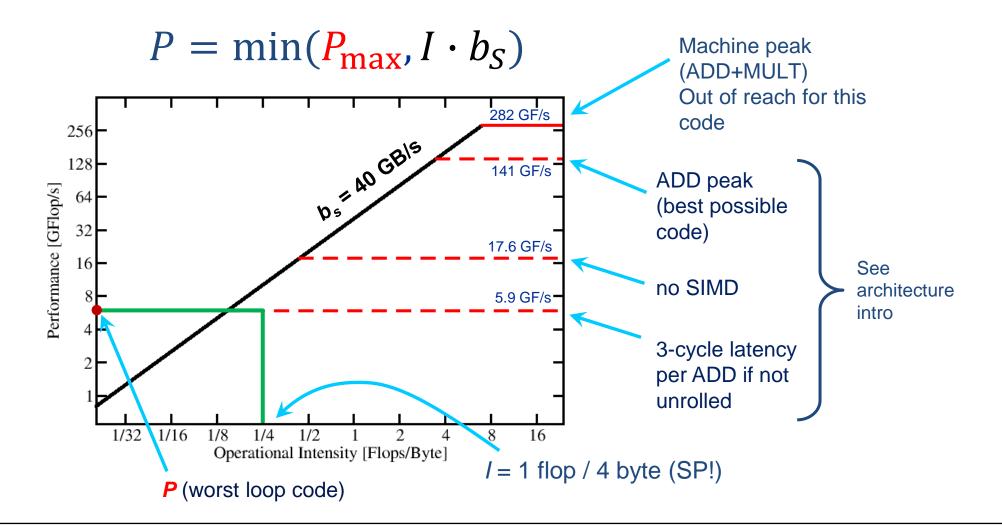

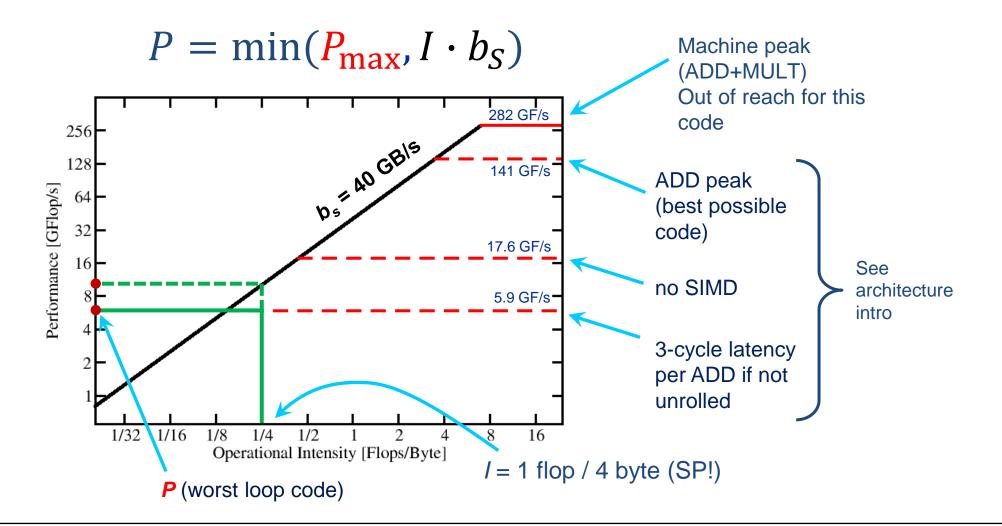

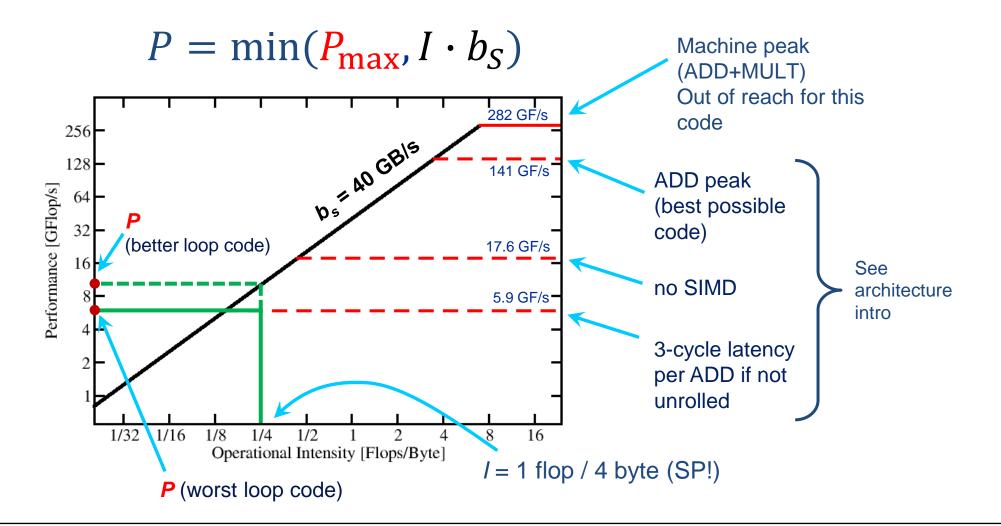

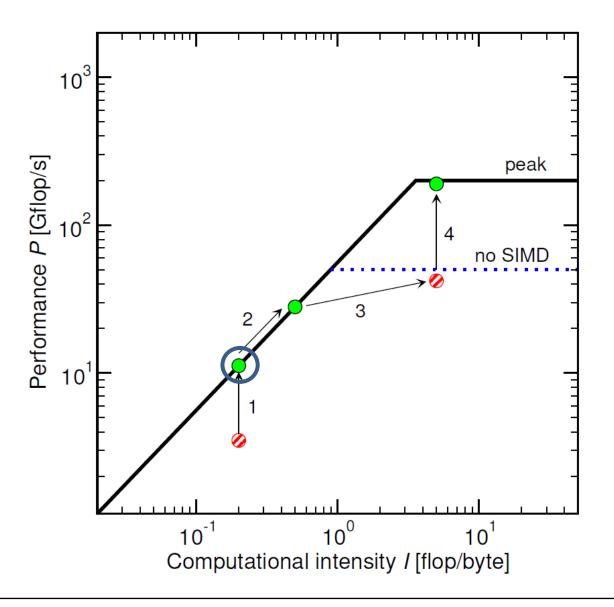

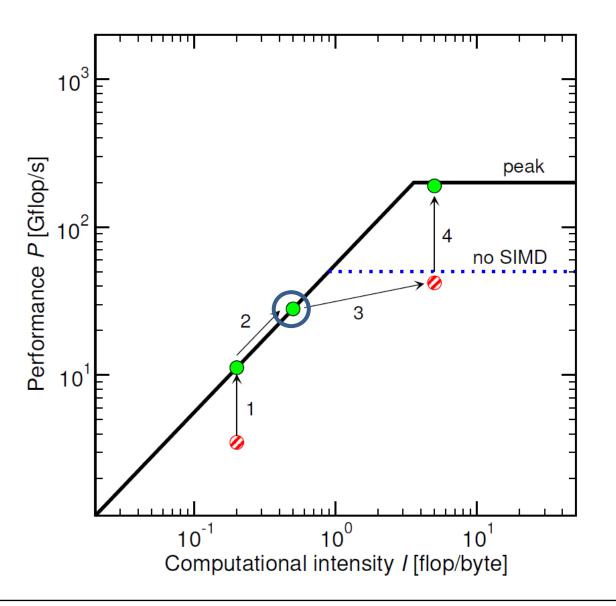

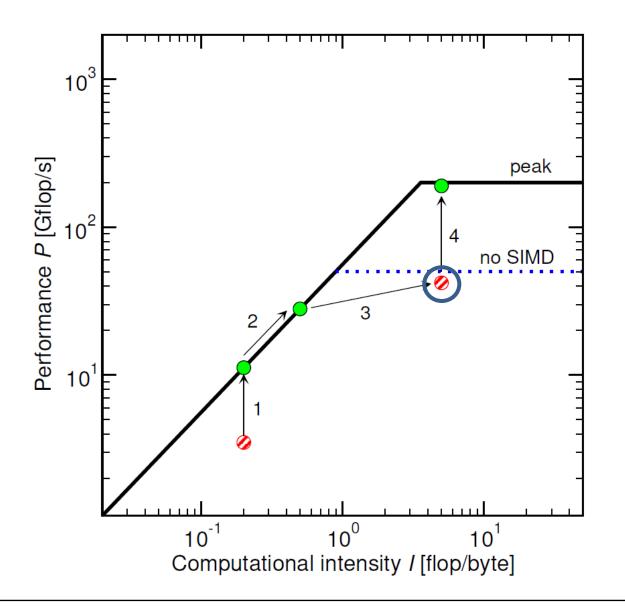

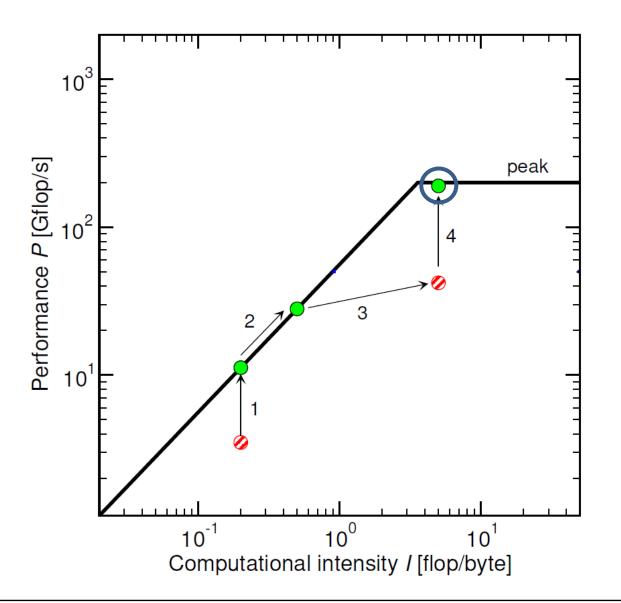

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

#### Example: do i=1,N; s=s+a(i); enddo

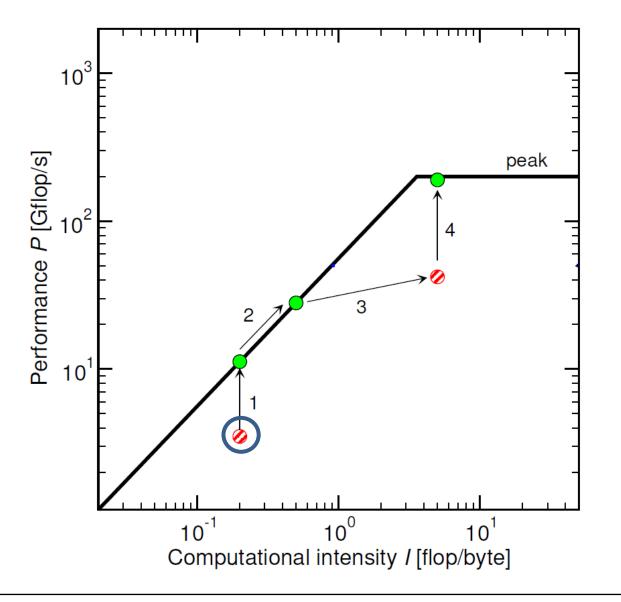

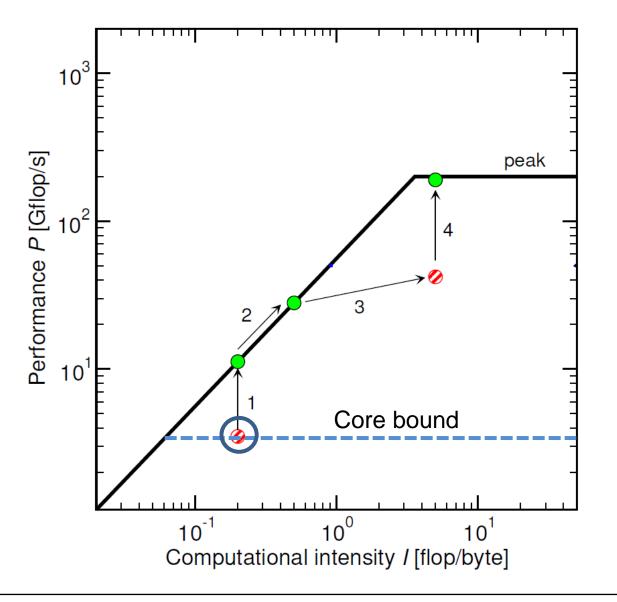

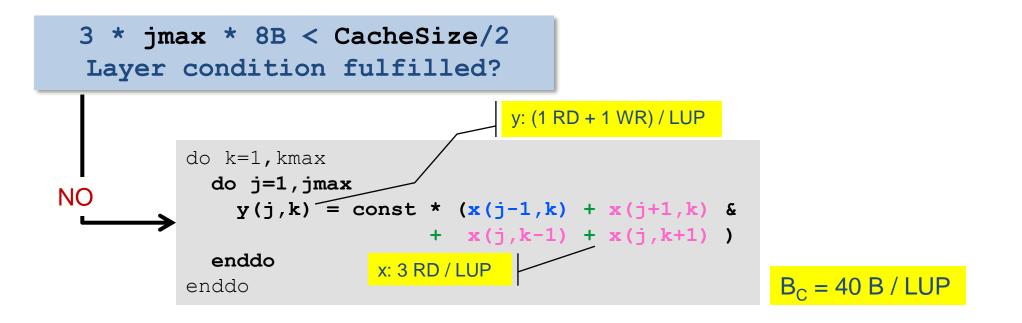

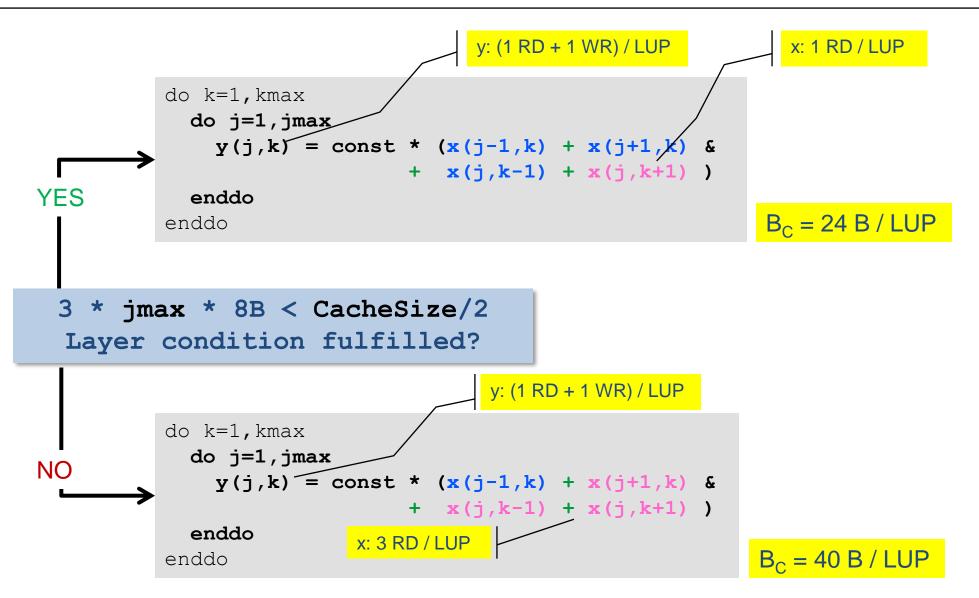

Hit the BW bottleneck by good serial code (e.g., plain Python → Fortran)

- Hit the BW bottleneck by good serial code (e.g., plain Python → Fortran)

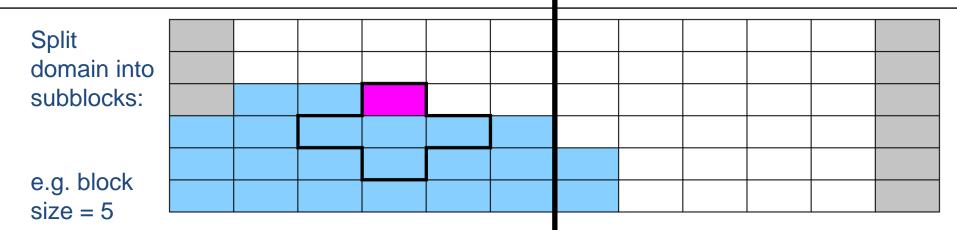

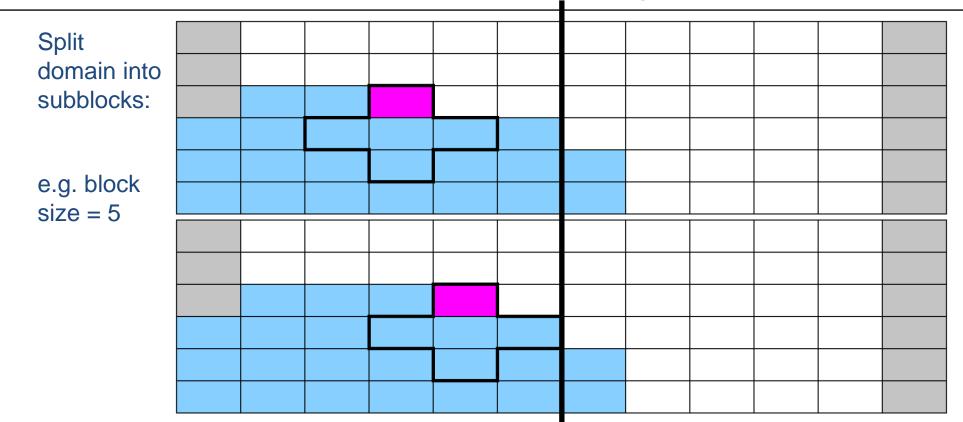

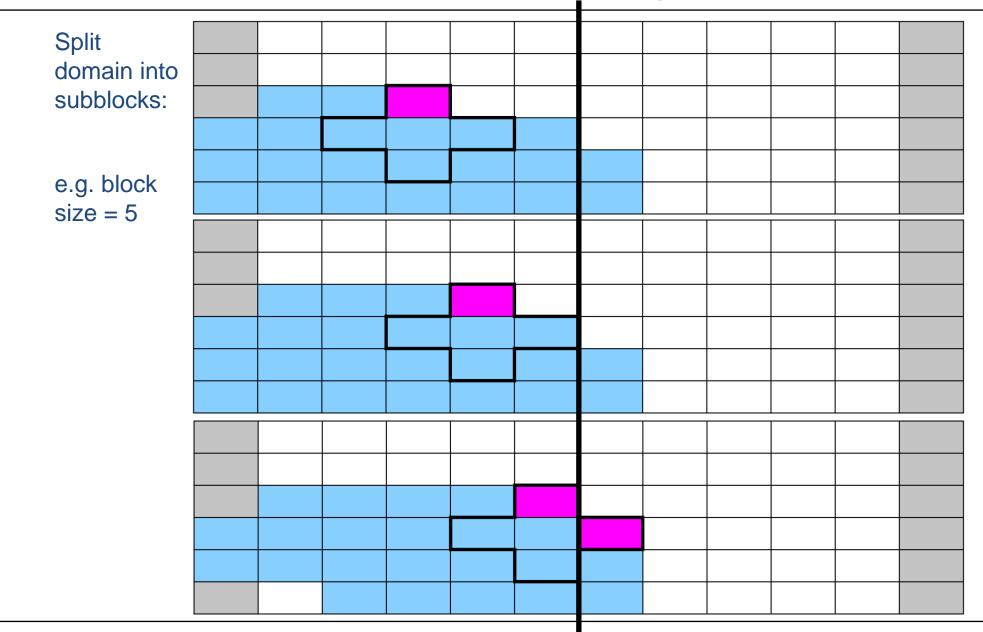

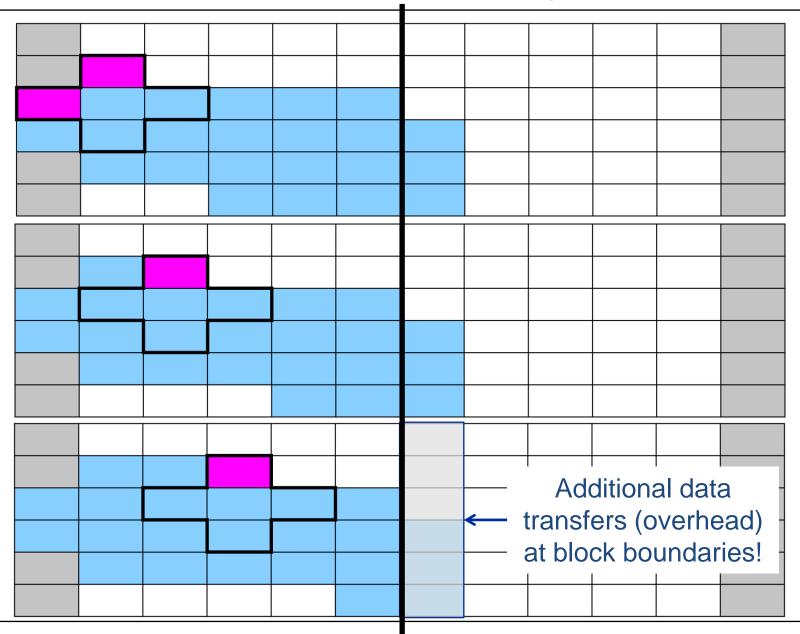

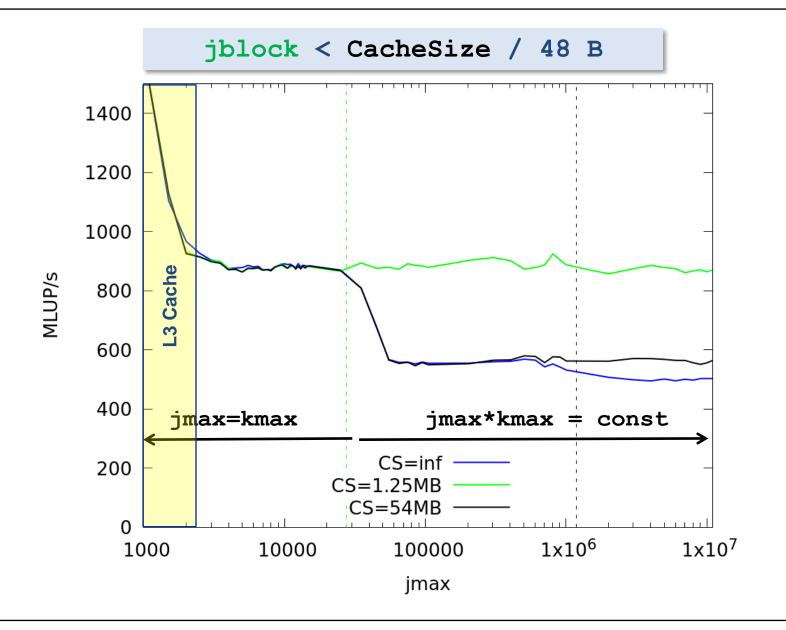

- 2. Increase intensity to make better use of BW bottleneck (e.g., spatial loop blocking)

- Hit the BW bottleneck by good serial code (e.g., plain Python → Fortran)

- 2. Increase intensity to make better use of BW bottleneck (e.g., spatial loop blocking)

- 3. Increase intensity and go from memory bound to core bound (e.g., temporal blocking)

- Hit the BW bottleneck by good serial code (e.g., plain Python → Fortran)

- 2. Increase intensity to make better use of BW bottleneck (e.g., spatial loop blocking)

- 3. Increase intensity and go from memory bound to core bound (e.g., temporal blocking)

- 4. Hit the core bottleneck by good serial code (e.g., -fno-alias, SIMD intrinsics)

Friedrich-Alexander-Universität Erlangen-Nürnberg

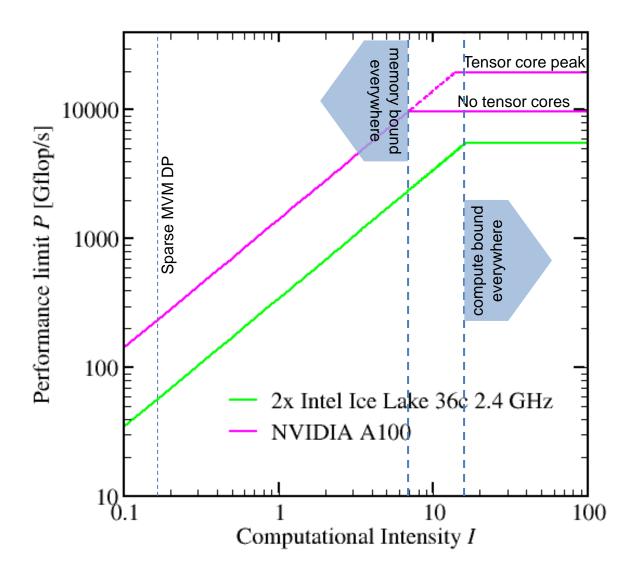

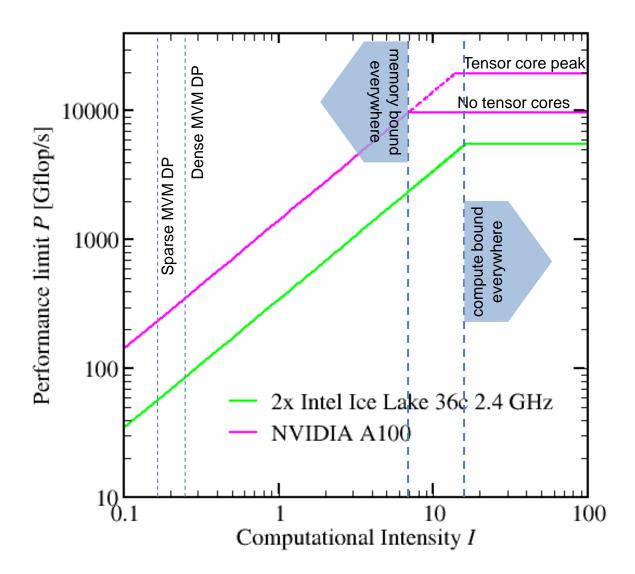

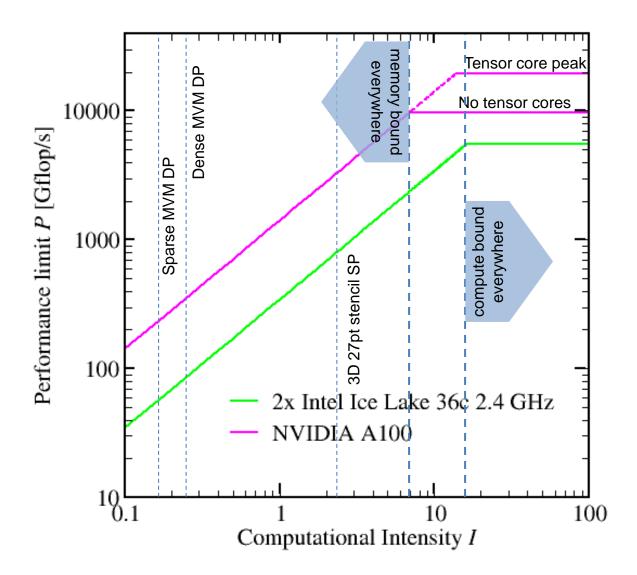

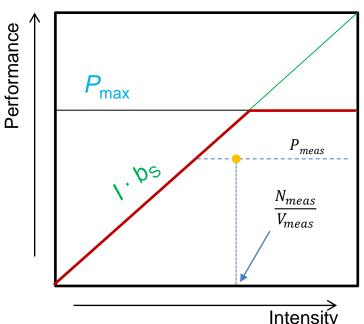

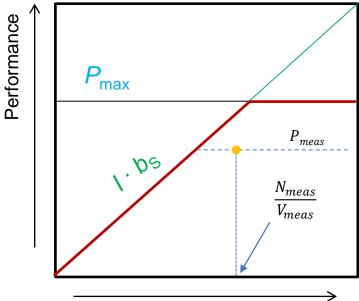

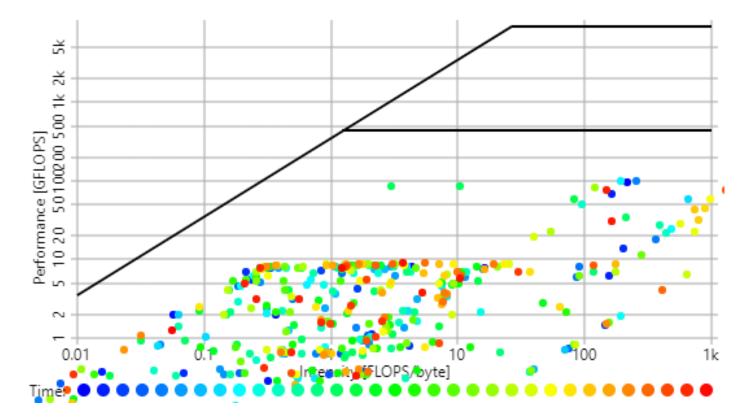

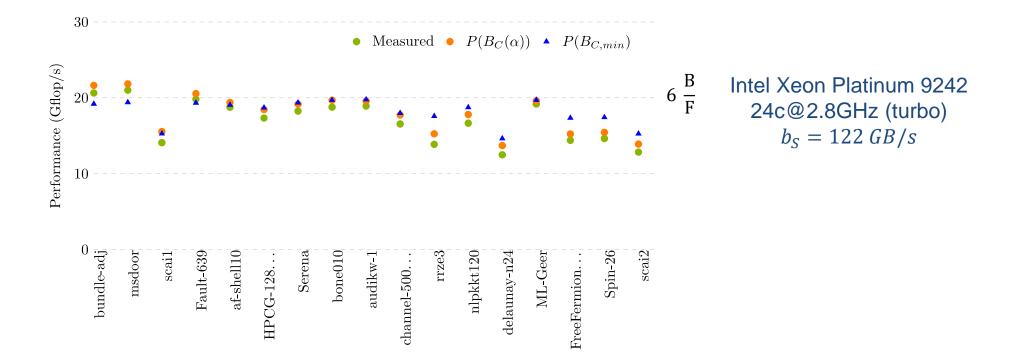

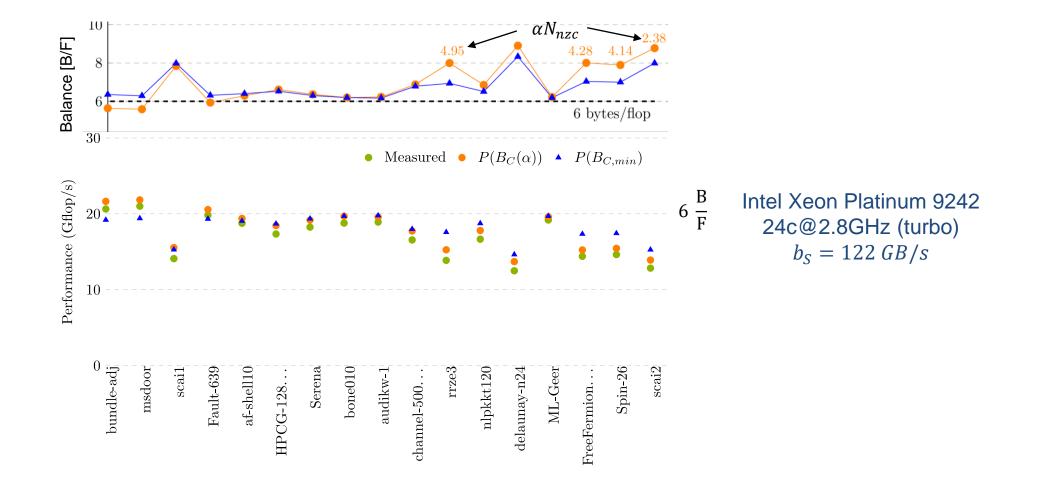

# Diagnostic / phenomenological Roofline modeling

- What if we cannot predict the intensity/balance?

- Code very complicated

- Code not available

- Parameters unknown

- Doubts about correctness of analysis

- What if we cannot predict the intensity/balance?

- Code very complicated

- Code not available

- Parameters unknown

- Doubts about correctness of analysis

- What if we cannot predict the intensity/balance?

- Code very complicated

- Code not available

- Parameters unknown

- Doubts about correctness of analysis

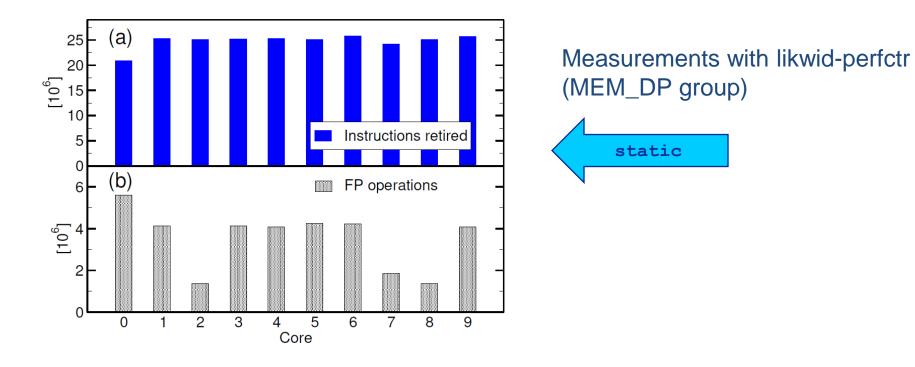

- Measure data volume V<sub>meas</sub> (and work N<sub>meas</sub>)

- Hardware performance counters

- Tools: likwid-perfctr, PAPI, Intel Vtune,...

- What if we cannot predict the intensity/balance?

- Code very complicated

- Code not available

- Parameters unknown

- Doubts about correctness of analysis

- Measure data volume V<sub>meas</sub> (and work N<sub>meas</sub>)

- Hardware performance counters

- Tools: likwid-perfctr, PAPI, Intel Vtune,...

- Insights + benefits

- Compare analytic model and measurement  $\rightarrow$  validate model

- Can be applied (semi-)automatically

- Useful in performance monitoring of user jobs on clusters

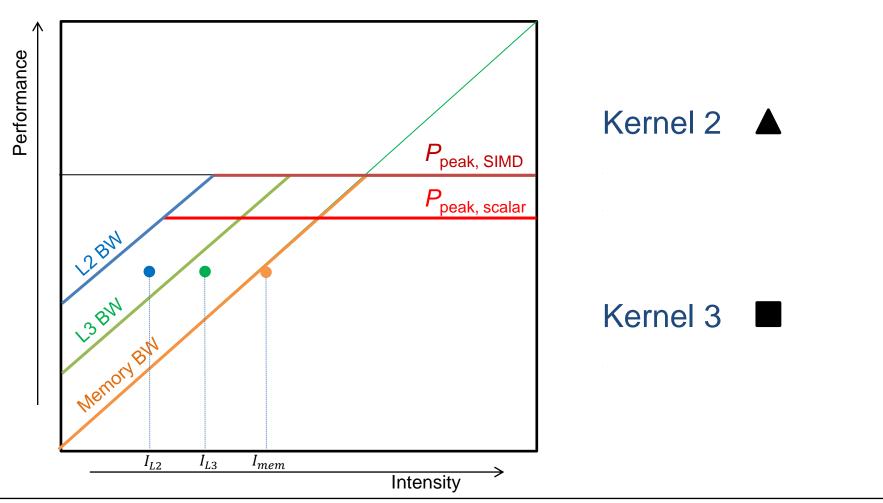

Kernel 1

Multiple bandwidth bottlenecks  $\rightarrow$  need *I* for each one ( $I_{mem}$ ,  $I_{L3}$ ,  $I_{L2}$ , ...)

Kernel 1

Multiple bandwidth bottlenecks  $\rightarrow$  need *I* for each one ( $I_{mem}$ ,  $I_{L3}$ ,  $I_{L2}$ , ...)

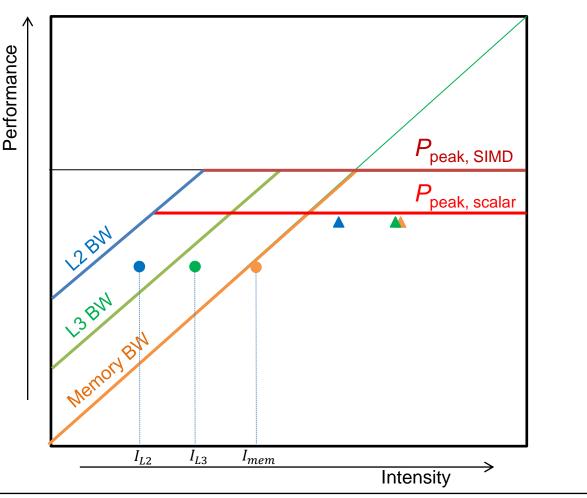

Multiple bandwidth bottlenecks  $\rightarrow$  need *I* for each one ( $I_{mem}$ ,  $I_{L3}$ ,  $I_{L2}$ , ...)

Performance close to memory BW ceiling but far away from others

→ indicates **memory bound**

Multiple bandwidth bottlenecks  $\rightarrow$  need *I* for each one ( $I_{mem}$ ,  $I_{L3}$ ,  $I_{L2}$ , ...)

#### Kernel 1

- Performance close to memory BW ceiling but far away from others

- $\rightarrow$  indicates **memory bound**

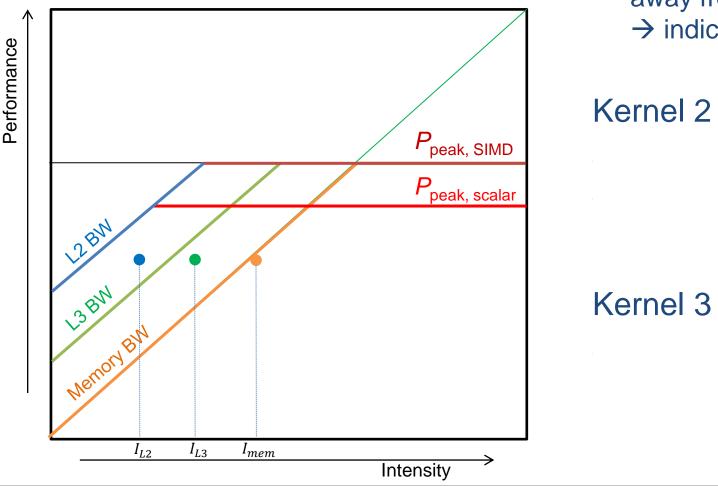

### Kernel 2

Multiple bandwidth bottlenecks  $\rightarrow$  need *I* for each one ( $I_{mem}$ ,  $I_{L3}$ ,  $I_{L2}$ , ...)

#### Kernel 1

Performance close to memory BW ceiling but far away from others

→ indicates memory bound

### Kernel 2

- Performance not near any BW ceiling

- Performance close to scalar peak ceiling

indicates scalar core-bound peak code

Multiple bandwidth bottlenecks  $\rightarrow$  need *I* for each one ( $I_{mem}$ ,  $I_{L3}$ ,  $I_{L2}$ , ...)

#### Kernel 1

Performance close to memory BW ceiling but far away from others

→ indicates memory bound

### Kernel 2

- Performance not near any BW ceiling

- Performance close to scalar peak ceiling

indicates scalar core-bound peak code

Multiple bandwidth bottlenecks  $\rightarrow$  need *I* for each one ( $I_{mem}$ ,  $I_{L3}$ ,  $I_{L2}$ , ...)

#### Kernel 1

Performance close to memory BW ceiling but far away from others

→ indicates memory bound

### Kernel 2

- Performance not near any BW ceiling

- Performance close to scalar peak ceiling

indicates scalar core-bound peak code

### Kernel 3

Performance not anywhere near any ceiling

→ There must be an (as yet) unknown in-core performance limit P<sub>max</sub>

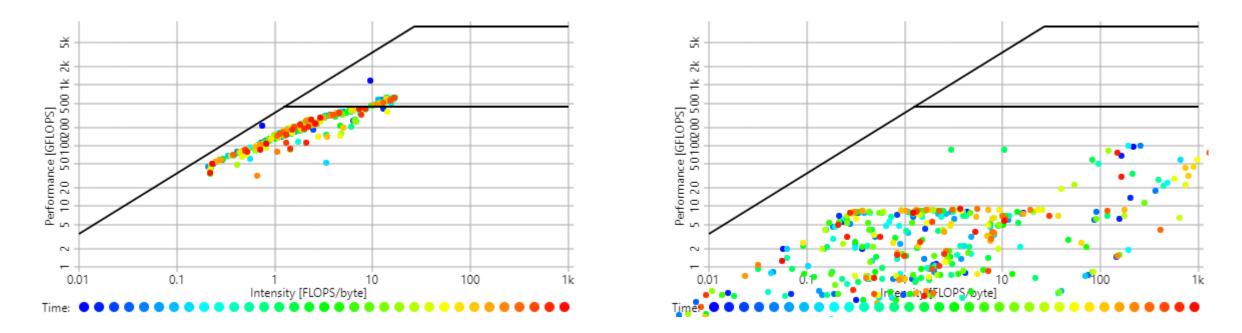

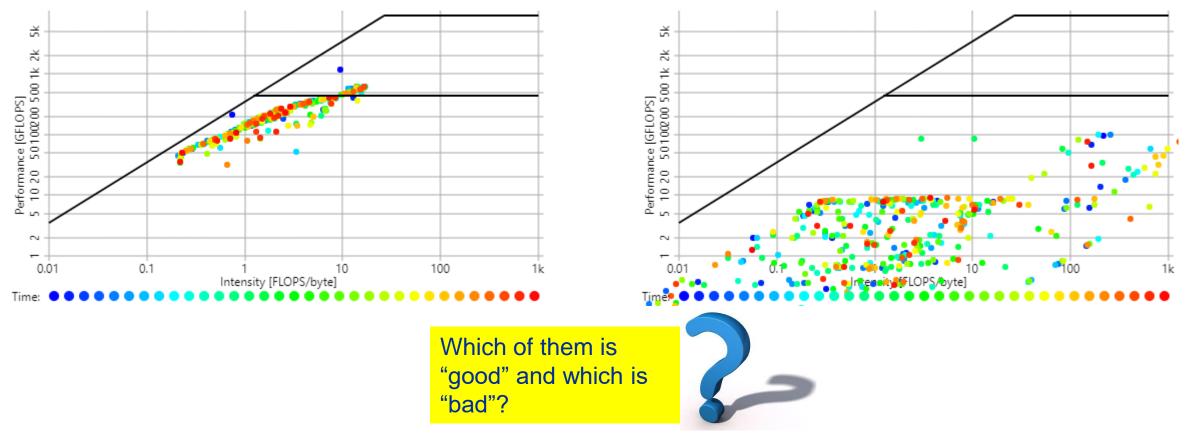

# Roofline and performance monitoring of clusters

#### Two cluster jobs...

Cluster monitoring framework: ClusterCockpit <u>https://clustercockpit.org</u> Come visit Booth #1311 (LRZ)

# Roofline and performance monitoring of clusters

#### Two cluster jobs...

Cluster monitoring framework: ClusterCockpit <u>https://clustercockpit.org</u> Come visit Booth #1311 (LRZ)

## **Roofline conclusion**

- Roofline = simple first-principle model for upper performance limit of datastreaming loops

- Machine model  $(P_{max}, b_S)$  + application model (I)

- Conditions apply, extensions exist

- Two modes of operation

- Predictive: Calculate I, calculate upper limit, validate model, optimize, iterate

- Diagnostic: Measure I and P, compare with roof

- Challenge of predictive modeling: Getting  $P_{max}$  and I right

Friedrich-Alexander-Universität Erlangen-Nürnberg

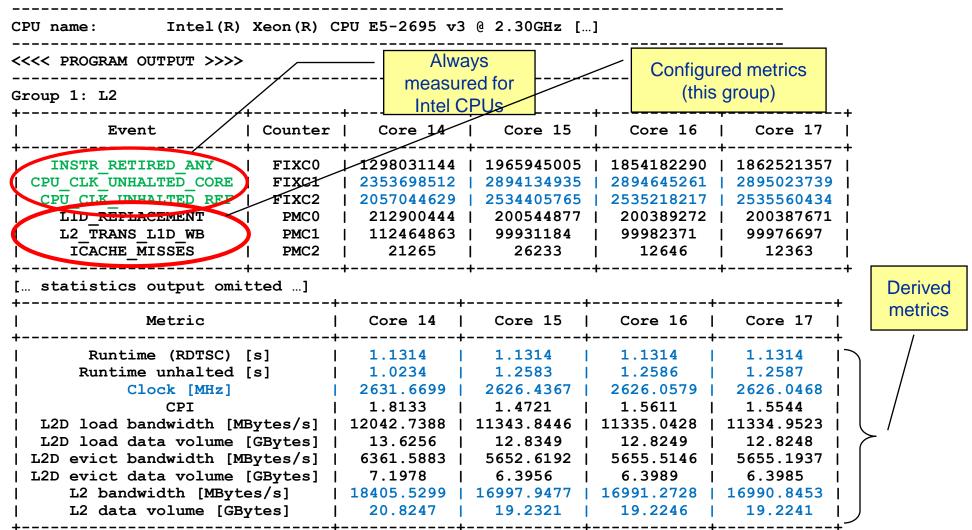

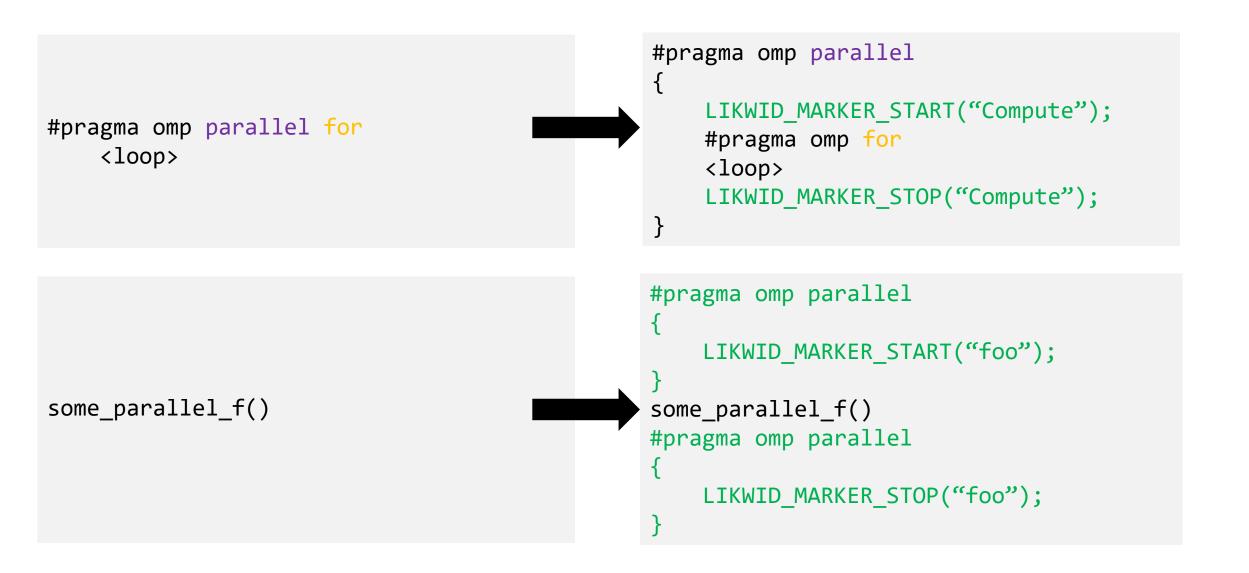

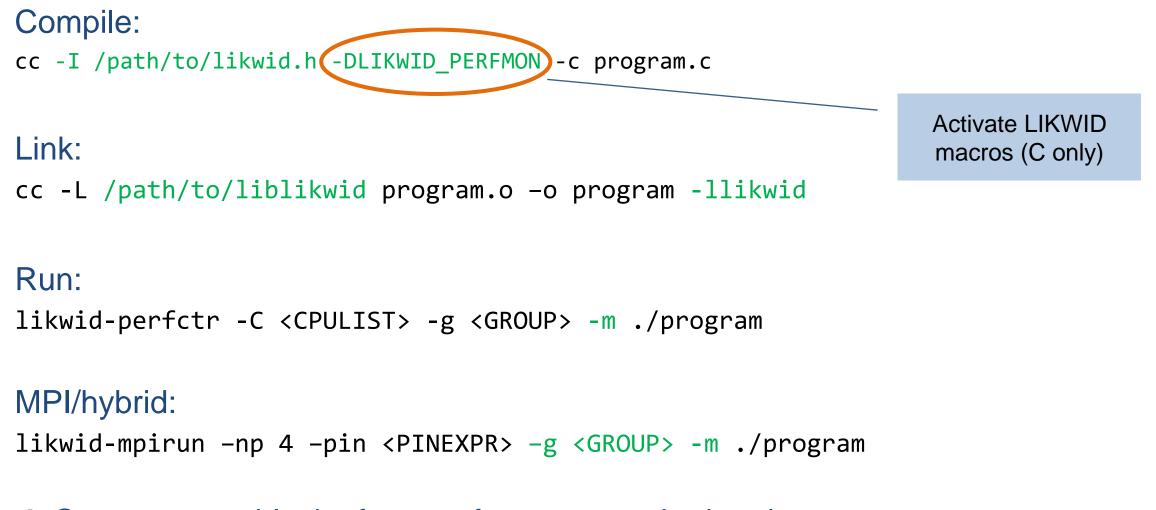

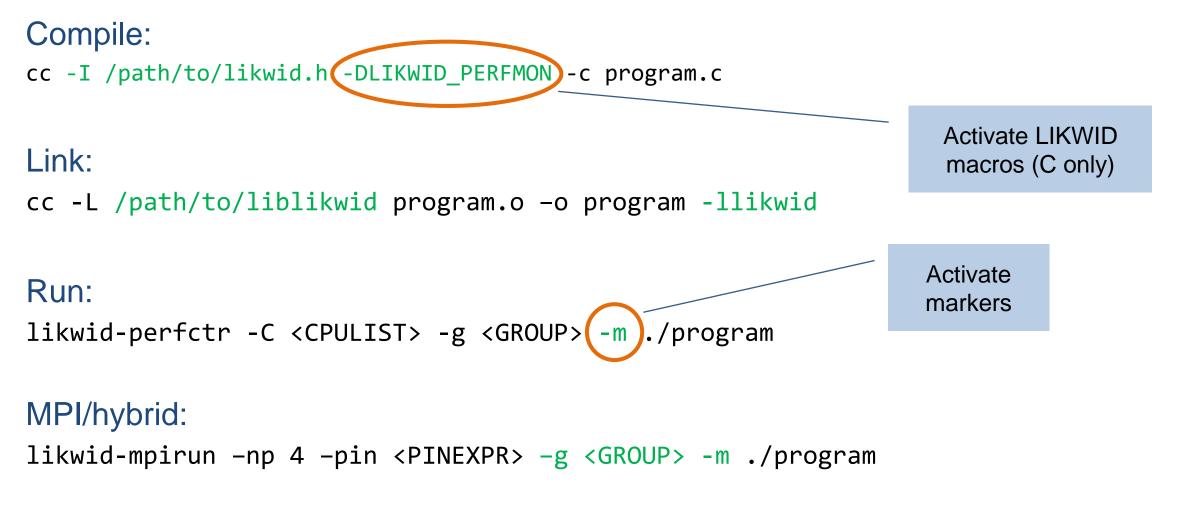

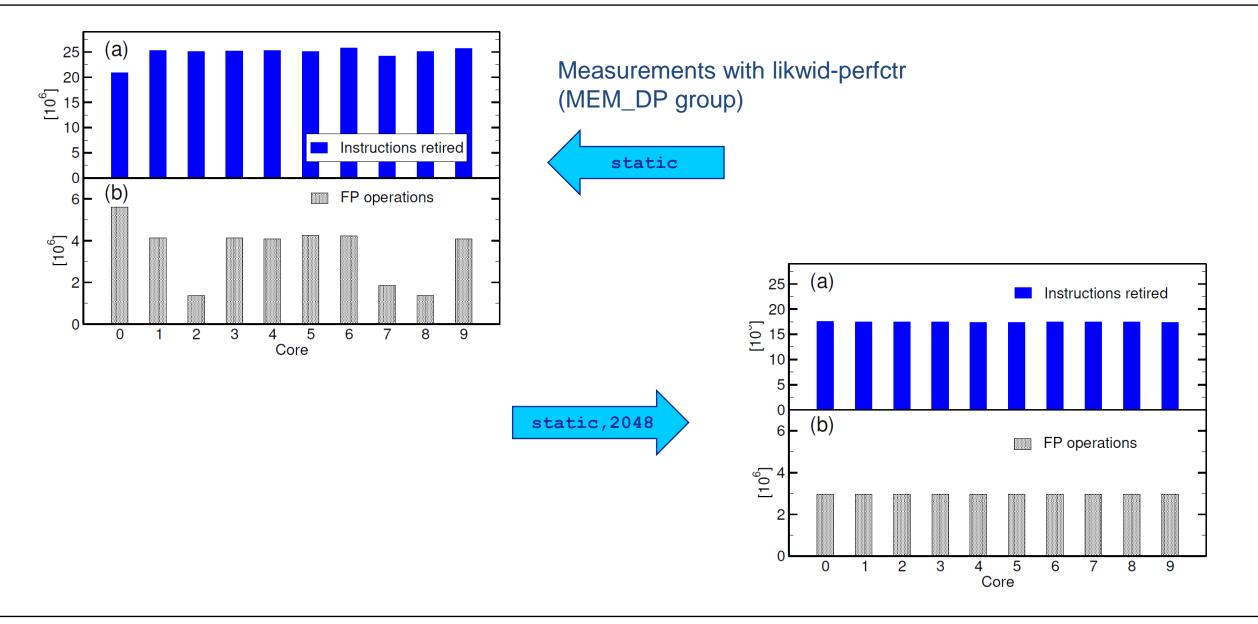

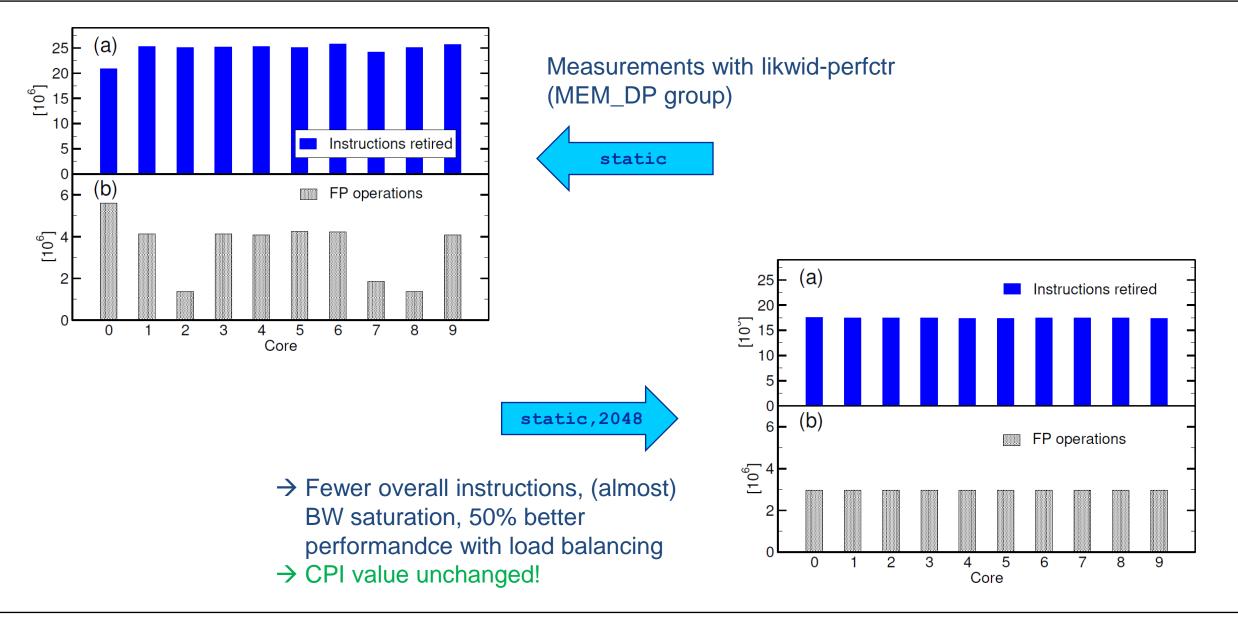

# Performance analysis with hardware metrics

likwid-perfctr

## Probing performance behavior

- How do we find out about the performance properties and requirements of a parallel code?

Profiling via advanced tools is often overkill

- A coarse overview is often sufficient: likwid-perfctr

- Simple measurement of hardware performance metrics

- Preconfigured and extensible metric groups, list with likwid-perfctr -a: BRANCH: Branch pred

- Operating modes:

- Wrapper

- Stethoscope

- Timeline

- Marker API

BRANCH: Branch prediction miss rate/ratio CLOCK: Clock frequency of cores DATA: Load to store ratio FLOPS\_DP: Double Precision MFlops/s FLOPS\_SP: Single Precision MFlops/s L2: L2 cache bandwidth in MBytes/s L2CACHE: L2 cache miss rate/ratio L3: L3 cache bandwidth in MBytes/s L3CACHE: L3 cache miss rate/ratio MEM: Main memory bandwidth in MBytes/s ENERGY: Power and energy consumption

# Best practices for Performance profiling

Focus on resource utilization and instruction mix! Metrics to measure:

- Operation throughput (Flops/s)

- Overall instruction throughput (CPI or IPC)

- Instruction breakdown:

- FP instructions

- loads and stores

- branch instructions

- other instructions

- Instruction breakdown to SIMD width (scalar, SSE, AVX, AVX512 for X86). (only arithmetic instructions on most architectures)

All above metrics can be acquired using performance groups: MEM DP, MEM SP, BRANCH, DATA, L2, L3

- Data volumes and bandwidths to

- main memory (GB and GB/s)

- cache levels (GB and GB/s)

Useful diagnostic metrics are:

- Clock frequency (GHz)

- Power (W)

| PU name:                                 | Intel(R)     | Xeon(R) C                      | PU E5-2695 v3 | @ 2.30GHz [ | ]                      |            |

|------------------------------------------|--------------|--------------------------------|---------------|-------------|------------------------|------------|

| <<< PROGRAM                              | OUTPUT >>>>  |                                |               |             |                        |            |

| roup 1: L2                               |              |                                |               |             |                        |            |

| Eve                                      | nt           | Counter                        | Core 14       | Core 15     | Core 16                | Core 17    |

| INSTR RET                                | IRED ANY     | <br>  FIXC0                    | 1298031144    | 1965945005  | 1854182290             | 1862521357 |

| CPU CLK UNH                              | ALTED CORE   | FIXC1                          | 2353698512    | 2894134935  | 2894645261             | 2895023739 |

| CPU CLK UN                               | HALTED REF   | FIXC2                          | 2057044629    | 2534405765  | 2535218217             | 2535560434 |

| LID_REPL                                 | ACEMENT      | PMC0                           | 212900444     | 200544877   | 200389272              | 200387671  |

| L2_TRANS                                 | L1D_WB       | PMC1                           | 112464863     | 99931184    | 99982371               | 99976697   |

| ICACHE_                                  | MISSES       | PMC2                           | 21265         | 26233       | 12646                  | 12363      |

| . statistics                             | output omi   | tted]                          | ++            | ++          | ++                     |            |

|                                          | Metric       | 1                              | Core 14       | Core 15     | Core 16                | Core 17    |

| Runti                                    | me (RDTSC)   | +<br>[s]                       | 1.1314        | 1.1314      | 1.1314                 | 1.1314     |

| Runtime unhalted [s]                     |              | 1.0234                         | 1.2583        | 1.2586      | 1.2587                 |            |

|                                          |              | 2631.6699                      | 2626.4367     | 2626.0579   | 2626.0468              |            |

| CPI                                      |              | 1                              | 1.8133        | 1.4721      | 1.5611                 | 1.5544     |

| L2D load bandwidth [MBytes/s]            |              | Bytes/s]                       | 12042.7388    | 11343.8446  | 11335.0428             | 11334.9523 |

| L2D load data volume [GBytes]            |              |                                | 13.6256       | 12.8349     | 12.8249                | 12.8248    |

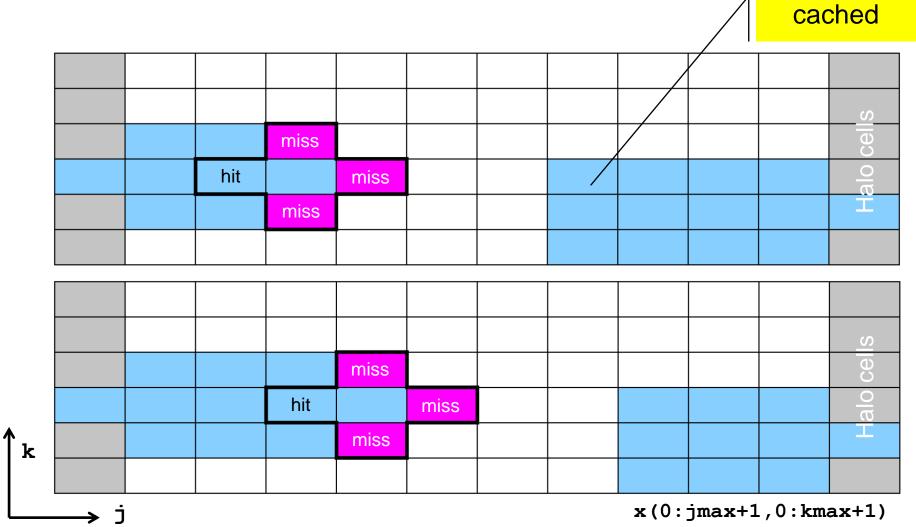

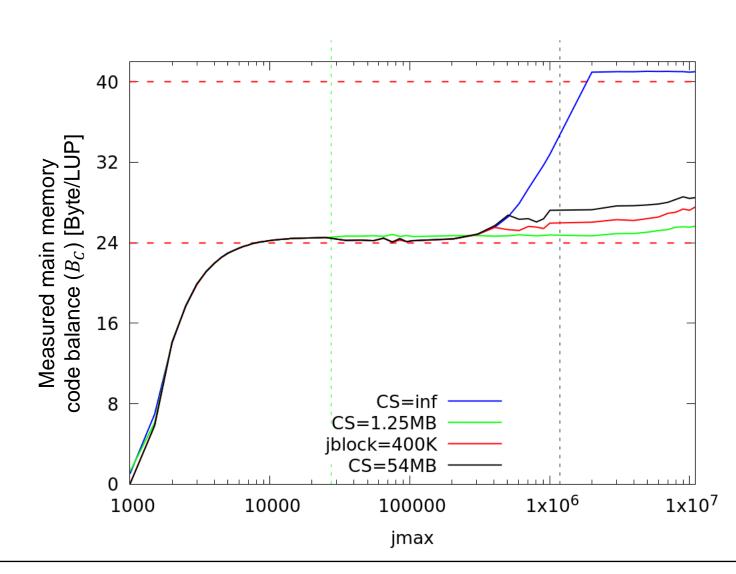

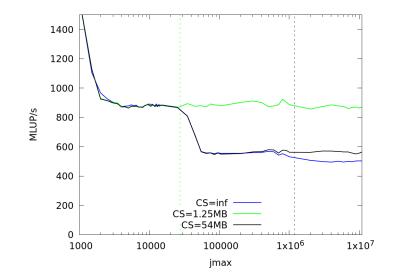

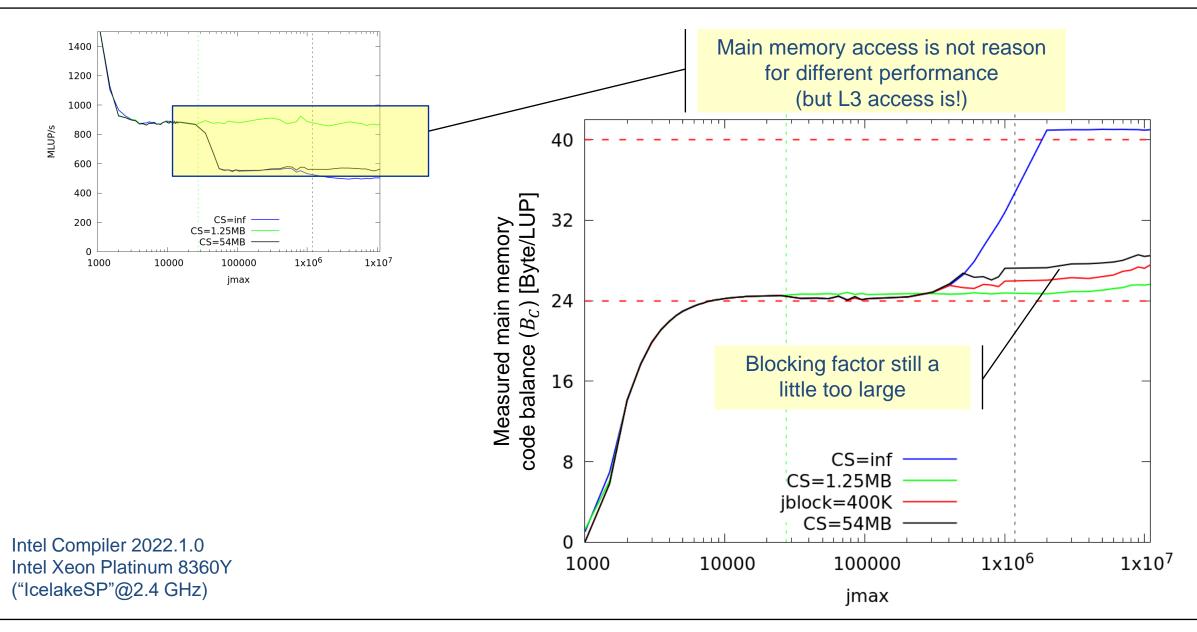

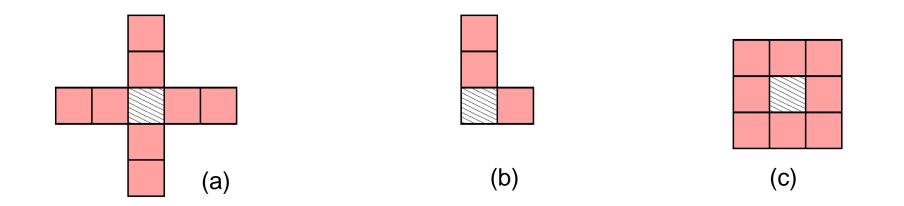

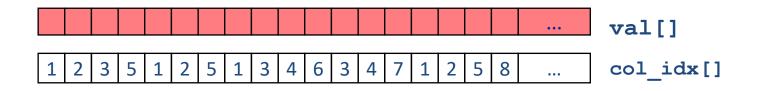

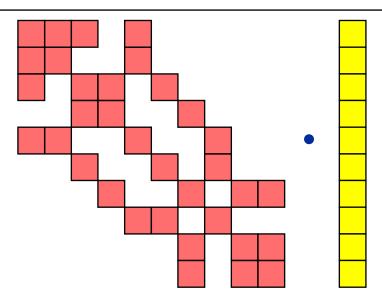

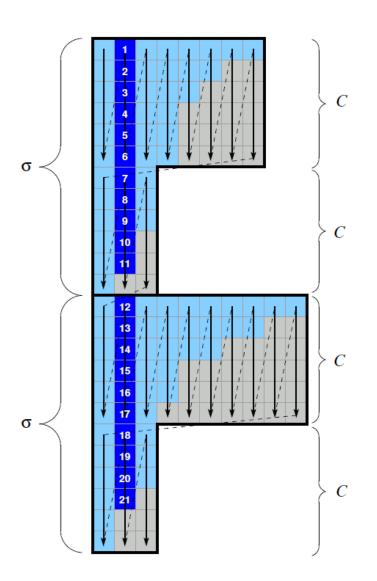

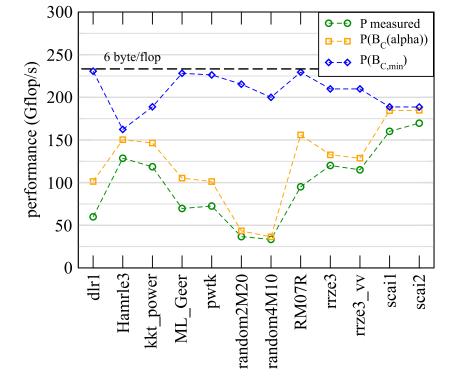

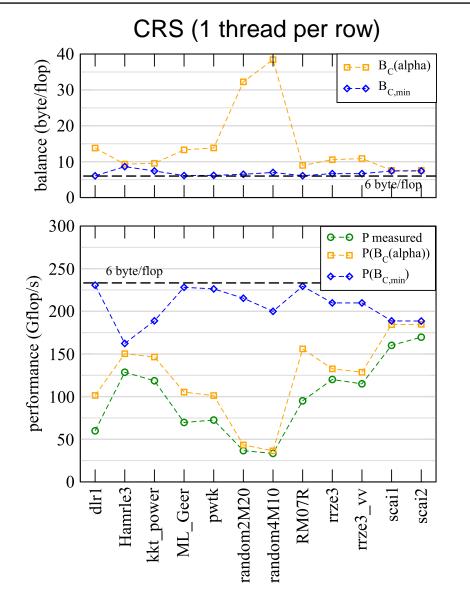

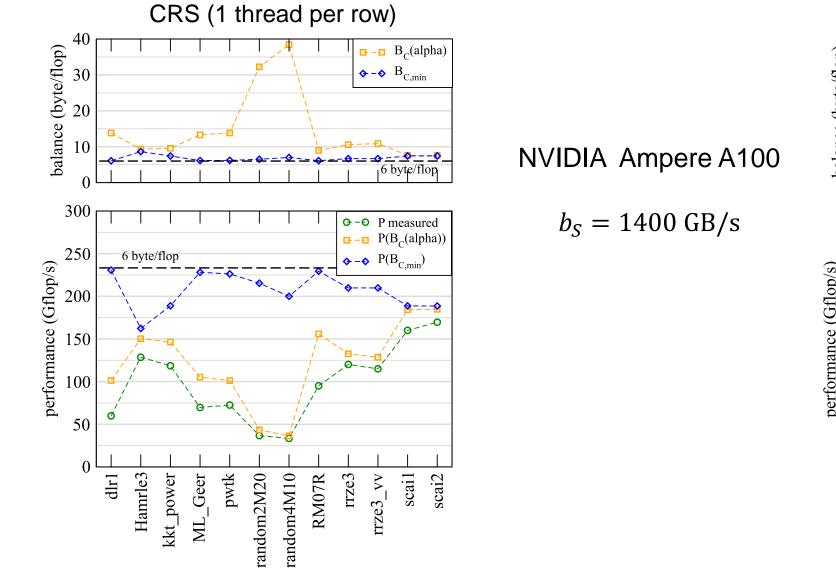

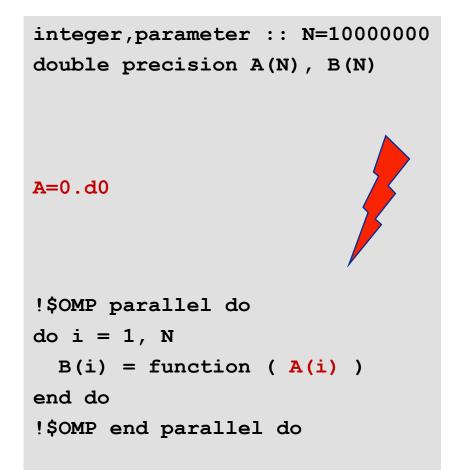

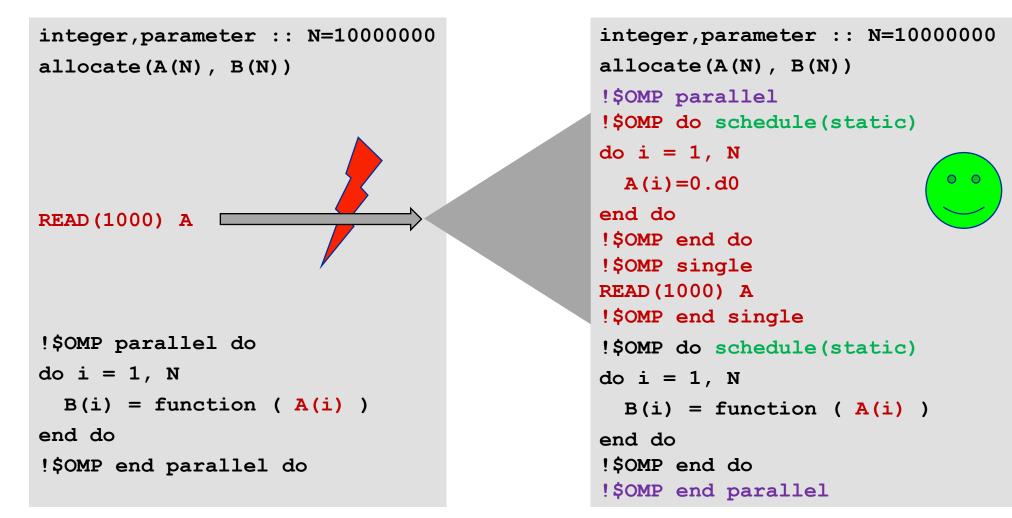

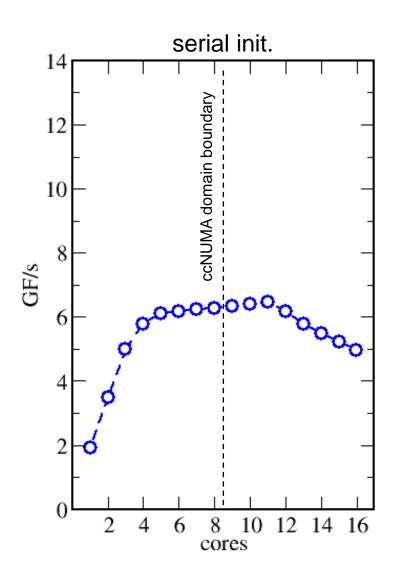

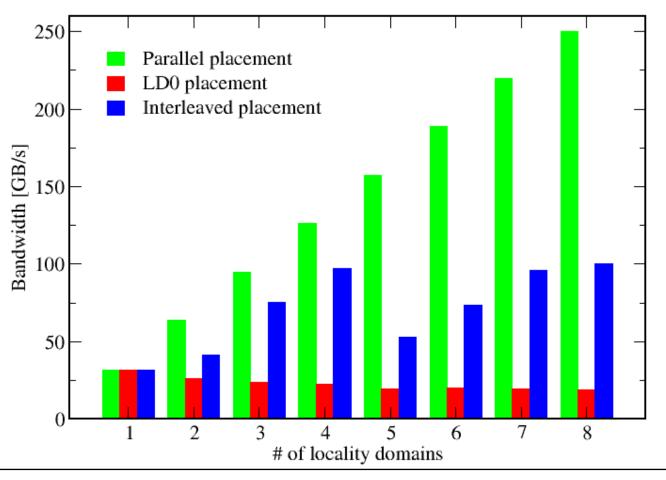

|                                          |              | L2D evict bandwidth [MBytes/s] |               |             | 5655.5146              | 5655.1937  |