Grant Nr. 01IH13009 Duration: 03/2017 – 02/2020

DEG Deutsche Forschungsgemeinschaft

# **ProPE** – A joint effort to establish a unified service infrastructure for Performance Engineering in German HPC-Centers

G. Wellein, J. Eitzinger, T. Röhl University of Erlangen-Nürnberg Erlangen Regional Computing Center (RRZE)

M. Müller, M. Petry, D. Schmidl **RWTH Aachen University** IT Center (RWTH Aachen University) W. Nagel, R. Dietrich, F. Winkler Technical University Dresden **Centre for Information Services and** High Performance Computing(ZIH)

### **Overview and Partners**

HPC competence in German HPC centers is distributed across the country. The Gauss-Allianz is an initiative to integrate and organize TIER 2/3 HPC landscape in Germany. Furthermore there are multiple local efforts: bwHPC, KONWIHR, HKHLR, HLRN and JARA-HPC. Our contribution is to integrate with and built on already existing efforts and further drive the final goal of an hierarchical yet German HPC and integrated infrastructure with emphasis on Performancean Engineering.

## **ProPE Project Structure**

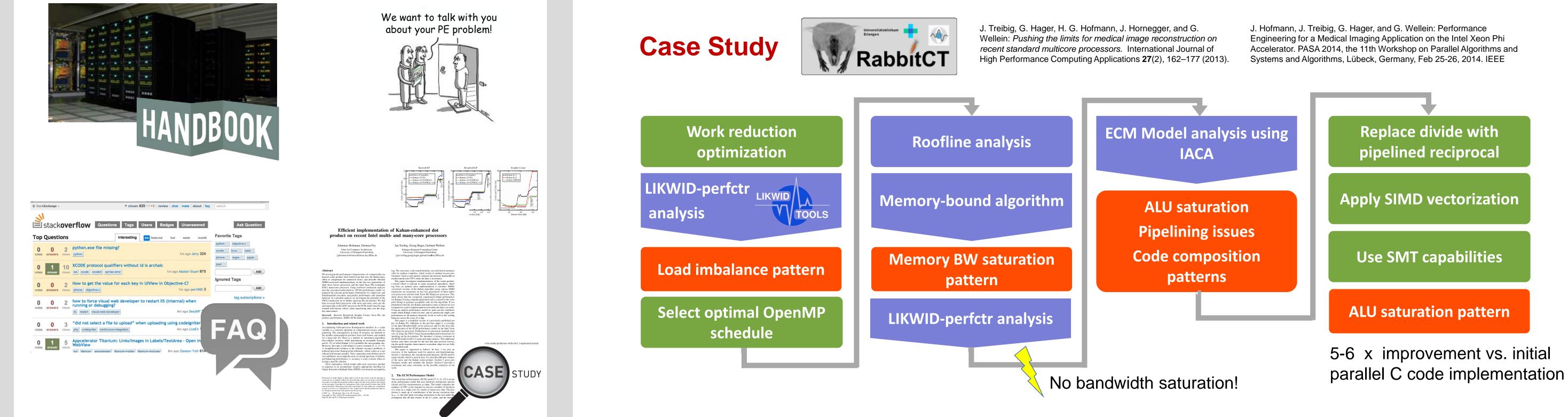

Important ingredients will be **show**cases by

- Carrying out real **Performance** Projects

- Organizing tutorials and researcher exchanges between sites

#### **Partners**

- RRZE (University Erlangen-Nuremberg)

- IT Center (RWTH Aachen University)

- ZIH (Technical University Dresden)

## **Associated Partners**

- KONWIHR

- TU Munich (Prof. Bungartz)

- Forschungszentrum Jülich

- Technical University Bergakademie Freiberg

# Dissemination and Documentation

Increase publicity for the project and raise general awareness for performance issues. Build a central web offering, create content and provide resources to maintain it.

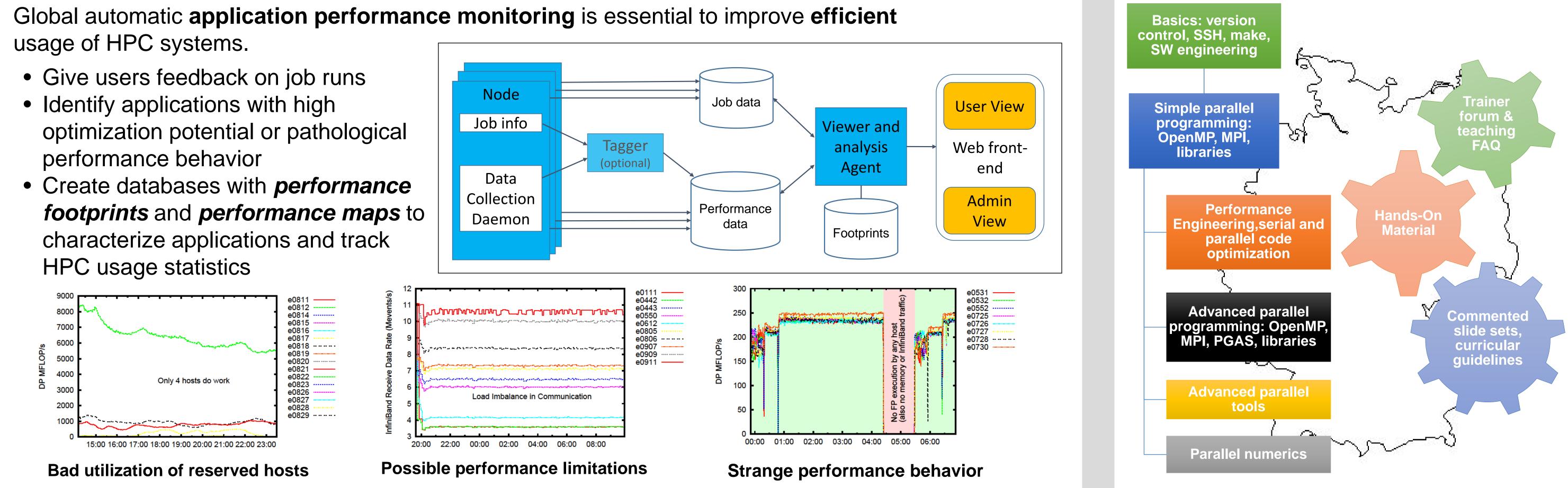

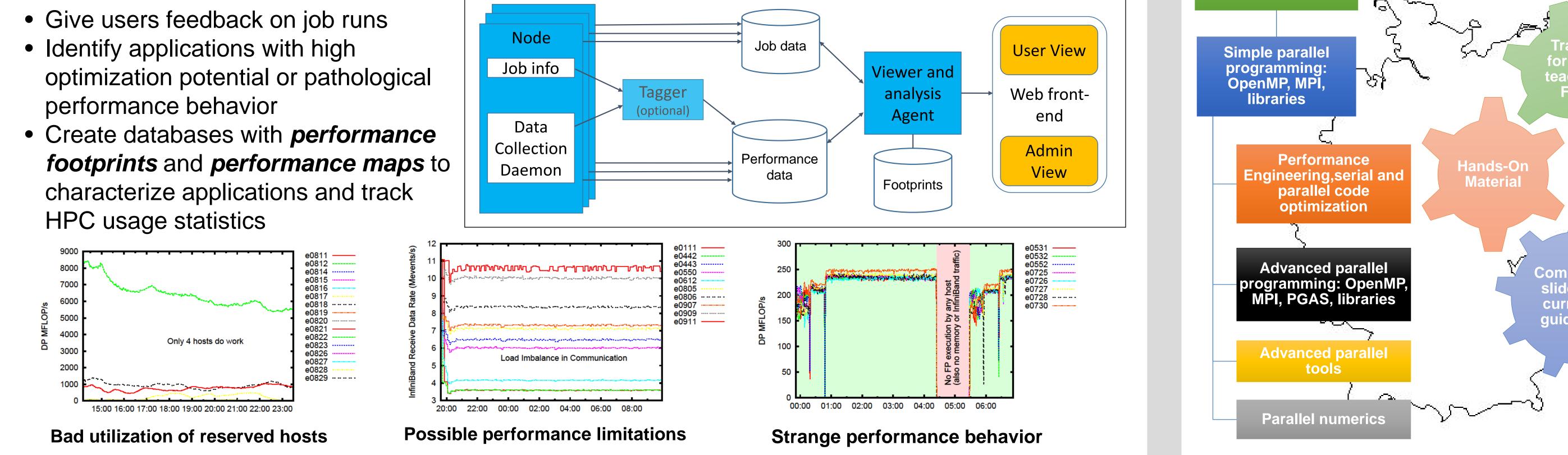

• Establishing system-wide job specific performance profiling infrastructures

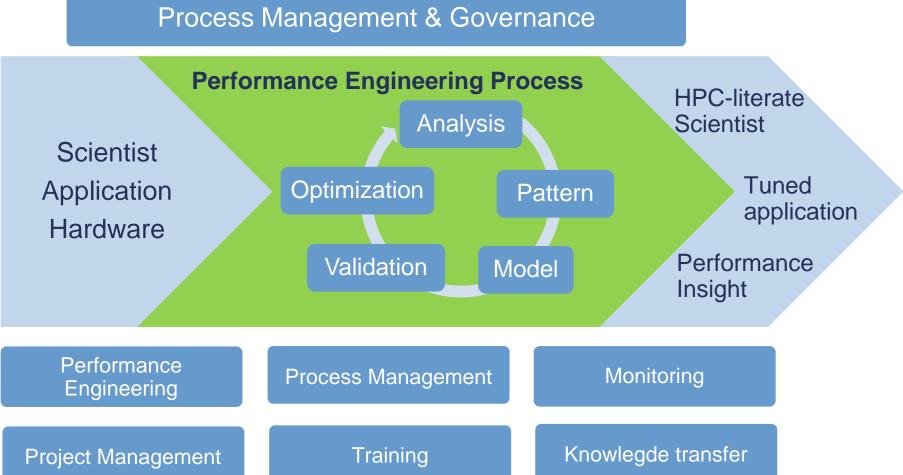

## **Structured PE-Process**

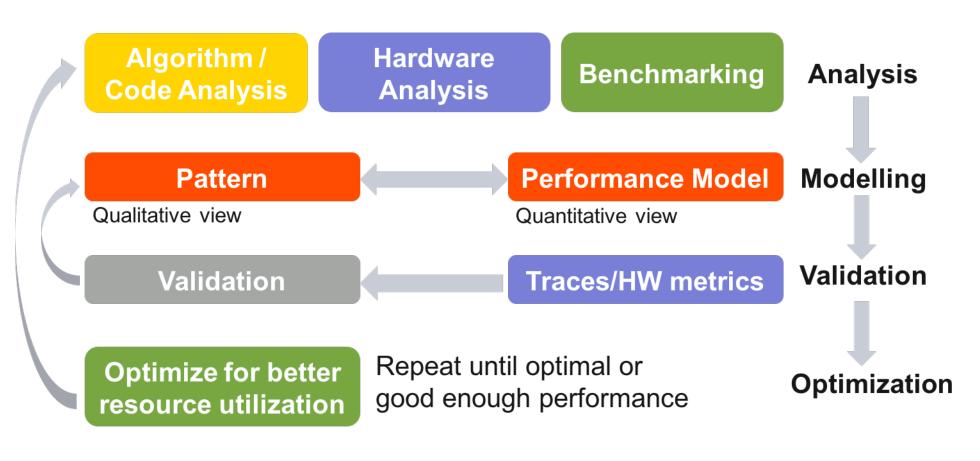

The core activity of analyzing and optimizing application performance is guided by a systematic PE-Process. At its core are typical limiting performance settings called performance patterns. To validate and to get a quantitative view of a pattern white box performance models employed. are Identifying a performance pattern is achieved by a set of hardware performance counter metrics but might also involve static code analysis and benchmarking results.

## **Application Performance Monitoring**

- optimization potential or pathological performance behavior

- *footprints* and *performance maps* to characterize applications and track

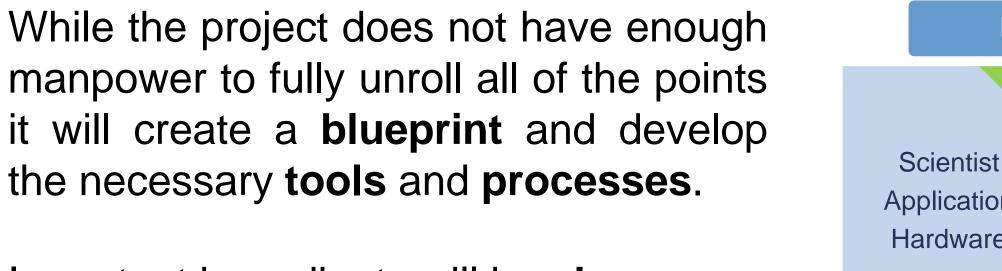

## **HPC Curriculum**