## Process-Oriented Performance Engineering Service Infrastructure for Scientific Software at German HPC Centers

Whitepaper — July 2020

Dieter an Mey, Alesja Dammer, Robert Dietrich, Jan Eitzinger, Nicole Filla, Georg Hager, Jonas Hahnfeld, Paul Kapinos, Thomas Röhl, Daniel Schürhoff, Sandra Wienke, Frank Winkler, Thomas Zeiser

| Gerhard Wellein              | lein — Friedrich-Alexander Universität Erlangen-Nürnberg,<br>Regionales Rechenzentrum Erlangen (RRZE) – (coordi |                                                                                                 |

|------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Matthias S. Müller — RWTH Aa |                                                                                                                 | RWTH Aachen University, IT Center (RWTH)                                                        |

| Wolfgang E. Nagel —          |                                                                                                                 | Technical University Dresden,<br>Zentrum für Informationsdienste und Hochleistungsrechnen (ZIH) |

# Contents

| 1                                                                 | Introduction |          |                                                                     | 2        |

|-------------------------------------------------------------------|--------------|----------|---------------------------------------------------------------------|----------|

| 2                                                                 | Cur          | rent sta | tus of German HPC landscape                                         | 3        |

| 3                                                                 | Req          | uiremei  | nts for a national Performance Engineering infrastructure           | 6        |

| 4 Components of a national Performance Engineering infrastructure |              |          |                                                                     |          |

|                                                                   | 4.1          | ProPE    | Performance Engineering Process                                     | 8        |

|                                                                   |              | 4.1.1    | Iterative scientific process for performance engineering            | 8        |

|                                                                   |              | 4.1.2    | Required skills                                                     | 10       |

|                                                                   |              | 4.1.3    | Threshold-based performance analysis                                | 10       |

|                                                                   |              | 4.1.4    | Performance analysis with patterns                                  | 12       |

|                                                                   |              | 4.1.5    | The Performance Logbook                                             | 12       |

|                                                                   |              | 4.1.6    | File format standards for Job Meta- and Metric-data                 | 13       |

|                                                                   |              | 4.1.7    | The broader context of performance engineering                      | 13       |

|                                                                   | 4.2          | Establi  | ishment of a Distributed Support Infrastructure                     | 14       |

|                                                                   |              | 4.2.1    | HPC on Sites                                                        | 14       |

|                                                                   |              | 4.2.2    | HPC Expertise on Sites                                              | 15       |

|                                                                   |              | 4.2.3    | Development of a Distributed Support Structure                      | 15       |

|                                                                   |              | 4.2.4    | The Process Map for a Multi-Tier Distributed Support Infrastructure | 17       |

|                                                                   |              | 4.2.5    | Gathering User Feedback                                             | 20       |

|                                                                   | 4.3          | Perform  | mance Monitoring and Analysis                                       | 20       |

|                                                                   |              | 4.3.1    | An Infrastructure for System-Wide Job Monitoring                    | 21       |

|                                                                   |              | 4.3.2    | Performance Metrics                                                 | 21       |

|                                                                   |              | 4.3.3    | Data Collection                                                     | 21       |

|                                                                   |              | 4.3.4    | Data Storage                                                        | 23       |

|                                                                   |              | 4.3.5    | Data Analysis and Visualization                                     | 24       |

|                                                                   | 4.4          | Knowl    | edge Transfer and HPC Curriculum                                    | 27       |

|                                                                   |              | 4.4.1    | HPC target groups                                                   | 28       |

|                                                                   |              | 4.4.2    | Training                                                            | 29       |

|                                                                   |              | 4.4.3    | Knowledge Base                                                      | 30       |

| 5                                                                 | Sum          |          | nd Recommendation                                                   | 34       |

| 5                                                                 | Sum          | iniary a |                                                                     | 54       |

| A                                                                 | Perf         |          | e Engineering Process                                               | 36       |

|                                                                   | A.1          |          | ic guidelines for performance optimizations                         | 36       |

|                                                                   | A.2          | Detaile  | ed threshold analysis                                               | 37       |

| в                                                                 | Dict         | ributad  | Support Infrastructure                                              | 41       |

| D                                                                 | B.1          |          | ise on Participating Sites                                          | 41       |

|                                                                   | Б.1<br>В.2   |          | l Description of Core Process                                       | 41       |

|                                                                   |              |          |                                                                     | 42<br>44 |

|                                                                   | B.3          | User S   | atisfaction Survey Template                                         | 44       |

# Chapter 1

# Introduction

High Performance Computing (HPC) systems have always had complex system architectures that are subject to constant change, which presents a challenge for the use and programming of these systems. Furthermore, the increasing investment and operating costs of modern HPC systems require their efficient use. For this reason, HPC data centers offer their HPC users support services at various levels. Basic support is always available at helpdesk level, covering questions about available resources or access modes. In addition, larger centers often provide support for basic programming, code performance and parallelization issues. Some centers offer expert assistance on specific application areas, HPC topics, or may be involved in advanced HPC teaching topics. These activities are often based on the research topics of the academic institution in which the HPC center is embedded. The lack of experienced support staff and available financial resources has further increased the specialization of the HPC systems has increased significantly and new application communities have entered the field. These developments require the implementation of sustainable concepts for the provision of appropriate and qualified HPC support services, including training activities and nationwide joint efforts to use distributed HPC expertise in a transparent manner.

To this end the DFG has issued the call "Performance Engineering for Scientific Software" (Nov. 2015; see <sup>1</sup>) to demonstrate the need for hardware efficient utilization of HPC systems and to establish appropriate HPC user support structures. A special focus was put on HPC centers embedded into German universities. The project "Process-oriented Performance Engineering Service Infrastructure for Scientific Software at German HPC Centres" (ProPE) dealt with this call for proposals in the context of a structured distributed Performance Engineering (PE) initiative involving three established academic HPC centers distributed throughout Germany: ITC Aachen, ZIH Dresden and Regional Computer Center Erlangen. The aim of the project was to evaluate and implement common processes, methods and tools to create a blueprint for a nationwide PE infrastructure in which distributed HPC expertise can be used transparently.

The three ProPE partners have long provided the HPC support services described above and have continuously participated in HPC training activities. They are strongly embedded in different application communities and pursue complementary HPC research directions. As they are spread over three states, they also represent different approaches of nationwide coordination structures in HPC, which also need to be integrated into a national PE infrastructure.

This white paper summarizes central methods, processes and tools for distributed PE that were developed and implemented within the ProPE project. It also provides experience in the process of building the distributed infrastructure and identifies infrastructures, processes and data/documentation formats that need to be centrally maintained. The project also emphasizes the need to share structured and appropriate performance engineering approaches, clearly defined IT service processes and documentation, and reliable and robust tools. We first identify the requirements for a distributed PE support infrastructure (see Chapter 3), which components are necessary and how these components could be implemented (see Chapter 4). The paper concludes with a management summary (see Chapter 5).

<sup>&</sup>lt;sup>1</sup>https://www.dfg.de/foerderung/info\_wissenschaft/2015/info\_wissenschaft\_15\_75/index.html

## **Chapter 2**

# **Current status of German HPC landscape**

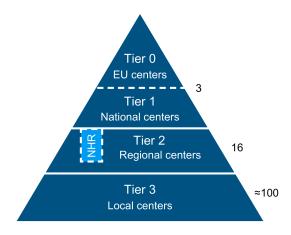

The landscape of HPC centers in Germany is organized as a pyramid following the recommendations of the German Council of Science and Humanities <sup>1</sup> (Wissenschaftsrat, WR) [13]. It covers basically three tiers of HPC capacity/capability systems matching the user range to be served (national/european, regional, local) comprising centers of different sizes (see Figure 2.1 for the current state of the pyramid). The high-end demand on European and national (**Tier-0/1**) level is served by the three **Gauss Center for Supercomputing** (GCS) members HLRS (Stuttgart), LRZ (Garching) and JSC (Jülich). A sustainable funding stream for GCS has been established by the federal government and the hosting states covering full costs of operation including investments, personnel and energy costs. The centers offer complementing application support teams but have no overarching user support structures.

Figure 2.1: HPC pyramid characterizing the HPC landscape in Germany.

At the **Tier-2 level** there is a broad range of mid-sized HPC centers mostly at academic sites and centers serving dedicated user communities (e.g. German Climate Computing Center) or user societies (e.g. Max Planck Computing and Data Facility). Though, Tier-2 academic sites should serve users on a regional scale, funding has been highly local as only 50 % of the investment costs have been funded through DFG while all other costs had to be covered by local authorities. The only cross-state organizational body at Tier-2 is the North German Supercomputing Alliance (**HLRN**) founded in 2001 with 7 member states in northern Germany. Besides the joint funding for two Tier-2 centers (ZIB Berlin and GWDG Göttingen), HLRN also offers dedicated user support personnel in all member states. A nation-wide effort to coordinate HPC centers across the Tiers and to promote HPC as a strategic research activity is the **Gauss-Allianz e.V.**<sup>2</sup> (GA), which is a non-profit organisation. All Tier-2 centers, several Tier-3 sites and the GCS hold a GA membership. The GA aims

<sup>&</sup>lt;sup>1</sup>http://www.wissenschaftsrat.de/en/about.html

<sup>&</sup>lt;sup>2</sup>https://gauss-allianz.de

to improve the national and international visibility of German HPC research efforts, accomplishes scientific events, consults decision makers and provides recommendations concerning national HPC infrastructures. Its web page is a central hub that provides information about BMBF and DFG funded HPC programs (e.g. the DFG call under which ProPE project has been funded) and projects, and presents all membership centers in a coherent way. The annual GA HPC status conference offers a platform to present results from BMBF and DFG funded HPC research projects and discuss new HPC developments. Complementing the GA activities, the ZKI AK Supercomputing <sup>3</sup> is an interest group that primarily provides a platform for exchange of knowledge and experiences between HPC centers across all Tiers aiming mostly at operational and administrative issues. It organizes two annual meetings at member sites.

In addition some states have established state-wide HPC competence or coordination networks: bwHPC in Baden-Würtemberg<sup>4</sup>, HKHLR in Hessen<sup>5</sup>, KONWIHR in Bavaria<sup>6</sup>, and most recently HPC.NRW<sup>7</sup> in North-Rhine Westphalia. The scope of these efforts is very different. The **bwHPC** association has dedicated hardware resources, which are distributed across state universities and provides central infrastructures (high speed networks, IDM, documentation platforms) for state-wide access. The involved Tier-2/3 HPC centers focus their efforts on specific application communities. A different approach is implemented by the Bavarian competence network for HPC (**KONWIHR**) which fosters research and software projects for efficient utilization of modern HPC systems for more than two decades. The KONWIHR projects receive dedicated funding and special support from the two leading HPC centers in Bavaria (LRZ Garching and Erlangen Regional Computing Center). The **HPC.NRW** and **HKHLR** offer and coordinate state-wide training activities and foster HPC user support of relevant Tier-2 and Tier-3 centers. Figure 2.2 gives an overview of currently existing HPC federations and the embedding of the ProPE partners.

Figure 2.2: Overview German HPC landscape. Shown are locations of Tier-0/1 and Tier-2 locations. ProPE partners are marked with red dots. The five regional networks are colored.

In April 2015 the German Council of Science and Humanities recommended the implementation and longterm financing of a nationwide coordinated Tier-2 infrastructure for High Performance Computing (Nationales Hoch- und Höchstleistungsrechnen, NHR) at academic institution in Germany [14]. In January 2020 the DFG has issued a call for "Admission of Computing Centres to the **NHR Alliance**" <sup>8</sup> which seeks for "suitable computing centres with complementary profiles". In this context, the "NHR Alliance shall provide resources

<sup>&</sup>lt;sup>3</sup>https://www.zki.de/ueber-den-zki/vereinsstruktur/supercomputing/

<sup>&</sup>lt;sup>4</sup>https://www.bwhpc.de

<sup>&</sup>lt;sup>5</sup>https://www.hkhlr.de

<sup>&</sup>lt;sup>6</sup>https://www.konwihr.de

<sup>&</sup>lt;sup>7</sup>https://hpc.dh.nrw

<sup>&</sup>lt;sup>8</sup>https://www.dfg.de/foerderung/info\_wissenschaft/2020/info\_wissenschaft\_20\_03/index.html

and nationwide services with respect to scientific computing and thus meet the universities' nationwide need for high-performance computing". The program will provide complete funding for each center over a timeframe of 10 years including personnel and operational costs. Centers in the NHR Alliance will not only coordinate their hardware investments but are also expected to collaborate in HPC user support and training and shall promote "trans regional and interdisciplinary collaborations and cooperation". This will allow scientists from all over Germany to access NHR's systems and benefit from the combined know-how of the NHR Alliance in the fields of performance engineering, HPC-applications and numerical methods. A nationwide HPC environment is to be created hosting high-quality HPC systems, distributed HPC know-how and internationally recognized HPC research. The NHR Alliance is expected to start operations in January 2021 with eight to ten NHR centers distributed across Germany.

The funding and operational structures of smaller academic HPC centers and HPC systems at the research group levels (**Tier-3**) will continue. With the strengthening of the academic Tier-2 centers through the NHR program, the NHR centers may act as regional hubs for accessing the NHR resources and providing and distributing advanced HPC expertise into Tier-3 level.

## **Chapter 3**

# **Requirements for a national Performance Engineering infrastructure**

This white paper discusses basic components and central structures of a potential nationwide Performance Engineering (PE) infrastructure at academic HPC centers. The proposed concept aims to leverage distributed HPC expert knowledge to provide high-quality problem-specific user support at all participating centers. A blueprint of this infrastructure has been established across the three participating centers in the ProPE project. These centers can cover many relevant HPC topics: RWTH Aachen focuses on identifying scalability issues and optimizing OpenMP codes, FAU Erlangen is known for its node-level PE activities for CPUs and GPUs, and TU Dresden has a strong focus on I/O optimization and visual performance analysis tools (see B.1 for a comprehensive overview of the competence fields). All centers have a long-standing track record in both daily HPC user support and research contributions in their competence fields. They are furthermore well known for related training and teaching activities.

The term Performance Engineering is often used in HPC for any activity to improve the time to solution for a given code or problem. This includes trial-and-error optimization approaches, where textbook code transformations are tested for improved runtime without gaining a deeper understanding of the underlying performance problems. Performance Engineering as done by the ProPE partners goes substantially beyond this: Performance Engineering is a well-defined, structured process to identify the relevant performance bottlenecks and then derive appropriate code changes or other measures to improve the resource efficiency of programs. Various approaches are available in ProPE to identify the performance bottleneck and understand its implications: threshold analysis, performance patterns and performance models can be used depending on the requirements of the analyzed problem. The profound bottleneck analysis aims for a deeper understanding of the interaction between hardware and software for the application code, solver or kernel operation at hand, and the insights reach beyond the optimization effort for a specific HPC system and parameter setting. The underlying core process of our PE approach consists of three steps: performance measurement and analysis, bottleneck identification (testing thresholds or performance patterns, establishing performance models) and performance optimization. Finally, code optimization in our understanding is any measure to improve time to solution for a given code including code transformations, parallelization, improved compiler settings or optimized execution parameter settings. While our PE approach does not explicitly include algorithmic optimizations, it often provides guidelines about basic features of alternative algorithms to be considered; choosing an algorithm with higher computational intensity is a typical example. As the centers are embedded into an academic environment, researchers from applied math can be involved in a PE case if code optimization did not deliver the required improvements or indicate some potential for choosing alternative algorithms.

An important component of any PE activity is the **identification of (potential) PE cases**. First, these can be triggered **by users or software developers** who have identified a performance problem themselves or require faster time to solution. The users/developers contact the local PE engineers through the established support structures. These PE cases often require in-depth analysis and the users/developers will be strongly involved in the PE activity. The second alternative is the identification of potential performance problems **by active performance monitoring** of the HPC resources. With appropriate monitoring of the hardware utilization in place, the HPC support team can use bottleneck identification procedures from the PE process (thresholds or performance patterns) to pinpoint badly performing applications, e.g. which only a fraction of the allocated nodes or which show very low hardware utilization. Typically most of these severe performance problems can

easily be solved after the performance engineer contacts the user, e.g. by adapting job scripts or choosing better compiler (options). For users with large allocations further in-depth analysis is offered. Please note, that the hardware performance monitoring data should also be made available to the users. This raises the awareness for hardware efficiency and may encourage them to investigate if actual performance behavior is inline with their expectations. Thus, a system-wide, continuous job-specific hardware performance monitoring which provides reliable and relevant utilization metrics (such as main memory bandwidth, FLOP-rates, instruction throughputs, vectorization ratios, IO-rates or communication frequencies/volumes) is a foundation of any PE-oriented user support. Beyond the application of PE for their local users all three centers regularly contribute their PE expertise to research projects often in the context of a co-design approach (e.g. the three centers have been involved in five DFG SPPEXA projects) or within state-wide HPC networks such as KONWHIR (FAU) or HPC.NRW (RWTH).

Setting up a nation-wide PE infrastructure covering all relevant tier-2/3 center faces the challenge of very different PE knowledge levels of the HPC support people involved in this infrastructure as well as the application scientists and code developers accessing this infrastructure. **Knowledge documentation and transfer** as well as **training** of support personnel and users/developers is a central issue to keep the coordination effort between the centers low and minimize the number of PE cases which cannot be resolved locally but have to be escalated to the central infrastructure. To achieve this goal a central documentation platform process needs to be established and a structured nation-wide training program is required that is tailored to user groups, knowledge levels and application domains.

At the start of the ProPE project each participating center has performed such PE activities by local staff (performance engineers) for local users for a long time. Further they had implemented different PE approaches, user support structures, and HPC system environments. The task of the ProPE project was to identify and implement components for a distributed PE infrastructure which integrates existing local support structures and PE expertises into a nation-wide infrastructure while maintaining local administrative structures. Central goals of this infrastructure are continuous knowledge exchange, coordinated knowledge transfer and training, coherent PE processes allowing for an easy transfer of PE cases to remote centers, and a joint job-specific monitoring strategy with a coordinated format to exchange job performance data.

To this end we have identified and implemented the following components:

- A systematic performance engineering process following scientific practices.

- Robust and simple processes that cover the required use cases of a distributed support infrastructure.

- A system-wide **job-specific performance monitoring infrastructure** at each site to identify both pathological jobs and those with high optimization potential.

- A central knowledge base containing documentation of all relevant PE core activities and all required specifications

- A coordinated, distributed training curriculum covering all required areas and target groups

Further, a common classification and nomenclature is required for the following areas:

- Performance metrics: Define common metrics that characterize application performance.

- Job Classes: Group jobs by their performance characteristics and hardware utilization.

- Target groups: Group persons by task and position.

- Knowledge levels: Indicate the degrees of preliminary knowledge.

Above components and requirements are sufficient from a technical point of view. Still from a governance point of view the financial investment of a performance engineering infrastructure has to be justified. The infrastructure and processes used should ideally either provide metrics for increased scientific productivity (e.g. measured in publications made possible by the use of an HPC system) or, with a finer granularity, the ratio of money saved by an activity to the investment consumed by that activity.

## **Chapter 4**

# **Components of a national Performance Engineering infrastructure**

### 4.1 **ProPE Performance Engineering Process**

#### 4.1.1 Iterative scientific process for performance engineering

As discussed in Chapter 2 we consider **Performance Engineering** as a well-defined, structured process to improve the resource efficiency of application programs. The ProPE project offers a generic PE process based on scientific principles (shown in Section 4.1.1), which can be employed in support actions and training activities. This process can be carried out in different levels of detail, and we describe two variants in Sections 4.1.3 and 4.1.4.

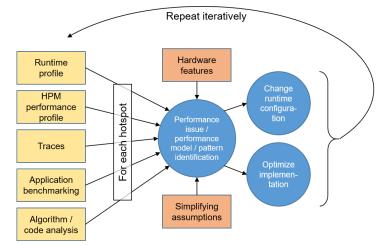

Within the regular support activities, the PE process can be initiated in different ways: (1) detection of performance issues via job-specific performance monitoring, (2) a user's own performance analysis, (3) a user request for more effective use of a resource allotment, or (4) a user request for performance models of their own code in order to get better insight into performance issues. Irrespective of the path that was taken, the PE process follows the cyclic pattern schematically shown in Figure 4.1. Before it can begin, however, it is pivotal to define a relevant test case that allows for quick turnaround time while benchmarking but still reflects production performance behavior. The basic iterative performance engineering procedure requires the following steps:

Acquire a runtime profile to determine which parts of the code require significant time to execute. Even this first step may impose a significant obstacle since the profile of complex applications my be quite "flat," i.e., the runtime may be spread rather evenly across many small loops or routines. Even worse, inlining may distort the view on the profile since hotspot functions can disappear by the compiler inserting their code at the call site. Standard tools may or may not handle this situation gracefully. It is a recom-

Figure 4.1: Simplified overview of the PE process. Note that the construction of a full performance model or the identification of a pattern for each hotspot is optional and also not always possible. For each specific hotspot, the cycle terminates as soon as no relevant performance improvements can be attained any more.

mended practice to endow complex applications with explicit timing functions so that at least a coarse overview is readily available. Note also that the runtime profile for the parallel version of an application may differ significantly from the sequential version because node-level bottlenecks augment the impact of bandwidth-bound code regions in the parallel case.

- 2. For all parts of the code that consume a significant fraction of the total runtime (hot spots), a **performance analysis** must be done. The level of detail may vary here since there is a wide spectrum of possible performance issues, not all of which require all the data to be addressed. In the following we list the possible components of the analysis step and comment on their applicability and utility:

- *Static code analysis.* This step concentrates on the high-level aspects of the code. It tries to answer questions like "Which execution resources are needed (data structures, execution units,...)?", "Does the compiler have enough information to produce 'good' assembly?", "Are there any basic problems with data access patterns?", etc. While it usually starts with the high-level language, later passes of the PE cycle may consider assembly code as well. Note that the data acquired here does not require to run the code (although the questions addressed can certainly be motivated by results from the steps below).

- *Application benchmarking.* A single performance or runtime measurement per hotspot is rarely sufficient to acquire all data necessary to form a solid hypothesis about performance issues. Data about the behavior with changing runtime parameters such as number of cores, threads, and processes, thread-core affinity, problem size, problem geometry, etc., may be pivotal to understand performance issues like bandwidth limitations, cache reuse, and communication overhead. This data is especially well suited for forming first hypotheses about performance patterns (see below). In complex applications it may not be straightforward to investigate the impact of the influence factors separately for each hotspot. Then it can be advisable to extract loops or sub-algorithms into **proxy apps** or **mini-apps**, i.e., small, stand-alone programs that are easier to handle than the full application.

- Acquire and analyze runtime traces. Especially in cases where a significant part of the runtime is not spent in the numerical code but in runtime libraries (such as MPI or OpenMP), the chronology of events is of major interest. There are numerous tracing tools that can visualize the interaction of the user's numerical code with the parallel programming library. Timeline and aggregated views allow quick insights into issues like communication hotspots, load imbalance, and desynchronization.

- *Hardware performance counter profiling*. Hardware events allow for a thorough investigation of bottleneck behavior on the core and node level. Raw counts and derived metrics such as memory and cache bandwidth, load/store to flop ratios, IPC, vectorization type and ratios, etc., can substantiate a hypothesis about a performance issue and underpin or validate a performance model.

One should not fail to mention that an experienced performance engineer might skip one or more of these activities because the available evidence is sufficient to arrive at a solid conclusion.

- 3. Based on the data acquired by above activities and considering the machine properties, a hypothesis about potential performance issues is formed. This hypothesis should be connected with a quantitative performance expectation or even a full-fledged **performance model** (like Roofline or ECM on the node level, or a combination with a communication model in the highly parallel case). **Performance patterns** are a helpful instrument in categorizing performance issues if a quantitative model is not desired or possible (see Section 4.1.4 below). Finally, a restricted set of hardware performance counter data can be used for a **threshold analysis** (see Section 4.1.3).

- 4. The performance expectation, pattern, or threshold analysis points directly to possible optimization actions (e.g., appropriate blocking techniques, parallelization strategy, efficient data layouts, distribution of workload, or changing the runtime configuration). It should be noted that the performance profile can change considerably if hotspot code profits from optimizations.

Regardless of the level of detail, above steps must be repeated several times for all hotspots until a required or sufficient performance level is achieved. This makes it is an *iterative* process, and it is the task of a PE consultant to determine when to stop. The level of detail is adapted to the importance of the project, ranging from drafting simple performance expectations to detailed modeling and optimization. After optimization it must be ensured that the optimized variants (within mini-apps or not) are used in regular production and exhibit the expected efficiency boost.

### 4.1.2 Required skills

Several specific skills and areas of knowledge that are not common among software engineers are required to perform the above iterative process in full detail:

- **Application benchmarking**: This includes defining relevant test cases, ensuring reliable timing and performance measurements, controlling and monitoring thread and data affinity settings, and managing the system options influencing performance (e.g., turbo mode, cache coherence options, and ccNUMA settings).

- **Microbenchmarking**: Microbenchmarking is an indispensable tool in performance engineering and serves a variety of purposes: it provides upper performance limits for various resources (e.g., memory bandwidth), it helps to find performance bugs in architectures (e.g., badly designed cache hierarchies), it can uncover undocumented but relevant processor properties (e.g., non-overlapping caches), and it can quantify the cost of programming model constructs or runtime environments (e.g., OpenMP barrier latency). In the context of PE, microbenchmarking is not a black box but a tool to create insight about hardware-software interaction.

- **Runtime profiling**: This may involve more than just running a profiling tool, since compilers and instrumentation may interact with the profile in unwanted ways. Instead of instrumentation, *sampling* may be a more effective way to obtain this data, but statistical variation has to be kept under control.

- **Performance counter profiling**: A plethora of tools exist that support hardware performance counting, but taking the data in the appropriate way and interpreting the numbers correctly requires considerable experience. Moreover, event counting is sometimes unreliable, e.g., counters may give wrong results, so it is pivotal to be able to separate out nonsensical data.

- **Performance expectation**: If possible, a performance expectation or analytic model is the reliable way to identify optimization strategies. Although some tools exist to aid in the construction of analytic performance models (especially for steady-state loops), there are cases in which such models fail or are just too cumbersome to construct, too complex to set up, or inapplicable because their prerequisites are not met (such as Roofline or ECM if the loop is too short to amortize startup and wind-down latencies). Black-box models (curve fitting, machine learning) may be an alternative in very complex situations and where hidden scalability bugs are suspected. Whatever the approach, performance modeling is a science in itself and not an automatic tool that always gives correct answers. It is thus not an activity that can be carried out by inexperienced support staff.

- **Performance optimizations**: While there are generic optimization techniques such as work reduction, tiling, vectorization, avoiding communication and synchronization, etc., the details and actual implementation are specific to the application. A code optimization that requires significant effort should thus only be done if there is a good indication that it will pay off. Again, this decision requires experience.

In addition to these specific skills, a performance engineer should have knowledge of application algorithms, processor and parallel computer architecture, operating system internals, programming models and their implementation, and the behavior and options of compilers. To make things even more complicated, many of these areas are moving targets where problems depend on the version of the operating system or compiler, not to mention features introduced with new processor architectures. Most of these skills are not part of a standard software engineering curriculum or even a parallel programming course. Therefore continuous training of all participating groups and a shared knowledge base is essential for success.

### 4.1.3 Threshold-based performance analysis

As described above, the analysis of benchmark results and/or hardware performance metrics is a difficult initial step in any PE effort and requires considerable experience. The ProPE threshold-based approach supports a simplified version of the full PE cycle. It is based on work of the EU POP Center of Excellence<sup>1</sup> project, in which the ProPE project partner RWTH is an active member. Together with POP project members the existing approach was improved and extended with an in-depth node-level coverage. It is based on thresholds for easy-to-obtain metrics and is useful for a rough initial performance analysis that is also suitable for beginners. After this first step, a more detailed pattern-based analysis can be employed, if necessary, by experienced developers.

<sup>&</sup>lt;sup>1</sup>https://pop-coe.eu/

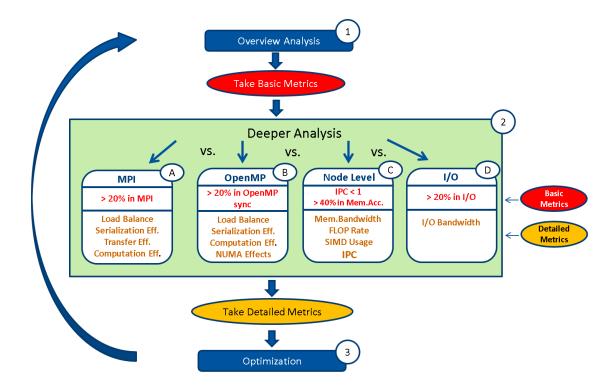

Figure 4.2: Overview of the threshold-based PE process. Initially, four basic metrics are obtained (step 1, indicated in red) and compared to fixed thresholds. If one (or more) of the four thresholds has been exceeded, a set of detailed metrics is acquired, ideally leading to a possible solution of the performance problem.

The threshold-based analysis considers four performance aspects: MPI issues, OpenMP issues, node-level performance, and I/O. See Figure 4.2 for an overview. The process consists of three repetitive steps: Overview analysis, detailed analysis of one of the performance aspects, and optimization of this performance aspect. Each aspect provides a set of additional metrics that can be used to identify and optimize performance issues. Once one of the performance aspects has been optimized, the process is started again from the beginning to focus on optimizing the next performance issue. In the following we describe the three steps in more detail.

#### **Overview analysis**

The first step is to perform a rough performance analysis for all four aspects using lightweight analysis tools such as Intel Application Performance Snapshot (free) or Arm Performance Reports (commercial). Both tools do not require recompilation and linking of the program or special settings of the tool. The tools provide overall metrics like the amount of time spent on MPI operations, OpenMP synchronization, number of instructions executed per cycle, etc. For each metric, a threshold is defined by experts in the relevant HPC area or by the analysis tools themselves. Each metric and its threshold identify a performance bottleneck for the application. This performance aspect should then be analyzed in detail and optimized in the next steps of the process. These are the metrics and their thresholds (letters correspond to the labels in Figure 4.2):

- A. If more than 20% of the CPU time is spent in MPI operations, the communication structure of the code should be analyzed.

- B. If more than 20% of the CPU time was spent in OpenMP synchronization (or, more generally, the OpenMP runtime library), the OpenMP parallelization should be analyzed.

- C. If the number of executed instructions per cycle (IPC) is smaller than 1 or more than 40% of the CPU time is spent in memory accesses, the data access properties of the code at the node level should be analyzed.

- D. If more than 20% of the time was spent in I/O read and write operations, the I/O behavior of the application should be analyzed.

In case more than one threshold is exceeded, the most severe should be handled first.

#### **Deeper Analysis**

The overview analysis identifies a performance aspect that should be analyzed in detail. The detailed threshold analysis requires key metrics to be measured for selected application regions and for the most severely exceeded threshold (A...D above). Appendix A.2 lists the detailed metrics and which thresholds should be observed.

#### 4.1.4 Performance analysis with patterns

The pattern-based approach provides a different angle to performance engineering at an intermediate level which does not reach as deep into the details of hardware-software interaction as the full PE cycle. It was initially presented in 2012 as a basic concept for describing and classifying typical performance motifs [12]. Currently, the available pattern set covers node-level issues only; it can be combined with the threshold analysis for highly parallel cases. The pattern analysis can only be used for a homogeneous ("steady-state") part of the code, usually the innermost loop nests that make up a substantial part of the runtime. This sets it apart from the threshold-based approach, which is used on the whole application or at least on larger parts such as entire solver components.

The process has the same structure as the generic PE process shown in Figure 4.1 but does not usually require to set up a performance model (although this is possible as an extension). Instead, the input data from the first stage (runtime profile, traces, etc.) is used to postulate a **performance pattern** or **motif**, which encapsulates the performance-limiting aspects of hardware-software interaction for the chosen hotspot. In case of doubt, the pattern hypothesis can be **validated** with additional measurements (e.g., more in-depth performance counter analysis or application benchmarking). Finally, with the correct pattern identified, code optimizations can be employed to mitigate the performance problem (if there is any – not all patterns actually point to problems).

| Name                     | Description                                                                                                             |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| ALU Saturation           | performance limitation caused by fully utilizing a functional unit inside a CPU core                                    |  |  |

| Instruction Overhead     | for a piece of high-level code, the compiler outputs excess instructions                                                |  |  |

| Excess data volume       | data is transferred more often than required within the memory hierarchy                                                |  |  |

| Bandwidth Saturation     | performance limitation caused by fully utilizing a shared data path                                                     |  |  |

| Bad data placement       | performance limitation caused by data residing in remote locations with higher access times                             |  |  |

| Load Imbalance           | problem when work is not equally distributed over all processing units                                                  |  |  |

| Synchronization overhead | performance limitation caused by frequent synchronization calls in parallel environ-<br>ments                           |  |  |

| Expensive instructions   | use expensive instructions although there may be cheaper solutions                                                      |  |  |

| Inefficient instructions | usage of one kind of instructions although there exist more effective ones, e.g., scalar vs. vectorized FP instructions |  |  |

A detailed list of performance patterns (extended from the original paper) can be found in the HPC-Wiki Portal<sup>2</sup>. The following table gives an overview of the most important patterns:

Most of these patterns are directly connected to optimization strategies; for instance, if the *ALU Saturation* pattern applies, the only way to improve the performance is to reduce the amount of instructions executed by the bottlenecked execution unit. In case of bandwidth saturation, reducing the amount of data transferred over the data path is paramount.

#### 4.1.5 The Performance Logbook

The documentation of activities, settings, and results is crucial for any performance engineering effort. It helps to keep track of changes, to make deterministic progress, and to decide which steps are up next. In addition, it contributes to the exchange of insights and knowledge and prevents redundant activities for all participants in the application lifecycle. We have created a performance log template that already contains placeholders for all important activities during performance engineering. The logbook consists of a central text document in markdown format, folders for referenced numbers, settings, and results, and everything else that should be tracked during the process. To use a markdown text file ensures that anyone can view and edit the file with a text editor. No special tools or software are required. As a further advantage, github and gitlab automatically

<sup>&</sup>lt;sup>2</sup>https://hpc-wiki.info/hpc/Performance\_Pattern\_List

convert markdown files to HTML and allow editing in the web browser. The inclusion of the performance log in revision control makes it possible to reference both code changes and PE activities that motivate specific code changes.

The logbook is intended for data centers running customer projects, but can be useful for anyone doing a performance project. The logbook comprises a preamble, several analysis sessions, and a summary. Each analysis session consists of one or more benchmarking blocks. There are five pre-configured activities within a benchmarking block:

- Runtime Profile: Create, analyze, and discuss a runtime profile

- Performance Counter Profile: Create, analyze and discuss a performance counter profile of any kind

- Result: Application benchmarking runs

- · Analysis: Compilation of analysis, observations, and further planning based on previous activities

- **Optimization**: Record of attempted performance optimizations (e.g., changing runtime settings or changing the code)

This structure is certainly not cast in stone and can be adapted to the case at hand. It is, however, recommended to keep the overall structure in order to give performance engineers some common ground when collaborating on projects.

The performance log template with examples is available as Open Source on GitHub [5].

#### 4.1.6 File format standards for Job Meta- and Metric-data

A common format for job metadata as well as metric time series data is useful to exchange job data between sites, for research and analysis purposes, and as a robust way for archiving job performance data. We have developed a JSON text file schema for job metadata and metric data. The format also contains basic statistics about jobs and nodes. The file formats are accompanied by a scalable directory hierarchy specification that can accommodate millions of jobs and an SQLite database schema with an access wrapper script. The JSON schema, helper scripts, and documentation is available at GitHub [4].

#### 4.1.7 The broader context of performance engineering

At the beginning of the ProPE project, a focus was put on performance engineering as a part of software development. However, as HPC is on the way to become scientific mainstream, only a minority of all HPC users today are also software developers. Most users employ either *community codes* (e.g., OpenFoam or Gromacs), commercial software, or production-grade applications that were developed at a chair or institute. Therefore, it is not effective to focus on software development only; other areas such as system configuration, execution environments, and workflow management are at least as important to increase the efficient use of the system. The term *performance engineering* should be seen in a much broader context, encompassing all activities that affect the resource efficiency of application programs.

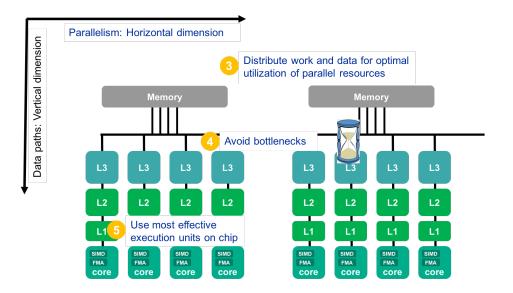

The following influence factors determine the execution efficiency of an application code on an HPC system. We also give some specific examples of aspects to look out for:

- **Choice of algorithm**(**s**): Is the algorithm the best solution to the problem at hand? Aspects: computational complexity, resource complexity, flexibility.

- **Software implementation**: Is the code written in a way that at least allows for efficient execution? Aspects: Data structures, abstractions, parallelization approach, communication strategies.

- Code generation: Does the compiler produce efficient code? Aspects: abstractions, data structures.

- System configuration: Are system tuning knobs exploited that allow for improved application performance? Aspects: clock speed, huge pages, NUMA balancing, Cluster-on-Die/Sub-NUMA Clustering, hardware prefetchers, memory configuration.

- **Execution environment**: Are affinity choices, amount of resources, etc., adapted to the performance properties of the software? Aspects: Pinning, number of threads/processes per contention domain, sub-domain mapping.

A software developer will consider all of these points. Someone who only installs the software focuses on the last two or three points. However, this can make a big difference in performance and also requires the use of performance engineering skills for performance analysis and application benchmarking. After all, an application user only considers the last two or even just the last point. Again, application benchmarking and performance profiling are essential to uncover performance opportunities here. This illustrates the importance of documenting PE activities, insights, and performance results, and sharing this information with all parties involved in the application life cycle.

## 4.2 Establishment of a Distributed Support Infrastructure

The need and desire for excellent science and research is constantly increasing. In an age in which the number of data and their processing are growing ever faster and more complex, appropriate resources and environments are needed to provide science and research with the appropriate infrastructure for calculation. However, the mere provision of resources is not sufficient without the appropriate and competent support from specialists in the system environments.

In order to satisfy the desire for excellent science and research, it is necessary to provide researchers and scientists with the necessary HPC infrastructure. The same applies to competent and specialized support in this field.

To enable efficient high performance computing for more excellent research it is crucial to introduce potential users of different scientific disciplines to the specific systems. Hardware specific surroundings, code optimization and performance engineering are those areas that are important for the implementation and achievement of research goals, especially for scientists in many research areas. A corresponding support infrastructure is therefore necessary as well. The goal is to help users solve problems with competent and specialized support and expertise.

Since the expertise differs in many HPC centres in Germany, competence and expertise oriented support, independent of the users and centres' locations, is of great additional value for science and research. Inquiries therefore do not need to stay unresolved; instead, the targeted use of expertise on remote sites is of great help and use.

The following parts of this white paper describe how the computing centres involved in the ProPE project are structured regarding their level support and how the corresponding expertise at the participating centres is defined. The selected methods as well as the approach of the development of the support infrastructure itself are displayed in the following parts. Focus on these next paragraphs will be laid on the developed supra regional support infrastructure and its processes, which are displayed and elaborated with regards to the process map.

When designing and conceiving a site comprehensive support-service of this quality, it is not only sufficient to make optimum use of the procedural and infrastructural conditions. For this reason, it is also important to meet the needs of the users and to keep the added value for the target group as high as possible. In order to meet these needs sustainably, quantitative surveys have also been designed and developed within the framework of the ProPE project. With the gathering of user feedback, we are aiming to ensure the quality of cross-centre support and to evaluate processes accordingly. In the course of this, the results of a user satisfaction survey enable demand-oriented adaptation and optimization of the support-process in case needs change or comparable.

#### 4.2.1 HPC on Sites

The aim of this work is to develop, describe and establish processes and structures which enable an efficient, sustainable and valuable multi-level user support in the field of HPC, between the participating computing centres. The cross-site support structure of participating HPC centres and experts aims also at an optimum use of resources across sites, both technical and human. The existing local support structures therefore need to be linked together. Here, we describe a regular Tier2-Support-Infrastructure. However, the organization and standardization of the respective support levels poses challenge for the data centers involved, which are not organised in support levels.

#### **First Level Support**

Data centers in this context need to rely on an established first level support and the complementing specialized second levels. These include the HPC second level among all sites, which have been mentioned before. The

customer contact is primarily regulated via the service desks in the first level. There, reaction times are maintained, initial solutions are provided and standard information is obtained from the users for the second level, if necessary. The first level support primarily includes requests relating to access authorizations and login as well as batch submission and availability of resources and status information for the respective systems. The forwarding to the second level HPC support is also carried out by the first levels.

#### Second Level Support

Second level HPC support at data centres for this context needs to consist of specialists in the fields of HPC. The HPC staff may be both local and external employees. The second level is able to answer regular standard HPC service requests and has an advanced HPC knowledge level. In case requests cannot be answered or solved in the second level HPC a third level support is of need. The resident second level categorizes the user request to the third level HPC support. However, this is no longer located on the home site.

#### **Third Level**

Level 3 HPC support (Third Level) in this context consists of both local and external HPC experts. The HPC experts in this particular kind of third level are personnel who support the second level support at the home site, but who step into the third level support function if required. In the ProPE-Project we have tested the supra regional support with three levels to make optimum use of expertise and resources.

#### 4.2.2 HPC Expertise on Sites

In order to establish an expertise-oriented multi-level support structure it is crucial to define expertise and focal points for the precise and efficient processing of customer inquiries. Experts in the context of HPC and in the field of Performance Engineering have different focal points resulting from research, system surroundings or simply competence and knowledge regarding specific aspects in HPC.

Here, we are looking at Performance Engineering experts on three sites. These are local or external domain experts in the field of computational sciences. The supporting experts in the third level are members of the HPC Competence Network and are available to the cooperation partners with their expertise. The data centers with their individual expertise are marked on the HPC landscape and defined as high-level. In the framework of NHR a further concretisation takes place including the creation of centers of excellence.

The ProPE project, serving as example, has in this context developed, tested and established a sustainable cross-site HPC support with three support levels. The three data centers involved, RRZE, RWTH and ZIH, are defined with regard to their respective expertise. In order to provide an insight into the respective expertise, we offer an overview of them in the appendix B.1.

Based on the above mentioned and defined expertise of the participating sites the development of a sustainable and distributed support infrastructure has been developed. The development of the infrastructure aims especially at sustainability and includes the possibility that the concept can be adapted in other support contexts. The following part of this chapter shows an overview of the development of the distributed support infrastructure in the context of the ProPE project.

#### 4.2.3 Development of a Distributed Support Structure

In order to offer a high-quality IT-infrastructure and support, which works efficiently both location-independent and site-wide, not only are the necessary competences indispensable, but above all the organization of such support structures. To provide HPC support across three support levels in three locations or more, processes need to be developed, tested and optimized. In the following section, we focus on the development and the concept for a multi-site support that serves not only users in the fields of research and science but also the national cooperation of university computing and research centers.

To provide a distributed and site-wide support infrastructure with several participating sites, proper and regulated communication between the centers must be ensured. In this context, clear-cut definitions are necessary, which define the extent of responsibilities and work flows for a quality customer support.

#### **The First Test Phase**

In a first phase of testing, an early concept of the support infrastructure has been examined. At its core, the participating sites tried to process customer inquiries across three support levels. It is therefore important that

processes and work flows need to be defined from the beginning to avoid uncoordinated or double communication with support staff and users.

The following section shows in abbreviated form the course of the first test phase, which lays the foundation for the later organized and defined concept of the desired and efficient support process.

For this communication process, e-mail transmission via personal e-mail-accounts was selected and no ticketing tool was used. With the help of voluntary "friendly users", we simulated support requests in order to see how communication and problem solving in the context of PE takes place. It followed the main idea that customer inquiries are processed accordingly to established structures starting on one site, hereinafter referred to as home site. While customer inquiries have been processed accordingly to established structures up to the 2nd-level at the respective computing center, the 2nd-level supporter faced the challenge of getting the cross-site support as 3rd-level involved.

Here we tried to rely on a process that had already proven itself with regard to the external support by the 2nd-level sciebo, which is located in Münster and thus represents an external support level. In this case, the specialist department with its expertise is not located at the home site.

The process provides that requests related to sciebo can be handled to a large extent by the 1st-level support on site. However, in the case of queries that cannot be processed by the 1st-level, these queries, including all standard information, required by the specialist department to process inquiries, need to be forwarded by e-mail to the second level support sciebo. The e-mail, including original inquiry and standard information, is sent to the external second level in Münster from the ticket tool used by the 1st-level on site. This way the processing of the inquiry is sustainably documented and can be used for the further processing by all support staff in the respective support levels. For this purpose, the sciebo support in Münster has its own support e-mail address to which the respective inquiries are sent.

#### **Testing Cross-Location Support**

To start the cross-site support, the 2nd-level of the home site used their local ticket tool to contact the other centers by forwarding the original inquiry. This initial contact of the centers has already depicted an obstacle in terms of communication. Although the 2nd-level supporter of the home site contacted the other HPC specialists, the other 2nd-levels of the remote sites could not be informed about the processing and status of the inquiry. , While one site started to process the inquiry by communicating with the customer by using different communication paths, i.e., various e-mail-addresses and telephone contacts, the other party did not document their progress or findings. This led to the assumption that the inquiry has not been processed for some time. In the meantime, other supporting specialists were dedicated to the customer inquiries. Therefore communication took place via various electronic and telephone routes. This broad variation led to gaps of information and the documentation of those on all sites involved.

The different sites contacted the customer by e-mail as well as by telephone in order to try to process the request and also to gather support-relevant information. Information, which may be necessary for supporters in the 2nd-level of the home site and the supporter functioning as a 3rd-level support for processing the request. Without the documentation of the previous processing steps, the support personnel involved lack knowledge of the processing status. This circumstance has prevented shared access to solutions found on the one hand, but also justifies the need to create structures that gurantee a quality-assured processing of customer inquiries. A further advantage of the documentation of process and work steps is that supporters collect experience through the expertise of colleagues at other locations and thus benefit. In order to share insights and solutions, it is necessary to document processing steps that lead to solutions of the customer concern. This way, the idea came up to use a common ticket tool, which is used by all specialists in the individual 2nd-levels HPC who potentially work on the same requests. In the individual processing steps of the tickets, the solution approaches can be documented and then potentially collected in a common knowledge base to provide edited information in a sustainable manner for support and customers.

The following section shows how we handled the experiences from the first test phase to develop an efficient concept, which has been tested in a second test phase.

#### The Second Test Phase

We mainly test the operationalization of the technical requirements to ensure all comprehensible communication and documentation. The cooperating computing centers face the challenge of how to handle customer inquiries with two ticketing tools. One requirement is that personnel have to transfer inquiries from their local ticketing tool to the one that is centrally provided and serves as communication base. Therefore, one challenge is that personnel involved might have to learn working with the technical aspects of a second ticket tool. Using one common ticketing tool is the quintessential aspect for this concept and serves as the main idea to provide a supra-regional support infrastructure.

This concept also goes hand in hand with the definition of responsibility for the respective origin ticket. For each opened ticket in the common ticket tool, a responsible person must be declared who observes the processing to avoid the following escalation scenarios, which ought to be considered:

- The customer request is not processed. This can be the case for example, due to illness, holidays or insufficient resources.

- A solution to the concern cannot be found; the person in charge has the opportunity to consult another center.

To avoid these scenarios, we have agreed that the responsibility lies within the 2nd-level of the home site. Further agreements for the support process have been found and are presented below as a formal support process. Starting with the common basic requirements, such as the similar support level structure at the cooperating computing centers, to the solution of the request and documentation of the knowledge.

In this course, a completely new concept for the support was developed. The following part shows the developed concept for a distributed support infrastructure and its process map. The formal support process, which embodies the core process of the process map, displays the actual processing of a user request running through all three support levels.

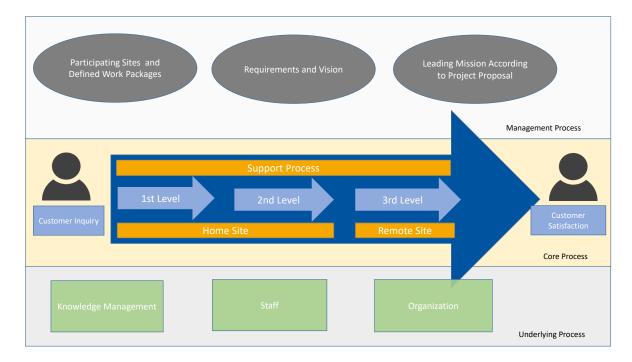

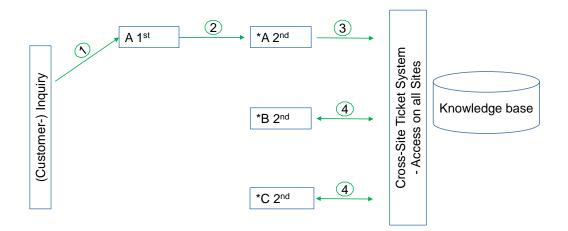

#### 4.2.4 The Process Map for a Multi-Tier Distributed Support Infrastructure

The following process landscape provides a much more detailed look on the several processes, which are involved to sustain and organize an effective customer support across sites. It shows interactions between management, support and customer in an abbreviated, but visualized form. Above all, the workflow illustrates the sequences of events in the process and the superordinate and supporting instances.

A verbalized description of the core process shows in detail the processing flow of a customer inquiry, which is processed by the three support levels.

#### Management Process, Core Process and Underlying Process

Process mapping allows communicating visually interdependences and conditions of important aspects regarding workflows. It provides and spotlights on important details without detailed verbalized descriptions. However, a formalization of the support process itself explains in detail specifications and instructions. The following visualizations provides an understanding of the management process, the core process and the underlying process, which represent interdependences and influences on the anticipated output, the distributed support infrastructure for HPC.

#### **Management Process**

The top layer of the process map depicts the management processes (MP). General functions of the MP are planning, organizing, leading and controlling. In the field of planning and deciding, the course of action is determined. Coordination of activities and resources, such as strategies aiming at visions and requirements. In the ProPE project clear-cut goals regarding determined courses of actions and resources have been made and defined in the existing project proposal by the DFG. It served as a guideline while providing defined goals and tasks during the project and is therefore placed on the level of MP.

The requirements and work status derived from the DFG proposal were discussed at regular conferences and work status was evaluated. Regular exchange talks via telephone conferences and project meetings served to coordinate tasks at the cross-location data centers. Since the entire project has been organized into four work packages, plans and execution of those individual work packages have been discussed in, for example, weekly meetings on site and also with the help of telecommunication or personal meetings across site. A well-organized coordination of individual tasks, responsibilities and communication of results and work statuses is necessary for a project like this.

In conference calls and project meetings off-site goals and decisions are reviewed, staff changes elaborated and responsibilities assigned.

Figure 4.3: Process Landscape for ProPE, shows management, core, and underlying process.

#### **Core Process**

The heart of a process landscape as displayed is the core process itself. In this case it spotlights the support process for the customer support regarding a distributed HPC support with expertise on remote sites. It visualizes the support process across three service levels.

This is illustrated in the process map by showing the different relationships between the support levels and the sites. While the first and second level support are located at the home site, the third level support moves over to the remote site. It is important that the second level of the home sites can take on the function of a third level support at any time, if a customer request exceeds the expertise of the second level and requires the defined competence field of the third level. The aim of the competence-oriented support built up in this way is to offer the users the best possible support. Not only by a specific expert, but also by many experts at the remote sites. The result is the use of existing resources without the limiting factor of the location.

Within the scope of the project, the challenge was on the one hand to use a cross-centre ticket tool and on the other hand to enable customer support in compliance with data protection regulations. Among other features, a common ticket tool offers the possibility to set up a shared ticketing queue to which all agents of the different sites have access. This simplifies the communication and processing of customer requests between the sites as well as the transfer of customer requests from the second to the third level. Therefore, a cross-center ticket instance was necessary for the implementation, which in our case was suspended by the Gauss Alliance. Here, the decision was made in favour of the OTRS ticket system, in which the "Performance Engineering" support queue was set up specifically for this purpose.

Similarly, it is important not only to establish a common and fluid workflow with an appropriate technical realization, but also to comply with data protection agreements. These privacy policies are especially important for the processing of personal data of users, regardless of which organization they belong to.

While first and second level each remaining on the respective home site, the third level interacts across sites. Here all second level agents on the participating sites inhibit the potential function of third level support agents. They enter the third level support function as soon as a support request arrives that matches the defined field of competence. At the latest in the third level, the supporters come into contact with personal data of users of other facilities. This includes not only the personal data, but also, for example, code that is passed on as part of the support request. This content must also be protected and the user must be informed that, in order to solve the request, this information may have to leave the home site and be passed on to third parties for further processing. The core process aims at the satisfaction of the customers whose support requests were made at the home location, whereby all possible resources are used in the network, even with the help of a third level on a remote site.

#### **Underlying Process**

The bottom layer shows the underlying processes, which support the overarching processes. The task of these is to provide the necessary resources for providing the best possible support. Within the framework of the ProPE project, these are the following processes:

**Knowledge Management** Both, workflow and forwarding, of tickets to the home and remote sites are clearly defined by workflows and process documentation. The aim is to maintain a transparent documentation of the ticket forwarding and processing and to ensure that the handling of personal data was in compliance with data protection regulations. Ultimately, the responsibilities have to be clearly defined and thus the quality standards for support have to be maintained even when a request is passed on.

Following the test phase, the satisfaction of the users (here: support agents using OTRS) with regard to the functionality was recorded. Interviews were conducted by support agents and the data was evaluated anonymously. The findings were used to improve support structures for both users and agents. A first finding is that the ticket transfer shows a need for optimization. Especially since the different agents at the sites have to find their way with two different ticketing tools at the same time. The specific guidelines and workflows as well as templates for declarations of consent are documented in a wiki section of the versioning tool GitLab, accessible to all participants. These have proven themselves as necessary for correct ticket processing.

Work steps and solutions are documented in the respective service units of the tickets. These serve as a potential source for subsequent entries into the HPC Wiki, which serves as user documentation. This way a sustainable handling of solutions and findings is ensured.

The next step remains in the establishment of regular in order to gain insights and measure the quality of support with the help of the gathering of user satisfaction.

**Staff** If the aim is to have a support structure based on expertise and competence orientation that functions across centres, it is also necessary to ensure the availability of human resources. In the project described here, there is at least one person at all locations who can assume the function of Third Level Support. In order to maintain accessibility, a deputy should always be sought in order to be able to maintain reaction times and processing times.

All in all, however, the amalgamation of the centres is sufficient to cover the need for support even if there is any doubt that a personnel resource will be unavailable at one location. In the joint network, the core team thus forms the entirety of the second level supporters working at the centers, who can step into the function of the third level.

Absences are regulated in such a way that, if unexpected, the respective team is informed at the home site and, if necessary, measures are taken at the home site. In the case of planned and foreseeable absences, these are communicated to the entire project team. Absences can also be stored in the ticket tool used so that they are transparent and traceable for everyone. Furthermore, at all locations, an absence note is stored in the personal mailbox informing about the foreseeable duration

**Organization** Depending on the site, there are different internal regulations and cycles in which the respective exchange between employees takes place. This often also depends on the size of the team at the home site and the need for exchange. For example, the site-internal meeting cycle can take place weekly. As part of the ProPE project, it has proven helpful for teams from several work packages to exchange information on the respective processing status on a weekly basis.

Nevertheless, it is necessary that both results and upcoming tasks are recorded in meeting minutes, so that they can be accessed if necessary. Decisions can be traced in this way and in case of absences it is possible to inform oneself about the decisions, developments and upcoming as well as to be completed tasks. In the case of the ProPE project, for example, these protocols have proven to be helpful not only in maintaining the level of information, but also in retrospectively evaluating developments and decisions and, if necessary, optimising them. Basically, it is necessary to make protocols available to all participants. We have used the versioning tool GitLab and used the Wiki section to store and make protocols available.

Depending on the amount of support required, the cycle can be adapted as required. For coordination and mutual information in a cross-site context, however, it is advisable to hold telephone conferences at regular intervals. These not only serve to exchange information regarding technical implementations, but also, for example, to ensure the coordination of service requests in the ticket queue.

In order to coordinate the responsibility for the ProPE queue in the Tickettool, a concept for the periodic assignment of responsibility is created in the form of a calendar concept.

The responsibility is planned for the rest of the project duration and the respective schedule in form of a table is also documented in the Wiki section of the GitLab-project and available to all members of the project.

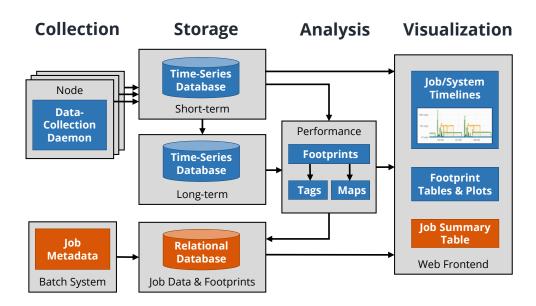

Figure 4.4: Monitoring Infrastructure